Академический Документы

Профессиональный Документы

Культура Документы

Simulink HDL Coder

Загружено:

7788778887Исходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Simulink HDL Coder

Загружено:

7788778887Авторское право:

Доступные форматы

Simulink HDL Coder 2.

1

Generate HDL code from Simulink models and MATLAB code

Introduction Simulink HDL Coder generates bit-true and cycle-accurate, synthesizable Verilog and VHDL code from Simulink models, MATLAB code, and Stateflow charts. The generated HDL code can be simulated and synthesized using industry-standard tools and then implemented on FPGAs and ASICs. With Simulink HDL Coder you can control HDL architecture and implementation, highlight critical paths in the model, and generate hardware resource utilization estimates. For rapid verification, Simulink HDL Coder generates test benches and EDA Simulator Link cosimulation models, and provides code traceability to support the DO-254 workflow. Key Features Generation of target-independent, synthesizable HDL code from Simulink models, MATLAB code, and Stateflow charts Support for Mealy and Moore finite-state machines and control logic implementations Generation of test benches and EDA Simulator Link cosimulation models Resource sharing and subsystem-level retiming options for area-speed tradeoffs Simulink model optimization using timing constraint information and HDL synthesis tools Code-to-model and model-to-code traceability for DO-254 Legacy code integration

Generating HDL code from a Simulink model. Simulink HDL Coder enables you to model your system and then automatically generate bit-true and cycle-accurate synthesizable Verilog and VHDL code and test benches.

Working with Simulink HDL Coder Simulink HDL Coder lets you automate your algorithm design process, from modeling to FPGA and ASIC implementation, with these steps:

Model your system using Simulink, MATLAB code, and Stateflow charts Configure parameters to select different HDL block implementations Optimize models to meet area-speed design objectives Generate HDL code using the HDL Workflow Advisor or the Configuration Parameters GUI Verify generated code using test benches and automatically generated cosimulation models You start the HDL code generation process by first modeling your algorithm in Simulink, MATLAB, or Stateflow. You can select from more than 160 Simulink blocks from add-on products for signal processing and communications to model your algorithm. For example, you can use the Viterbi decoder or Reed-Solomon decoder to model communications receivers and generate HDL code. Similarly, you can use signal processing FFT function and filtering algorithms, including CIC and FIR interpolation and decimation filters. You can generate HDL code from your MATLAB code by using the MATLAB function block in Simulink. Simulink HDL Coder provides a library of common and ready-to-use logic elements, such as counters and timers that are written in MATLAB code. You can also model your finite-state machine (FSM) in Stateflow and integrate your handwritten or legacy HDL code into the Simulink model via black-box interfaces. Once you have created your model, you can use the HDL Workflow Advisor or the Configuration Parameters GUI to apply code generation constraints and generate HDL code.

Configuration Parameters GUI for setting code generation options and generating Verilog and VHDL code.

Simulink HDL Coder works with EDA Simulator Link to perform FPGA-in-the-loop (FIL) simulations and HDL cosimulations. In addition, you can generate HDL test benches and script files for standalone verification in your HDL simulation environment.

Optimizing Design

Resource utilization report for performing area-speed tradeoffs.

Simulink HDL Coder lets you control the architecture of the HDL code at a block and subsystem level in your model. For example, you can employ distributed pipelining, streaming, and resource sharing for subsystems, Stateflow charts, and MATLAB function blocks, to achieve speed-area tradeoffs in your FPGA and ASIC implementations. You can also implement multichannel designs and serialization techniques that are commonly used in signal processing and multimedia applications.

Resource-optimization example. Replacing four multipliers with one multiplier reduces the design area at the cost of increasing the data rate by a factor of four.

Documenting and Tracing Code Simulink HDL Coder helps you verify your generated code with: User-controlled comments and descriptions to improve code readability Model-to-code and code-to-model traceability

Support for including requirements in the generated code, enabling DO-254 compliance

Model-to-code and code-to-model traceability. Simulink HDL Coder facilitates DO-254 compliance and design verification and validation.

Simulink HDL Coder documents the generated code in an HTML report that comprehensively describes the code modules and model optimization settings applied during HDL code generation. The report includes a summary section and a table of generated source files that are linked to your Simulink model. Selecting a source file in the MATLAB Help browser highlights the corresponding block in your model, making the code easy to trace and review. You can also highlight HDL code from Simulink blocks, Stateflow transitions and states, and MATLAB for bidirectional tracing. When used with Simulink Verification and Validation, Simulink HDL Coder can embed system requirements within HDL code as comments. As a result, you can achieve complete transparency throughout the entire workflow, from system requirements to implemented HDL code. Cosimulation and Test-Bench Generation Simulink HDL Coder generates VHDL and Verilog test benches to enable rapid verification of the generated HDL code. You can customize an HDL test bench using a variety of options that apply stimuli to the HDL code. You can also generate script files to automate the process of compiling and simulating your code in HDL simulators. Simulink HDL Coder works with EDA Simulator Link to generate a cosimulation model. The automatically generated model is configured for both Simulink simulation and cosimulation with an HDL simulator, such as Cadence Incisive or Mentor Graphics ModelSim and Questa. You can also use the generated model to perform FPGA-in-the-loop simulations.

Automatic instantiation of cosimulation model (bottom, left) and generation of HDL test bench (top, right) using Simulink HDL Coder.

Automating FPGA Design

FPGA design workflow with Simulink HDL Coder. The HDL Workflow Advisor works with third-party synthesis tools, such as Xilinx ISE and Altera Quartus II, for rapid design iterations.

Simulink HDL Coder enables you to quickly implement your Simulink model in Xilinx and Altera FPGAs. The HDL Workflow Advisor supports and integrates all stages of the FPGA design process, including: Checking the Simulink model for HDL code generation compatibility Generating RTL code, an RTL test bench, and a cosimulation model Performing synthesis and timing analysis through integration with Xilinx ISE and Altera Quartus II Providing a resource estimation report and guidance on modifying the model to achieve design constraints Back annotating the Simulink model with critical path information

HDL Workflow Advisor, which supports all stages of the FPGA design process from within Simulink.

You can view a postsynthesis timing report and back annotate the Simulink model to identify timing-constraint bottlenecks. Such integration with synthesis tools provides for rapid design iterations and significantly reduces FPGA design cycle time.

Critical path highlighting of presynthesis and postsynthesis timing information in Simulink. You can quickly iterate on your design to eliminate timing-constraint bottlenecks.

Simulink HDL Coder generates HDL code that is readable, target-independent, and supports legacy code integration. As a result, you can quickly transition between FPGA and ASIC implementations based on your design requirements.

Resources

Product Details, Demos, and System Requirements www.mathworks.com/products/slhdlcoder Trial Software www.mathworks.com/trialrequest Sales www.mathworks.com/contactsales Technical Support www.mathworks.com/support Online User Community www.mathworks.com/matlabcentral Training Services www.mathworks.com/training Third-Party Products and Services www.mathworks.com/connections Worldwide Contacts www.mathworks.com/contact

2011 The MathWorks, Inc. MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Object Oriented Analysis and Design 3 0 0 3 ObjectiveДокумент2 страницыObject Oriented Analysis and Design 3 0 0 3 Objectiveryu447Оценок пока нет

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- BACnet (Honeywell) PDFДокумент77 страницBACnet (Honeywell) PDFRaviОценок пока нет

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Microsoft Word - Deployment Diagram - An - An IntroductionДокумент6 страницMicrosoft Word - Deployment Diagram - An - An IntroductionChandra MohanОценок пока нет

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- Devtools CheatsheetДокумент2 страницыDevtools CheatsheetMiguel Hinojosa100% (1)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- Bachelor of Computer Applications (BCA) : Institute of Management StudiesДокумент24 страницыBachelor of Computer Applications (BCA) : Institute of Management StudiesgauravjainisОценок пока нет

- ICSE Questions On Functions1Документ12 страницICSE Questions On Functions1Harsh100% (1)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Chapter 1. Getting Started: Copying The Northwind Sample DatabaseДокумент10 страницChapter 1. Getting Started: Copying The Northwind Sample DatabasegosmileyОценок пока нет

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- Web SpoofingДокумент13 страницWeb SpoofingSanjeev MauryaОценок пока нет

- Oracle Install GuideДокумент8 страницOracle Install GuideSallyОценок пока нет

- Neural NetworksДокумент38 страницNeural Networkstt_aljobory3911Оценок пока нет

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- 01 Laboratory Exercise 1.IAДокумент9 страниц01 Laboratory Exercise 1.IAMelchie RepospoloОценок пока нет

- Keyboard ShortcutsДокумент28 страницKeyboard Shortcuts74831Оценок пока нет

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- Fourth Order Runge-Kutta-Step-By-Step PDFДокумент12 страницFourth Order Runge-Kutta-Step-By-Step PDFMetinОценок пока нет

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- Scloader 2 BДокумент4 страницыScloader 2 BLeo MagnoОценок пока нет

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Interpolare LagrangeДокумент9 страницInterpolare Lagrangedragos_bogdan1974Оценок пока нет

- Factorial of A Number Using RecursionДокумент5 страницFactorial of A Number Using RecursionPriyanshu JainОценок пока нет

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- Poradnik Mechanika - REAДокумент215 страницPoradnik Mechanika - REAAndrzej100% (1)

- Chapter 1: Introduction: ©silberschatz, Korth and Sudarshan 1.1 Database System ConceptsДокумент21 страницаChapter 1: Introduction: ©silberschatz, Korth and Sudarshan 1.1 Database System ConceptsvarshapadiharОценок пока нет

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

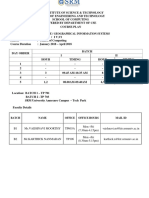

- B.tech 15CS329E Geographical Information SystemsДокумент5 страницB.tech 15CS329E Geographical Information SystemsRajalearn2 Ramlearn2Оценок пока нет

- Lecture 8.1 - 2-Introduction To Zero-Sum GamesДокумент19 страницLecture 8.1 - 2-Introduction To Zero-Sum GamesAna FloreaОценок пока нет

- Data Science & Machine Learning by Using R ProgrammingДокумент6 страницData Science & Machine Learning by Using R ProgrammingVikram SinghОценок пока нет

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Infosphere Information Server InstallationДокумент7 страницInfosphere Information Server InstallationsrimkbОценок пока нет

- Final ProjectДокумент11 страницFinal Projectapi-374891391Оценок пока нет

- LCD PPTДокумент41 страницаLCD PPTSneh Srijan100% (1)

- TMN ArchitectureДокумент4 страницыTMN ArchitectureNitu Jha SaksenaОценок пока нет

- Planning and Implementing Vlans With Hp-Ux: HP Part Number: 5992-0538 Published: March 2007Документ18 страницPlanning and Implementing Vlans With Hp-Ux: HP Part Number: 5992-0538 Published: March 2007Thi HaОценок пока нет

- Sample Project DocumentationДокумент20 страницSample Project DocumentationZakiОценок пока нет

- Riyaj Cost Based Query TransformationДокумент49 страницRiyaj Cost Based Query TransformationNaresh KumarОценок пока нет

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- COMP3121 2 Basic Tools For Analysis of AlgorithmsДокумент23 страницыCOMP3121 2 Basic Tools For Analysis of Algorithmsriders29Оценок пока нет

- Embedded Real Time SystemДокумент12 страницEmbedded Real Time SystemKottai eswariОценок пока нет