Академический Документы

Профессиональный Документы

Культура Документы

N-Channel Trenchmos Transistor Irf540, Irf540S: Features Symbol Quick Reference Data

Загружено:

thedrodИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

N-Channel Trenchmos Transistor Irf540, Irf540S: Features Symbol Quick Reference Data

Загружено:

thedrodАвторское право:

Доступные форматы

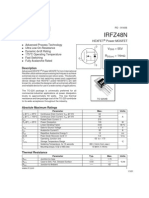

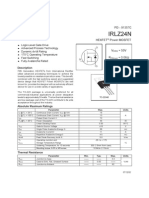

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF540, IRF540S

FEATURES

Trench technology Low on-state resistance Fast switching Low thermal resistance

SYMBOL

d

QUICK REFERENCE DATA VDSS = 100 V ID = 23 A

g

RDS(ON) 77 m

s

GENERAL DESCRIPTION

N-channel enhancement mode field-effect power transistor in a plastic envelope using trench technology. Applications: d.c. to d.c. converters switched mode power supplies T.V. and computer monitor power supplies The IRF540 is supplied in the SOT78 (TO220AB) conventional leaded package. The IRF540S is supplied in the SOT404 (D2PAK) surface mounting package.

PINNING

PIN 1 2 3 tab gate drain1 source drain DESCRIPTION

SOT78 (TO220AB)

tab

SOT404 (D2PAK)

tab

2

1 23

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134) SYMBOL PARAMETER VDSS VDGR VGS ID IDM PD Tj, Tstg Drain-source voltage Drain-gate voltage Gate-source voltage Continuous drain current Pulsed drain current Total power dissipation Operating junction and storage temperature CONDITIONS Tj = 25 C to 175C Tj = 25 C to 175C; RGS = 20 k Tmb = 25 C; VGS = 10 V Tmb = 100 C; VGS = 10 V Tmb = 25 C Tmb = 25 C MIN. - 55 MAX. 100 100 20 23 16 92 100 175 UNIT V V V A A A W C

1 It is not possible to make connection to pin:2 of the SOT404 package August 1999 1 Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF540, IRF540S

AVALANCHE ENERGY LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134) SYMBOL PARAMETER EAS Non-repetitive avalanche energy Peak non-repetitive avalanche current CONDITIONS Unclamped inductive load, IAS = 10 A; tp = 350 s; Tj prior to avalanche = 25C; VDD 25 V; RGS = 50 ; VGS = 10 V; refer to fig:14 MIN. MAX. 230 UNIT mJ

IAS

23

THERMAL RESISTANCES

SYMBOL PARAMETER Rth j-mb Rth j-a Thermal resistance junction to mounting base Thermal resistance junction to ambient CONDITIONS MIN. SOT78 package, in free air SOT404 package, pcb mounted, minimum footprint TYP. MAX. UNIT 60 50 1.5 K/W K/W K/W

ELECTRICAL CHARACTERISTICS

Tj= 25C unless otherwise specified SYMBOL PARAMETER V(BR)DSS VGS(TO) RDS(ON) gfs IGSS IDSS Qg(tot) Qgs Qgd td on tr td off tf Ld Ld Ls Ciss Coss Crss Drain-source breakdown voltage Gate threshold voltage Drain-source on-state resistance Forward transconductance Gate source leakage current Zero gate voltage drain current Total gate charge Gate-source charge Gate-drain (Miller) charge Turn-on delay time Turn-on rise time Turn-off delay time Turn-off fall time Internal drain inductance Internal drain inductance Internal source inductance Input capacitance Output capacitance Feedback capacitance CONDITIONS VGS = 0 V; ID = 0.25 mA; Tj = -55C VDS = VGS; ID = 1 mA Tj = 175C Tj = -55C VGS = 10 V; ID = 17 A Tj = 175C VDS = 25 V; ID = 17 A VGS = 20 V; VDS = 0 V VDS = 100 V; VGS = 0 V VDS = 80 V; VGS = 0 V; Tj = 175C ID = 17 A; VDD = 80 V; VGS = 10 V MIN. 100 89 2 1 8.7 TYP. MAX. UNIT 3 49 132 15.5 10 0.05 8 39 26 24 3.5 4.5 7.5 890 139 83 4 6 77 193 100 10 250 65 10 29 1187 167 109 V V V V V m m S nA A A nC nC nC ns ns ns ns nH nH nH pF pF pF

VDD = 50 V; RD = 2.2 ; VGS = 10 V; RG = 5.6 Resistive load Measured tab to centre of die Measured from drain lead to centre of die (SOT78 package only) Measured from source lead to source bond pad VGS = 0 V; VDS = 25 V; f = 1 MHz

August 1999

Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF540, IRF540S

REVERSE DIODE LIMITING VALUES AND CHARACTERISTICS

Tj = 25C unless otherwise specified SYMBOL PARAMETER IS ISM VSD trr Qrr Continuous source current (body diode) Pulsed source current (body diode) Diode forward voltage Reverse recovery time Reverse recovery charge CONDITIONS MIN. IF = 28 A; VGS = 0 V IF = 17 A; -dIF/dt = 100 A/s; VGS = 0 V; VR = 25 V TYP. MAX. UNIT 0.94 61 200 23 92 1.5 A A V ns nC

August 1999

Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF540, IRF540S

Normalised Power Derating, PD (%) 100 90 80 70 60 50 40 30 20 10 0 0 25 50 75 100 125 Mounting Base temperature, Tmb (C) 150 175

10

Transient thermal impedance, Zth j-mb (K/W)

D = 0.5 0.2 0.1 0.05 0.02 single pulse T 1E-04 1E-03 1E-02 1E-01 1E+00 P D

0.1

tp

D = tp/T

0.01 1E-06

1E-05

Pulse width, tp (s)

Fig.1. Normalised power dissipation. PD% = 100PD/PD 25 C = f(Tmb)

Fig.4. Transient thermal impedance. Zth j-mb = f(t); parameter D = tp/T

Drain Current, ID (A)

9V 8V 7V

Normalised Current Derating, ID (%) 100 90 80 70 60 50 40 30 20 10 0 0 25 50 75 100 125 Mounting Base temperature, Tmb (C) 150 175

55 50 45 40 35 30 25 20 15 10 5 0 0

6V

5V 4V 1 2 3 4 5 6 7 8 9 10

Drain-Source Voltage, VDS (V)

Fig.2. Normalised continuous drain current. ID% = 100ID/ID 25 C = f(Tmb); conditions: VGS 10 V

Peak Pulsed Drain Current, IDM (A)

Fig.5. Typical output characteristics, Tj = 25 C. ID = f(VDS)

Drain-Source On Resistance, RDS(on) (Ohms) 0.8 0.7

1000

100

RDS(on) = VDS/ ID tp = 10 us

0.6 0.5 4V 0.4 0.3 5V 0.2 0.1 VGS =9 V 5.5V 6V 6.5V 7V 8V

10 D.C. 1

100 us 1 ms 10 ms 100 ms

0.1 1 10 100 Drain-Source Voltage, VDS (V) 1000

0 0 10 20 30 Drain Current, ID (A) 40 50

Fig.3. Safe operating area. Tmb = 25 C ID & IDM = f(VDS); IDM single pulse; parameter tp

Fig.6. Typical on-state resistance, Tj = 25 C. RDS(ON) = f(ID)

August 1999

Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF540, IRF540S

Drain current, ID (A) 30 28 26 24 22 20 18 16 14 12 10 8 6 4 2 0 0 VDS > ID X RDS(ON)

4.5 4 3.5 3 2.5 2 175 C Tj = 25 C 1.5 1 0.5 0

Threshold Voltage, VGS(TO) (V) maximum typical

minimum

10

-60

-40

-20

20

40

60

80

100 120 140 160 180

Gate-source voltage, VGS (V)

Junction Temperature, Tj (C)

Fig.7. Typical transfer characteristics. ID = f(VGS)

Transconductance, gfs (S) VDS > ID X RDS(ON) Tj = 25 C 175 C

Fig.10. Gate threshold voltage. VGS(TO) = f(Tj); conditions: ID = 1 mA; VDS = VGS

Drain current, ID (A)

20 18 16 14 12 10 8 6 4 2 0

1.0E-01

1.0E-02 minimum typical 1.0E-04 maximum 1.0E-05

1.0E-03

1.0E-06 0 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 Drain current, ID (A) 0 0.5 1 1.5 2 2.5 3 3.5 Gate-source voltage, VGS (V) 4 4.5 5

Fig.8. Typical transconductance, Tj = 25 C. gfs = f(ID)

Normalised On-state Resistance 2.9 2.7 2.5 2.3 2.1 1.9 1.7 1.5 1.3 1.1 0.9 0.7 0.5 -60 -40 -20 0 20 40 60 80 100 120 140 160 180 Junction temperature, Tj (C)

Fig.11. Sub-threshold drain current. ID = f(VGS); conditions: Tj = 25 C; VDS = VGS

Capacitances, Ciss, Coss, Crss (pF) 10000

Ciss 1000

Coss 100

Crss 10 0.1 1 10 Drain-Source Voltage, VDS (V) 100

Fig.9. Normalised drain-source on-state resistance. RDS(ON)/RDS(ON)25 C = f(Tj)

Fig.12. Typical capacitances, Ciss, Coss, Crss. C = f(VDS); conditions: VGS = 0 V; f = 1 MHz

August 1999

Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF540, IRF540S

Source-Drain Diode Current, IF (A) 30 28 26 24 22 20 18 16 14 12 10 8 6 4 2 0 0

100

Maximum Avalanche Current, IAS (A)

VGS = 0 V

175 C Tj = 25 C

10

25 C

Tj prior to avalanche = 150 C 1

0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9

1.1 1.2 1.3 1.4 1.5

0.1 0.001

0.01

0.1 Avalanche time, tAV (ms)

10

Source-Drain Voltage, VSDS (V)

Fig.13. Typical reverse diode current. IF = f(VSDS); conditions: VGS = 0 V; parameter Tj

Fig.14. Maximum permissible non-repetitive avalanche current (IAS) versus avalanche time (tAV); unclamped inductive load

August 1999

Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF540, IRF540S

MECHANICAL DATA

Plastic single-ended package; heatsink mounted; 1 mounting hole; 3-lead TO-220 SOT78

E P

A A1 q

D1

L2(1)

L1 Q

b1

3

b c

5 scale

10 mm

DIMENSIONS (mm are the original dimensions) UNIT mm A 4.5 4.1 A1 1.39 1.27 b 0.9 0.7 b1 1.3 1.0 c 0.7 0.4 D 15.8 15.2 D1 6.4 5.9 E 10.3 9.7 e 2.54 L 15.0 13.5 L1 3.30 2.79 L2 max. 3.0

(1)

P 3.8 3.6

q 3.0 2.7

Q 2.6 2.2

Note 1. Terminals in this zone are not tinned. OUTLINE VERSION SOT78 REFERENCES IEC JEDEC TO-220 EIAJ EUROPEAN PROJECTION ISSUE DATE 97-06-11

Fig.15. SOT78 (TO220AB); pin 2 connected to mounting base (Net mass:2g)

Notes 1. This product is supplied in anti-static packaging. The gate-source input must be protected against static discharge during transport or handling. 2. Refer to mounting instructions for SOT78 (TO220AB) package. 3. Epoxy meets UL94 V0 at 1/8".

August 1999

Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF540, IRF540S

MECHANICAL DATA

Plastic single-ended surface mounted package (Philips version of D2-PAK); 3 leads (one lead cropped) SOT404

A E A1 mounting base

D1

HD

2

Lp

3

b c Q

2.5 scale

5 mm

DIMENSIONS (mm are the original dimensions) UNIT mm A 4.50 4.10 A1 1.40 1.27 b 0.85 0.60 c 0.64 0.46 D max. 11 D1 1.60 1.20 E 10.30 9.70 e 2.54 Lp 2.90 2.10 HD 15.40 14.80 Q 2.60 2.20

OUTLINE VERSION SOT404

REFERENCES IEC JEDEC EIAJ

EUROPEAN PROJECTION

ISSUE DATE 98-12-14 99-06-25

Fig.16. SOT404 surface mounting package. Centre pin connected to mounting base.

Notes 1. This product is supplied in anti-static packaging. The gate-source input must be protected against static discharge during transport or handling. 2. Refer to SMD Footprint Design and Soldering Guidelines, Data Handbook SC18. 3. Epoxy meets UL94 V0 at 1/8".

August 1999

Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF540, IRF540S

MOUNTING INSTRUCTIONS

Dimensions in mm

11.5

9.0

17.5 2.0

3.8

5.08

Fig.17. SOT404 : soldering pattern for surface mounting.

DEFINITIONS

Data sheet status Objective specification Product specification Limiting values Limiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of this specification is not implied. Exposure to limiting values for extended periods may affect device reliability. Application information Where application information is given, it is advisory and does not form part of the specification. Philips Electronics N.V. 1999 All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, it is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights. This data sheet contains target or goal specifications for product development. This data sheet contains final product specifications. Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

August 1999

Rev 1.100

This datasheet has been download from: www.datasheetcatalog.com Datasheets for electronics components.

Вам также может понравиться

- N-Channel Trenchmos Transistor Irf630, Irf630S: Features Symbol Quick Reference DataДокумент9 страницN-Channel Trenchmos Transistor Irf630, Irf630S: Features Symbol Quick Reference Datalord mace tyrellОценок пока нет

- Dual N-Channel Enhancement Mode Phn210T Trenchmos TransistorДокумент8 страницDual N-Channel Enhancement Mode Phn210T Trenchmos TransistorCristian ViolaОценок пока нет

- Fdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MДокумент11 страницFdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MKevin TateОценок пока нет

- IRF650B / IRFS650B: 200V N-Channel MOSFETДокумент10 страницIRF650B / IRFS650B: 200V N-Channel MOSFETbinoelОценок пока нет

- Irfp 260 NДокумент9 страницIrfp 260 NJolaine MojicaОценок пока нет

- N-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Документ11 страницN-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Kevin TateОценок пока нет

- BUK7511-55A BUK7611-55A: 1. DescriptionДокумент15 страницBUK7511-55A BUK7611-55A: 1. DescriptionziminautaОценок пока нет

- N-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataДокумент9 страницN-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataroozbehxoxОценок пока нет

- FQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETДокумент9 страницFQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETsoweloОценок пока нет

- PHB 55n03lta Logic Level FetДокумент15 страницPHB 55n03lta Logic Level FetyusufwpОценок пока нет

- IRF740B/IRFS740B: 400V N-Channel MOSFETДокумент11 страницIRF740B/IRFS740B: 400V N-Channel MOSFETMistery of the souldОценок пока нет

- Description: N-Channel Enhancement Mode Field-Effect TransistorДокумент14 страницDescription: N-Channel Enhancement Mode Field-Effect TransistorFernando Gonzales SanchezОценок пока нет

- IRFP360LCДокумент8 страницIRFP360LCΗρακλης ΖερκελιδηςОценок пока нет

- IRF650B / IRFS650B: 200V N-Channel MOSFETДокумент11 страницIRF650B / IRFS650B: 200V N-Channel MOSFETMiloud ChouguiОценок пока нет

- Irl 1004Документ9 страницIrl 1004Luiz RvОценок пока нет

- IRFZ48NДокумент8 страницIRFZ48NLuay IssaОценок пока нет

- Irfz 34 NLДокумент10 страницIrfz 34 NLguerrero_27Оценок пока нет

- Irf740b PDFДокумент10 страницIrf740b PDFMed SamiОценок пока нет

- Irfi 3205 Power MosfetДокумент9 страницIrfi 3205 Power MosfetAndy WilsonОценок пока нет

- Irf7811Avpbf Irf7811Avpbf: Absolute Maximum RatingsДокумент6 страницIrf7811Avpbf Irf7811Avpbf: Absolute Maximum RatingsnewmailsОценок пока нет

- Irfz46n PDFДокумент9 страницIrfz46n PDFYunier FernandezОценок пока нет

- IRF540NДокумент7 страницIRF540Nmichaelliu123456Оценок пока нет

- IRF8788Документ9 страницIRF8788Robert KovacsОценок пока нет

- Irfz 48 VДокумент8 страницIrfz 48 VZoltán HalászОценок пока нет

- N 308 ApДокумент11 страницN 308 Apdragon-red0816Оценок пока нет

- IRFZ48 55V-64A 140W-N-channelenhancemenT PDFДокумент8 страницIRFZ48 55V-64A 140W-N-channelenhancemenT PDFZxdIaminxXzlovewithzxXzyouzxОценок пока нет

- Irfp 140 NДокумент9 страницIrfp 140 NCodinasound CaОценок пока нет

- FDP 8896Документ11 страницFDP 8896condejhonnyОценок пока нет

- CD22100 - DataSheetДокумент10 страницCD22100 - DataSheetHao ChungОценок пока нет

- BUK951R6-30E: 1. Product ProfileДокумент13 страницBUK951R6-30E: 1. Product ProfileTom BeanОценок пока нет

- FQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETДокумент10 страницFQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETJavier Ayerdis NarváezОценок пока нет

- 5305SДокумент10 страниц5305SHugo Camacho RamirezОценок пока нет

- F540NSДокумент10 страницF540NSedgarlibanioОценок пока нет

- Mosfet 10NM60NДокумент19 страницMosfet 10NM60NRicardo Misael Torres0% (1)

- Irfps 3810 PBFДокумент8 страницIrfps 3810 PBFCrisan Radu-HoreaОценок пока нет

- International Rectifier IRFP2907Документ9 страницInternational Rectifier IRFP2907scribd20110526Оценок пока нет

- FET 75N75 TransistorДокумент8 страницFET 75N75 Transistorshahid iqbalОценок пока нет

- Irlz 24 NДокумент9 страницIrlz 24 NRobson PontinОценок пока нет

- Irf1324s 7ppbfДокумент10 страницIrf1324s 7ppbfAnonymous Gblw2LОценок пока нет

- IRF3710Документ8 страницIRF3710Andrés MorochoОценок пока нет

- 750W RF Power MOSFET DatasheetДокумент4 страницы750W RF Power MOSFET DatasheetDurbha RaviОценок пока нет

- F1010EДокумент8 страницF1010EKamran KhanОценок пока нет

- P-Channel Enhancement Mode BSH205 MOS Transistor: Features Symbol Quick Reference DataДокумент7 страницP-Channel Enhancement Mode BSH205 MOS Transistor: Features Symbol Quick Reference DataKumar Amit VermaОценок пока нет

- FQB8N60C / FQI8N60C: 600V N-Channel MOSFETДокумент9 страницFQB8N60C / FQI8N60C: 600V N-Channel MOSFETemelchor57Оценок пока нет

- Irl 530 NДокумент9 страницIrl 530 NEric Lenin Marin MoncadaОценок пока нет

- FQPF8N80CДокумент11 страницFQPF8N80CWsad WsadОценок пока нет

- Irfp2907Pbf: Typical ApplicationsДокумент9 страницIrfp2907Pbf: Typical Applicationsrajeev_kumar_1231852Оценок пока нет

- Irfz 24 NДокумент9 страницIrfz 24 Njmbernal7487886Оценок пока нет

- PHD 98 N 03Документ14 страницPHD 98 N 03Kevin TateОценок пока нет

- Buk453 100aДокумент7 страницBuk453 100amicrowave440Оценок пока нет

- Qfet Qfet Qfet Qfet: FQP55N10Документ8 страницQfet Qfet Qfet Qfet: FQP55N10andreanuovoОценок пока нет

- Si4634dy PDFДокумент10 страницSi4634dy PDFVehid ParićОценок пока нет

- Irfp 150 NДокумент8 страницIrfp 150 NPerversso SkellingtonОценок пока нет

- B44P04Документ7 страницB44P04aldo_suviОценок пока нет

- Pmv65Xp: 1. Product ProfileДокумент12 страницPmv65Xp: 1. Product Profilealoksharma20Оценок пока нет

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsОт EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsОценок пока нет

- 110 Waveform Generator Projects for the Home ConstructorОт Everand110 Waveform Generator Projects for the Home ConstructorРейтинг: 4 из 5 звезд4/5 (1)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1От EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Рейтинг: 4.5 из 5 звезд4.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- ECED Lab ReportДокумент18 страницECED Lab ReportAvni GuptaОценок пока нет

- HSPA+ Compressed ModeДокумент10 страницHSPA+ Compressed ModeAkhtar KhanОценок пока нет

- Accident Causation Theories and ConceptДокумент4 страницыAccident Causation Theories and ConceptShayne Aira AnggongОценок пока нет

- Illustrator CourseДокумент101 страницаIllustrator CourseGreivanОценок пока нет

- CVP Solution (Quiz)Документ9 страницCVP Solution (Quiz)Angela Miles DizonОценок пока нет

- (Jf613e) CVT Renault-Nissan PDFДокумент4 страницы(Jf613e) CVT Renault-Nissan PDFJhoanny RodríguezОценок пока нет

- S4H - 885 How To Approach Fit To Standard Analysis - S4HANA CloudДокумент16 страницS4H - 885 How To Approach Fit To Standard Analysis - S4HANA Cloudwai waiОценок пока нет

- Business PlanДокумент9 страницBusiness PlanRico DejesusОценок пока нет

- Cycles in Nature: Understanding Biogeochemical CyclesДокумент17 страницCycles in Nature: Understanding Biogeochemical CyclesRatay EvelynОценок пока нет

- BIU and EU functions in 8086 microprocessorДокумент12 страницBIU and EU functions in 8086 microprocessorDaksh ShahОценок пока нет

- Coa - Ofx-8040a (H078K5G018)Документ2 страницыCoa - Ofx-8040a (H078K5G018)Jaleel AhmedОценок пока нет

- Duty Entitlement Pass BookДокумент3 страницыDuty Entitlement Pass BookSunail HussainОценок пока нет

- Sample Contract Rates MerchantДокумент2 страницыSample Contract Rates MerchantAlan BimantaraОценок пока нет

- WM3000U - WM3000 I: Measuring Bridges For Voltage Transformers and Current TransformersДокумент4 страницыWM3000U - WM3000 I: Measuring Bridges For Voltage Transformers and Current TransformersEdgar JimenezОценок пока нет

- Entrepreneurship and EconomicДокумент2 страницыEntrepreneurship and EconomicSukruti BajajОценок пока нет

- Leapfroggers, People Who Start A Company, Manage Its Growth Until They Get Bored, and Then SellДокумент3 страницыLeapfroggers, People Who Start A Company, Manage Its Growth Until They Get Bored, and Then Sellayesha noorОценок пока нет

- Trustees Under IndenturesДокумент233 страницыTrustees Under IndenturesPaul9268100% (6)

- Personal InsuranceДокумент11 страницPersonal InsuranceSumit Kumar SharmaОценок пока нет

- ViscosimetroДокумент7 страницViscosimetroAndres FernándezОценок пока нет

- TicketДокумент2 страницыTicketbikram kumarОценок пока нет

- SIWES Report Example For Civil Engineering StudentДокумент46 страницSIWES Report Example For Civil Engineering Studentolayinkar30Оценок пока нет

- FOMRHI Quarterly: Ekna Dal CortivoДокумент52 страницыFOMRHI Quarterly: Ekna Dal CortivoGaetano PreviteraОценок пока нет

- HW3Документ3 страницыHW3Noviyanti Tri Maretta Sagala0% (1)

- Kunci Jawaban Creative English 3BДокумент14 страницKunci Jawaban Creative English 3BLedjab Fatima67% (3)

- Air Cycle Refrigeration:-Bell - Coleman CycleДокумент21 страницаAir Cycle Refrigeration:-Bell - Coleman CycleSuraj Kumar100% (1)

- HetNet Solution Helps Telcos Improve User Experience & RevenueДокумент60 страницHetNet Solution Helps Telcos Improve User Experience & RevenuefarrukhmohammedОценок пока нет

- Movie Review TemplateДокумент9 страницMovie Review Templatehimanshu shuklaОценок пока нет

- 702190-Free PowerPoint Template AmazonДокумент1 страница702190-Free PowerPoint Template AmazonnazОценок пока нет

- 3000W InverterДокумент2 страницы3000W InverterSeda Armand AllaОценок пока нет

- Oscar Ortega Lopez - 1.2.3.a BinaryNumbersConversionДокумент6 страницOscar Ortega Lopez - 1.2.3.a BinaryNumbersConversionOscar Ortega LopezОценок пока нет