Академический Документы

Профессиональный Документы

Культура Документы

Logic State Analyser (Project)

Загружено:

DIPAK VINAYAK SHIRBHATEИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Logic State Analyser (Project)

Загружено:

DIPAK VINAYAK SHIRBHATEАвторское право:

Доступные форматы

Logic State Analyser

CHAPTER I

1. INTRODUCTION

1.1 Overview :

Major advances in Computer Technology have been closely

followed by an associated set of advances in test equipment. As digital design

has become more sophisticated, the tools have evolved to fill new needs.

Using data analysis to locate problem in data flow raised test

requirements that existing instruments could not meet. The designer needed

data registration or synchronisation between the two systems, data capture, data

formatting and data display. Wide spread use of microcomputers placed

additional demands on existing test equipment. Many mechanical functions

were replaced by software. Integration of this software with hardware during

product development became one of the most frustrating tasks confronting

digital designers. The ever increasing use of micro-computer systems in every

sector of business and industry emphasises the need of an equipment for new

product development and critical trouble shooting. Logic analyzers play a

major role in performing the above functions.

1.2 Logic Analysers :

The logic analyser, a form of digital oscilloscope, has evolved as

the most convenient trouble shooting tool for micro-computers. Despite its

name, the logic analyser does not analyse the data. Instead, it displays digital

Govt. Poly. Washim.

Logic State Analyser

data in a convenient form, either as rectangular waveforms representing the

digital data or in tabular forms as binary 1s and 0s that can be analysed by the

test engineer.

The modern logic analysers can be used for a variety of

applications typical of which are given below :

i) i) With its digital storage, the analyser is capable of capturing any

long and infrequent logic sequences and display it, which is

virtually impossible with conventional instruments.

ii) Analysers digital delay makes it possible to observe any section of a

long bit sequence without any uncertainty so that there is no need to

count clock pulses.

iii) In its spike mode, the analyser captures and displays the short

randomly occurring noise pulses that often is very difficult to detect

by conventional methods.

Although originated only in the early 1970's the logic analyser has

been improved considerably.

1.3 Basic Logic Analyser :

The block diagram of a basic logic analyser is shown in Fig.1.1

Data and control signals are given on the respective buses. When the

control signal matches with the data, the data is transferred on to the latches.

The point at which the data event is captured is called the trigger event.

Govt. Poly. Washim.

Logic State Analyser

From the latch, the data goes on to the decoder where it is decoded and given to

an output device, a seven segment display in the simplest case.

The trigger switch is used to clear the latches and the display and

to make the analyser ready to acquire the next set of data.

1.4 Types of Logic Analysers :

There are two types of logic analysers :

i) Logic Time Analyser and

ii) Logic State Analyser.

Logic Time Analyser :

In logic design there is always concern about race conditions,

set up and hold times, clock line reflections and other electrical phenomena that

can cause improper operation of a logic circuit. When these happenings need to

be viewed in a low repetition rate environment, in context with several other

signals, an ordinary oscilloscope's usefulness is low, consequently, a logic

timing analyser which samples a multi channel source at a rate determined by an

internal clock can store the logic value of each input at the sample time and

thereby reconstruct a logic timing diagram of the signals being observed. In

its glitch mode it can detect glitches, which are very narrow pulses coming in

between clock pulses, of a few nano seconds pulse width.

Thus, a logic time analyser is an optimal tool to view activity on

logic circuits operating synchronously, asynchronously or concurrently. The

primary function of a time analyser is to provide a display of functional

Govt. Poly. Washim.

Logic State Analyser

timing relations between signals on a logic circuit that is the output

displayed is a waveform of voltage Vs time. So, if there are n-inputs, we get

n-waveforms.

Logic State Analyser :

This is an instrument aimed at measuring the functional

performance of a digital circuit. This helps designers trouble shoot

algorithmic state machines where knowledge of the state sequences are most

important. In this type of analyser, a multi channel input is sampled at a time

defined by the system under test. Each channel is then interpreted as a logic

‘true’ or ‘false’ and a functional display of logic values is presented. The

display can be binary, hexadecimal or octal numbers grouped in rows and

columns.

In other words, a logic state analyser captures and displays the

flow of events occurring synchronously, in a logic system. It presents a

real time window by transparently monitoring the activity on the

operating system. The display of a n-input state analyser is a nxn matrix

where each element of the matrix is a ‘zero’ or a ‘one’. Each row shows one

input and the n-elements of each row show the state of that input over a period

of n-clock pulses.

For example, when you analyse digital circuits, that have many

output lines, such as a random access memory, it is advantageous to be able to

display and compare eight or more signals at the same time. This is one of the

Govt. Poly. Washim.

Logic State Analyser

functions of a logic state analyser. In its simplest form, a logic state analyser

is just a device that chops or alternates between eight or more input channels to

produce an oscilloscope trace for each. A word recogniser allows you to trigger

when a specific word or pattern of 1s and 0s is present on the input lines. Logic

analysers also may display the information from these channels as a string of 1s

and 0s, as a plot of points, or as hexadecimal words. Most logic analysers

contain a continuously recording memory that permits display of data which

occured before the trigger.

Govt. Poly. Washim.

Logic State Analyser

CHAPTER II

A REVIEW OF LOGIC ANALYSERS

2.1 Working of a typical logic analyser :

As we have seen, there are two types of logic analysers. They are

logic state and logic time analysers. In both instruments, the input block

captures the logic sequence of 0s and 1s from the system under test and store

it in a digital storage unit. But display sections are different. In the time

analysis, the stored data is displayed on an oscilloscope screen as a

wavefrom of voltage versus time. So if there are 'n' input channels, we get a

display of n-channels simultaneously on the same screen. But in state

analysis, this is different. Here the input data is displayed as a matrix

form. Each row of the matrix denotes a single word, and each element of the

matrix will be a 'zero' or a 'one' according to the input.

Any analyser has got two main blocks. They are

(i) Data Acquisition block and

(ii) Display block.

If the analyser is a 16-bit one, its data acquisition block gathers

16 bits of input data sequence for each clock pulse and stores it in a Random

Access Memory. Once the storing of a fixed number of words of 'zeros' and

'ones' is over, the control goes to the display section. Here, an internal clock

Govt. Poly. Washim.

Logic State Analyser

addresses the RAM through a memory address counter. The output of the RAM

is selected by the same clock serially and, using a digital multiplexer fed to

the 'Y'-input of the CRT through a D/A converter. For displaying a voltage

versus time waveform, a ramp is fed to the 'X' input. For state display, the

ramp should be intermittent. This is just like a staircase voltage. After

displaying each word, the DC component of 'Y'-input is shifted so that, now

the beam is at a different level on the screen. Likewise, we can display all the

words by giving suitable DC shifts.

To produce a zero, a sinewave is super-imposed over the Y-input of

CRT and the same sinewave shifted by 90 in phase and slightly reduced in

amplitude is fed to X-input, so that it will produce an ellipse. To obtain a

'one', the cosine wave superimposing over the X-input is the output.

2.2 Modes of operation :

Commercial equipments have many modes of operation. Some of

the important modes are as follows :

In the start display mode, data is written constantly into memory.

When a match between incoming data and a preset trigger word occurs, the data

acquisition block will store 16 or 32 words that follow the trigger word,

depending on the capacity of the instrument.

Govt. Poly. Washim.

Logic State Analyser

The start delay mode is essentially the same except that data

acquisition starts after the preset number of clock pulses are counted. Then

the acquisition continues for the next 16 or 32 clock pulses and stops.

In the end display mode, the trigger word comes in the last so that

on the screen, we get 15 words that come before the trigger word and finally the

trigger word also. This mode is useful to study what actually is happening

before a particular trigger word.

Govt. Poly. Washim.

Logic State Analyser

CHAPTER III

SYSTEM PLANNING

3.1 Logic State Analyzer :

The two types of logic analyzers, viz. Time and state have been

described earlier. For debegging of microprocessor based systems, logic state

analysers are superior. With this in mind, it was decided to build a simple

logic state analyzer.

The following factors were also borne in mind before embarking

upon this project :

a) The cathode ray oscilloscope will be an excellent display device.

b) Random Access Memories can be used to store the input data.

Subsequently it can be displayed by additional circuitry.

c) Integrated circuit blocks will be used wherever possible. This

will reduce the system size and cost drastically.

d) Good results can be obtained by limiting the band width in the range of

tens of kilohertz.

Since, very good oscilloscopes and integrated circuit chips were

readily available, it was not very difficult to develop such an analyzer.

Govt. Poly. Washim.

Logic State Analyser

3.2 Circuit Block :

The entire circuit comprises of individual blocks such as

comparator, memory, trigger word comparator, clock generator, counter,

multiplexer, monostable multivibrator etc. which are connected together.

3.3 System operation :

A logic analyser has got two main blocks. They are

a) Data acquisition block and

b) Display block

The functions of the two blocks are clear from the names itself.

The two blocks are briefly described below.

Data acquisition block :

As the name indicates, this is the block where the input data is

collected and stored. Storing is essential since we require a constant display of

a particular event that has occured.

First, the 8-bit input signal goes to a comparator. Here, the

incoming voltage levels are compared to the instrument's threshold level to

classify them as 'HIGH' or 'LOW'. This threshold level is made variable using

a buffer amplifier and a potentiometer arrangement. This variable

arrangement is necessary in order to make the analyser to test equipments

comparing of any family i.e., TTL, CMOS, ECL etc. Since each family has a

different threshold level. From the output of the temporary storage where

Govt. Poly. Washim.

Logic State Analyser

they are stored temporarily. The system clock also is taken through a

comparator. Afterwards, it drives a monoshot multivibrator to produce a write

enable pulse for the Random Access Memory.

The outputs of the temporary storage unit are passed on to the

memory and to the trigger word comparator where they are compared with front

panel trigger word switch settings. When a match occurs, it will give an output

pulse which will enable the write enable pulse to reach RAM thus initiating the

storage process. Once 8 words are stored, the data index flip flop is set, thus

disabling the write pulse. Data ready output goes high which will enable the

display section. The Read/Write pin of the RAM becomes 'one' which will

enable the RAM output.

Display Block :

This section has two counters, horizontal and vertical 8 state

counters. These select the word (8-bit) in the memory to be displayed and

positions the CRT beam by way of digital to analog converter. The required

CRT beam positioning waveforms are as shown in the Fig. . The count of

the horizontal counter is also applied to 1 of 8 selector that select the bit in a

particular word that is to be displayed.

The counter is incremented by an internally generated clock

and it steps through all of its 8 states before resetting. While resetting it

increments the memory address counter and the vertical counter. Thus all the 8

words in the memory are scanned one by one.

Govt. Poly. Washim.

Logic State Analyser

A CRO is used to display the data and as the data consists of

0's and l's only, these can be displayed on the CRO screen by making use of

the property of Lissajous figures. The lissajous figures are shown in Fig.

Characters are generated by superimposing a 10 KHz sine wave

on the deflection voltage. The sine wave to the horizontal deflection

system is shifted about 90 0 by a capacitor and reduced slightly in

amplitude so that an ellipse is written. To trace a '1', the sine wave to the

horizontal is switched off. This is done by making use of a transistor as a

switch.

3.4 Detailed circuit blocks :

Having discussed the functioning of Data Acquisition and display

sections, it is found that the following circuit blocks are required for system

realization :

a) Voltage comparators

b) Digital storage unit

c) Binary counters

d) Magnitude comparators

e) Monoshot multivibrator

f) Internal clock generator

g) Multiplexer

All the above are available in the standard monolithic integrated

circuit form.

Govt. Poly. Washim.

Logic State Analyser

3.5 Choice of devices and integrated circuits :

a) Voltage comparator :

Operational amplifiers can work as excellent voltage

comparators. LM 324 Quad Op Amps will be a very good selection. It

provides 4 operational amplifiers in one chip thus reducing the number of chips

used and still maintaining sufficient band width.

b) Digital storage unit :

This is a very important part of the instrument. An 8 bit, 8 word

Read/Write memory is required. The 7489 Random Access Memory provides 4

bit, 16 words capacity. So two 7489 RAMs in parallel provide the required 8-bit

word length. For temporary storage of data, before storing it in the RAM, 7475

latches have been used.

c) Binary counters :

A 3-bit binary counter is required to address the RAM. Also, in

the display section, two 3-bit binary counters are required. 7493 is a suitable

choice as it provides both, the counter and also it can be reset to zero by simply

giving a high signal to the particular pins.

d) Magnitude comparator :

To start the display from a particular word, we should be able to

set any 8-bit word as a trigger word so that when the input word is the same,

the trigger word comparator triggers the data acquisition. To provide the

trigger word facility, an 8-bit magnitude comparator is needed. 7485 is a 4-bit

Govt. Poly. Washim.

Logic State Analyser

magnitude comparator. So, two 7485 ICs have been used to give the required

8-bit comparator. In each chip, A 0- A0 , are connected to the input and B 0,- B 0 ,

are the programmable trigger word.

e) Monostable multivibrator

To give the write enable pulse to the Random Access Memory, a

monostable masturbator is used. IC 74123 is chosen, as the frequency of the

output can be controlled by using external resistor and capacitors.

f) Internal clock generator :

In the display section, the input has to be selected one by one and

they have to be displayed at a fast rate. For this, a clock of about 100 KHz is

needed. LM 555 timer can easily meet this requirement.

g) Multiplexer unit :

The data stored in the RAM has to be displayed one by one.

The RAM gives out all the 8 lines in a parallel form. It has to be multiplexed

and displayed on the oscilloscope screen. IC. 74151 is used since it is an 8-

line to 1-line multiplexer.

h) Flip-flops :

Two flip-flops are needed in the circuit. IC. 7476 is used since it

has two flip-flops on a single chip as also the necessary preset and clear

terminals.

Govt. Poly. Washim.

Logic State Analyser

CHAPTER IV

CIRCUIT DESIGN

The system planning of the logic state analyzer has been discussed

in the previous chapter. In this chapter, we shall discuss the .actual circuit

design.

4.1 Operational Amplifier Comparator :

In a comparator, the Op-amp is used in its non-linear mode. The

output of the comparator will be in any of the two states, either 'HIGH' or

'LOW i.e., this circuit converts any input to a two level output. A comparator

compares the input with a reference voltage and tells whether it is greater

than or less than the reference voltage.

A practical Op-amp has got a very large open loop voltage

gain and hence it can be used as a comparator. We give the reference voltage to

the non-inverting terminal and input to the inverting terminal of the operational

amplifier. When input is less than V ref, the output goes 'high' and when the input

is greater than Vref , the output goes 'low'.

There is every chance of oscillations in this simple scheme. To

prevent this, we can use the hysteresis property of Op-amps. It is explained as

follows.

Govt. Poly. Washim.

Logic State Analyser

Let as assume that the Op-amp output is varying between 0 and V cc.

From the figure, when

e1 < e1

e 0 = vcc

and by super position principle,

V ref R 2 + V cc R 1

e i1 =

R1 + R2

Once e1 < e0

e0 = 0

and V ref R 2

e i1 =

R1 + R2

So e i1 < ei2

This is explained by the hysteresis curve as shown in fig. 4.2.

As ‘e1 ’ increases’ at point A’ e 0 comes down to 0 volt. Now for ‘e 0’

to go again to V cc , e1 should fall to e i2 , so, only at B, e 0 goes from 0 volt to V cc .

Hence, even if e1 varies slightly’ the operational amplifier will not oscillate.

The input unit consists of 8 such Op-amps working as 8

comparators. The non-inverting terminals of each of them are connected

together and commonly given to a threshold reference level. This level is

variable. This is obtained by a potentiometer arrangement and a buffer amplifier.

Whenever the input voltage goes higher than the reference level, the output

Govt. Poly. Washim.

Logic State Analyser

comes down. When the input voltage is less than the reference level, the output

goes 'high'.

The values of the resistors are as follows :

R 1 = 10 Kilo Ohms

R 1 = 1 Mega Ohms

The I Kilo Ohms and 390 Ohms resistor combination at the

output of each Op-amp, makes it the standard TTL input to the latch.

4.2 Storage Unit :

There are two basic units here. First, the outputs of LM 324 is

stored in 7475 Quad Latch. This latch will take the input to its output when

clock goes 'high' and retain it when clock goes 'low'. The outputs of the latch

go to the inputs of the Random Access Memory.

The 7489 RAM requires a write enable pulse of minimum 30 nano

seconds pulse width. This is provided by monoshot 74123. For each rising

edge of clock, it will give a pulse of about 20 microseconds pulse width. The

pulse width is given by the equation given below :

t w = 0.32 R T C ext [ 1 + (0.7/ R T ) ]

where,

t w is the microseconds

R T is in Kilo Ohms

C ext is in micro Farads

By calculation, the values of resistance and capacitance are

Govt. Poly. Washim.

Logic State Analyser

R = 10 Kilo Ohms

C = 6 K pF = 6 micro Farads

The clock is not given directly to the RAM, but it is given

through the monoshot multivibrator. This is done to make it possible to adjust

the pulse width of clock (coming out of the multivibrator) by choosing proper

values of R T and C ext in accordance with write enable pulse width of the RAM.

When we give proper address and write enable pulse, the RAM

will store the input word in that particular location. The chip select is grounded

so that always the RAM will be enabled. When the Read/Write pin is kept

'high', the output of RAM will be enabled. This is the Read Mode.

4.3 Trigger word comparator :

In order to start the display from a specific word onwards, it is

necessary to have a trigger word. We should be able to set any 8-bit word as

trigger word so that when the input word is same, the trigger word comparator

triggers data acquisition. 7485 is a 4-bit magnitude comparator. Two 7485's

are connected in parallel and give the required 8-bit comparator. In each chip, A 0

- A3 are connected to the input word and B 0 - B 3 are the programmable trigger

word. By suitably connecting B 0 - B 3 to V cc or ground, it is possible to get

any 8-bit reference word. Whenever a match occurs, the output of 7485 goes

'high'. This will set the 7476 master slave flip-flop which in turn enables the

write enable pulse of the RAM.

Govt. Poly. Washim.

Logic State Analyser

4.4 Internal clock generator :

The displays of 64 bits are obtained by multiplexing all the 64 bits

on the screen. This requires a high frequency clock. LM 555 timer has been

used to generate this high frequency clock.

The circuit diagram is a special case to generate 50% duty cycle

clock, t 1 and t2 are given by the equation.

t 1 = 0.693 R AC

R AR B R B - 2R A

t2 = .Cl n - RA

RA + RB 2 RB

This circuit will not oscillate if RB > ½ R A

R A = 18 Kilo Ohms

R B = 8.2 Kilo Ohms

So, f = 148 KHz

4.5 Binary counters :

To store the data in the RAM, first we have to give an address. A

4 bit binary counter chip 7493 can be used as memory address counter. The

clock to this counter is the same as the write enable pulse of RAM. So, each

time the pulse goes 'low', it will enable the RAM for writing and when it goes

high, the counter increases one count and addresses the next location. When

the count reaches 9, a second master slave flip-flop is set. Thus Q becomes

zero. This will disable the write enable pulse. Also, the data ready

terminal goes 'high'. This enables the display section.

Govt. Poly. Washim.

Logic State Analyser

The display section also contains two such counters, one gives the

x-input voltage of oscilloscope, through a weighted resistor arrangement.

Resetting of horizontal counter will set vertical counter which helps to align

the beam in variable vertical position.

4.6 Multiplexer :

The data stored in RAM has to be displayed one by one. An 8 line

to one line 74151 multiplexer chip has been used for this. 3 bit address is given

to the chip to select the data. This address is derived from the horizontal

counter. The weighted resistor arrangement helps the beam to scan through

each bit and display it as either a '0' or a '1'. For different combinations of

counter outputs, the current flowing through the resistor will change and

hence the voltage drop across it also changes. This drop is given to 'X' and 'Y'

inputs.

The resistors used for the purpose are given below :

X – input Y – input

R 1 = 1 kilo Ohms R 1 = 180 kilo Ohms

R 2 = 2 kilo Ohms R 2 = 470 kilo Ohms

R 3 = 5.6 kilo Ohms R 3 = 1.0 kilo Ohms

R 4 = 1 kilo Ohms R 4 = 5.6 kilo Ohms

Govt. Poly. Washim.

Logic State Analyser

4.9 Digital analog converters

There are two types of D/A converters; one which uses a binary

weighted resistor network, and the other which uses an R and 2R resistor

network. We have used the former one. As we need a negative going

staircase waveform for positioning the CRO beam, an inverter is used along

with the D/A converter. The values of the resistors used are;

for Horizontal :

for Vertical :

Govt. Poly. Washim.

Logic State Analyser

CHAPTER V

FABRITATION AND TESTING

Fabrication :

The P.C.B. was fabricated by us in a simple manner. Initially,

the whole circuit was rearranged in a proper way i.e., according to the

respective pin positions of each I.C. Next, the connections were made in such a

way so as to avoid any overlap as far as possible. Whenever, this was not

possible, a 'jump' connection was made.

This circuit was then redrawn on an inch graph sheet with exact

dimensions of the ICs and pin distances. This circuit is called the 'art work'.

This was then pasted or fixed on to a single sided copper clad board. Holes were

then drilled into the board at the points of all the components. 0.7 mm φ

drill bit for ICs and 1 mm φ drill bit for resistors, capacitors etc., was used. The

graph sheet was then removed and using a 'marker' pen, all the circuit

connections were drawn on the copper board. This board was then dipped in

a solution of Ferric chloride. After approximately 20 minutes, when the

board was removed and washed throughly with water, it was ready to be

soldered upon, since all the area other than where the 'marker' pen was used,

was now devoid of copper. Marks of the marker pen are removed either by

scraping or by using a volatile solvent like spirit or petrol.

Govt. Poly. Washim.

Logic State Analyser

The components were then placed in their respective positions

and soldered and the circuit was then ready for testing. The PCBs copper

side is then coated with wax to avoid corrosion of copper due to ageing.

Testing :

For testing the circuit, a 7493, 4 bit counter IC was used. The

outputs of the counter are connected to the first four LSB bits of the input lines

of the analyser. The other four lines are grounded. The trigger word is set at

'0000' so that data acquisition starts as soon as the power is switched on.

The X and Y outputs of display section are connected to X and a Y input of

oscilloscope and the oscilloscope is put in the external mode. On the CRO, we

got an output which showed us the states of the four counter outputs for eight

clock pulses.

The trigger word was then set at another value and it was seen

that the data acquisition started after that word and the data upto eight clock

pulses after that word was displayed.

Govt. Poly. Washim.

Logic State Analyser

APPENDIX – 1

SPECIFICATION OF THE LOGIC STATE ANALYZER

1. Repetition rate 0 – 20 KHz

2. Input impedance 100 kilo Ohms

3. Input bias currents 45 nA

4. Input threshold variable 0 to 10 v

5. Minimum input swing threshold + 100 mV

6. Display clock pulse width 148 KHz

7. Minimum clock pulse width 100 n sec.

8. number of channels 8

9. Power supply +10 V and +5 V

Govt. Poly. Washim.

Logic State Analyser

APPENDIX – II

LIST OF COMPONENTS

ICs No. of Pieces

LM 324 3

7475 2

7485 2

7489 2

7476 1

7493 3

74151 1

74123 1

LM555 1

7408 1

7400 2

7404 1

Resistors No. of Pieces

10 Kilo ohms/1/4 W 12

1 Kilo ohms 9

1 Mega ohms 14

390 ohms 9

8.2 Kilo ohms 1

Govt. Poly. Washim.

Logic State Analyser

18 Kilo ohms 1

5.6 Kilo ohms 1

2.2 Kilo ohms 1

470 ohms 1

Transistor No. of Pieces

2N2222 1

Presets No. of Pieces

10 Kilo ohms 1

47 Kilo ohms 1

22 Kilo ohms 2

Govt. Poly. Washim.

Logic State Analyser

REFERENCES

1. Microprocessors/Microcomputers, Architecture, Software and systems by

Adi. J. Khambatta.

2. Micro Computer Handbook.

by J.A. McCrindle.

3. Microprocessors and Digital Systems.

by Doughlous. V. Hall.

4. Introduction to System Design Using Integrated Circuits.

by B.S. Sonde.

5. OP-AMPS and Linear Integrated Circuit Technology

by Ramakant. A. Gayakwad.

Govt. Poly. Washim.

Logic State Analyser

CONTENTS

Sr. No. Particular Page No.

1. Introduction

1.1 Overview 1

1.2 Logic Analysers 1

1.3 Basic Logic Analyser 2

1.4 Types of Logic Analysers 3

2. A review of Logic Analysers

2.1 Working of a Typical Logic Analyzer 6

2.2 Modes of Operation 7

3. System Planning

3.1 Logic State Analyzer 9

3.2 Circuit Blocks 10

3.3 System Operation 10

3.4 Detailed Circuit Blocks 12

3.5 Choice of Devices and Integrated Circuits 13

4. Circuit Design

4.1 Operation Amplifier Comparator 15

4.2 Storage Unit 17

4.3 Trigger Word Comparator 18

4.4 Internal Clock Generator 19

4.5 Binary Counters 19

4.6 Multiplexer 20

4.7 Digital to Analog Convertors 21

5 Fabrication And Testing

5.1 Fabrication 22

5.2 Testing 23

Appendices 24

References 27

Govt. Poly. Washim.

Вам также может понравиться

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- NSN Lte-Advanced White PaperДокумент20 страницNSN Lte-Advanced White Paperjoseph221106Оценок пока нет

- Related Literature and Studies of AntennaДокумент4 страницыRelated Literature and Studies of AntennaStephen Joy ArellanoОценок пока нет

- On Hacking MicroSD Cards Bunnie's BlogДокумент13 страницOn Hacking MicroSD Cards Bunnie's BlogDiego HernandezОценок пока нет

- Car Video Interface Porsche PCM2.1 Manual enДокумент13 страницCar Video Interface Porsche PCM2.1 Manual enTomaz RdvnОценок пока нет

- DFT DRC - PPT 0Документ3 страницыDFT DRC - PPT 0Mohan RajОценок пока нет

- Educational Multimedia On Hydraulics and PneumaticsДокумент89 страницEducational Multimedia On Hydraulics and PneumaticsDIPAK VINAYAK SHIRBHATEОценок пока нет

- Quality Circle A Case Study: Prof. D.V. Shirbhate Principal, Vikramshila Polytechnic DarapurДокумент34 страницыQuality Circle A Case Study: Prof. D.V. Shirbhate Principal, Vikramshila Polytechnic DarapurDIPAK VINAYAK SHIRBHATEОценок пока нет

- Aahan's BirthdayДокумент22 страницыAahan's BirthdayDIPAK VINAYAK SHIRBHATEОценок пока нет

- New File ListДокумент2 страницыNew File ListDIPAK VINAYAK SHIRBHATEОценок пока нет

- Quality Circles For Vikramshila StudentsДокумент22 страницыQuality Circles For Vikramshila StudentsDIPAK VINAYAK SHIRBHATEОценок пока нет

- Kaizan Presentation 11092012Документ12 страницKaizan Presentation 11092012DIPAK VINAYAK SHIRBHATEОценок пока нет

- 2 Dipak Vinayak Shirbhate VSRDIJMCAPE 3631 Research Paper 4 8 August 2014Документ8 страниц2 Dipak Vinayak Shirbhate VSRDIJMCAPE 3631 Research Paper 4 8 August 2014DIPAK VINAYAK SHIRBHATEОценок пока нет

- Dipak Vinayak Shirbhate VSRDIJMCAPE 3631 Set PPRДокумент6 страницDipak Vinayak Shirbhate VSRDIJMCAPE 3631 Set PPRDIPAK VINAYAK SHIRBHATEОценок пока нет

- Boys Hostel FormДокумент1 страницаBoys Hostel FormDIPAK VINAYAK SHIRBHATE100% (1)

- Girls Hostel FormДокумент1 страницаGirls Hostel FormDIPAK VINAYAK SHIRBHATEОценок пока нет

- Kirti Polytechnic Prospectus Part AДокумент5 страницKirti Polytechnic Prospectus Part ADIPAK VINAYAK SHIRBHATEОценок пока нет

- Dipak Vinayak Shirbhate VSRDIJCSIT 3479 Research Communication June 2014Документ4 страницыDipak Vinayak Shirbhate VSRDIJCSIT 3479 Research Communication June 2014DIPAK VINAYAK SHIRBHATEОценок пока нет

- Domestic Water Heater PDFДокумент39 страницDomestic Water Heater PDFDIPAK VINAYAK SHIRBHATEОценок пока нет

- Salary Slip - May 2014Документ5 страницSalary Slip - May 2014DIPAK VINAYAK SHIRBHATEОценок пока нет

- Ad Draft Approved by MsbteДокумент1 страницаAd Draft Approved by MsbteDIPAK VINAYAK SHIRBHATEОценок пока нет

- Prospectus For 13-14Документ42 страницыProspectus For 13-14DIPAK VINAYAK SHIRBHATEОценок пока нет

- Equivalence of Discipline Praposed Draft For Tech InstitutesДокумент14 страницEquivalence of Discipline Praposed Draft For Tech InstitutesDIPAK VINAYAK SHIRBHATEОценок пока нет

- Domestic Water Heater PDFДокумент39 страницDomestic Water Heater PDFDIPAK VINAYAK SHIRBHATEОценок пока нет

- Prospectus For 14-15Документ44 страницыProspectus For 14-15DIPAK VINAYAK SHIRBHATEОценок пока нет

- Pramod Naik's Letter Director MsbteДокумент1 страницаPramod Naik's Letter Director MsbteDIPAK VINAYAK SHIRBHATEОценок пока нет

- Inplant TrainingДокумент1 страницаInplant TrainingDIPAK VINAYAK SHIRBHATEОценок пока нет

- Prospectus Data 2013-14Документ12 страницProspectus Data 2013-14DIPAK VINAYAK SHIRBHATEОценок пока нет

- Vikramshila Polytechnic DarapurДокумент1 страницаVikramshila Polytechnic DarapurDIPAK VINAYAK SHIRBHATEОценок пока нет

- Creativity & The Business IdeaДокумент12 страницCreativity & The Business IdeaDIPAK VINAYAK SHIRBHATEОценок пока нет

- Vikramshila Poly Prospectus MarathiДокумент29 страницVikramshila Poly Prospectus MarathiDIPAK VINAYAK SHIRBHATEОценок пока нет

- Performance ApprisalДокумент12 страницPerformance ApprisalDIPAK VINAYAK SHIRBHATEОценок пока нет

- Importance of Diploma Education For Rural StudentsnnДокумент55 страницImportance of Diploma Education For Rural Studentsnnvspd2010Оценок пока нет

- Classification of EnterprenuersДокумент12 страницClassification of EnterprenuersDIPAK VINAYAK SHIRBHATE100% (2)

- Pragati Ahawal, 2010 11Документ9 страницPragati Ahawal, 2010 11DIPAK VINAYAK SHIRBHATEОценок пока нет

- Mobile Number of StudentsДокумент4 страницыMobile Number of Studentsvspd2010Оценок пока нет

- De Lab Manual-EEE New1Документ77 страницDe Lab Manual-EEE New1selva_raj215414Оценок пока нет

- 9.3 Astable Multivibrator: Return NextДокумент8 страниц9.3 Astable Multivibrator: Return Nextsankar2015Оценок пока нет

- Xy FZ35Документ11 страницXy FZ35janekiviОценок пока нет

- Ex. No: 2a Simulation of 4X1 Multiplexer Using 3 Modeling Styles in Verilog Date: AimДокумент7 страницEx. No: 2a Simulation of 4X1 Multiplexer Using 3 Modeling Styles in Verilog Date: Aimsamhita santhanamОценок пока нет

- Manual Huawei E1750Документ7 страницManual Huawei E1750tineogxОценок пока нет

- BF998 Data SheetsДокумент9 страницBF998 Data SheetstarpinoОценок пока нет

- System Component and Protection DevicesДокумент16 страницSystem Component and Protection DevicesSandeep KumarОценок пока нет

- Cse 211 NotesДокумент41 страницаCse 211 NotesVamsi Krishna100% (1)

- HDDScan Eng PDFДокумент18 страницHDDScan Eng PDFnoisi80Оценок пока нет

- pg100 Axi EmcДокумент72 страницыpg100 Axi EmcSarang Purushottam PurnayeОценок пока нет

- Chap10 13 tmr2 PWMДокумент38 страницChap10 13 tmr2 PWMThanh LeОценок пока нет

- ACKS010Документ5 страницACKS010kallatisОценок пока нет

- 74688Документ4 страницы74688Alexandre S. CorrêaОценок пока нет

- Des 1024dДокумент2 страницыDes 1024dbxlmichael8837Оценок пока нет

- Nokia Lumia 925 - Service ManualДокумент68 страницNokia Lumia 925 - Service Manualwds555Оценок пока нет

- AVH-P5200DVD AVH-P5200BT: DVD Av Receiver Radio Av Con DVD Autoradio Av Lecteur de DVDДокумент32 страницыAVH-P5200DVD AVH-P5200BT: DVD Av Receiver Radio Av Con DVD Autoradio Av Lecteur de DVDCaron GuimaОценок пока нет

- TH-9800 - RF Test ReportДокумент43 страницыTH-9800 - RF Test ReportBenjamin DoverОценок пока нет

- Keep in Mind The Five Key Test Points LCD Screen Logic BoardДокумент2 страницыKeep in Mind The Five Key Test Points LCD Screen Logic BoardClubedoTecnicoОценок пока нет

- Lvsim EmsДокумент1 страницаLvsim EmsLadyminchin Dela CruzОценок пока нет

- WD Caviar SE: Desktop Hard DrivesДокумент2 страницыWD Caviar SE: Desktop Hard DrivesZoran ŠušakОценок пока нет

- Pump Control Pcu001Документ2 страницыPump Control Pcu001spreewellОценок пока нет

- Taller Chapter 16 PDFДокумент2 страницыTaller Chapter 16 PDFManuel ZuñiigaОценок пока нет

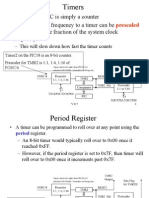

- Timer and CountersДокумент4 страницыTimer and CountersMathematics TutorОценок пока нет

- Px7103 Analysis and Design of InvertersДокумент3 страницыPx7103 Analysis and Design of InvertersRoja0% (1)

- 000000US6438 (30kva, 3X1,220VDC, 110VAC)Документ3 страницы000000US6438 (30kva, 3X1,220VDC, 110VAC)sayaliОценок пока нет