Академический Документы

Профессиональный Документы

Культура Документы

El Diseño Del Nivel de Microarquitectura

Загружено:

Manuel InciarteОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

El Diseño Del Nivel de Microarquitectura

Загружено:

Manuel InciarteАвторское право:

Доступные форматы

Repblica Bolivariana de Venezuela Ministerio del Poder Popular para la Defensa Universidad Nacional Experimental Politcnica de la Fuerza Armada

Bolivariana Ncleo Zulia

Integrantes: Hernndez Naheliel C.I.- 19075964 Inciarte Manuel C.I.- 19178565 Seccin: 06-ISI-V06 Maracaibo, Octubre de 2011

ESQUEMA: 1) El diseo de nivel de microarquitectura 2) Mejoramiento de desempeo 3) Ejemplo de nivel de microarquitectura

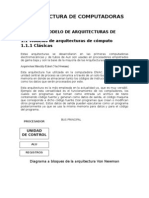

1)El diseo del nivel de microarquitectura. Las computadoras tienen muchas caractersticas deseables, como rapidez, bajo costo, confiabilidad, facilidad de uso, bajo consumo de energa y tamao fsico. Sin embargo el equilibrio que determina las decisiones ms importantes que el diseador de una CPU debe hacer es el de rapidez contra costo Rapidez versus costos: Existen varias formas de medir la rapidez, pero dada una tecnologa de circuitos y una ISA (arquitectura del conjunto de instrucciones), hay tres estrategias bsicas para aumentar la velocidad de ejecucin: Reducir el nmero de ciclos de reloj necesarios para ejecutar una instruccin. Simplificar la organizacin para que el ciclo de reloj pueda ser ms corto Traslapar la ejecucin de instrucciones. La primera y la segunda serian las ms obvias pero existen mltiples actividades que afectan a los ciclos del reloj y a pesar de que usemos hardware especializados para una actividad igual este se ver afectado por otro lado como por ejemplo el tiempo de espera de los datos proveniente de la memoria. En cambio si aprovechamos la tercera tcnica traslapar la ejecucin de instrucciones que no es ms que superponer las instrucciones o hacer que la unidad sea independiente de los circuitos que traen las instrucciones la velocidad ganada seria significativa. El costo es otro de los aspectos y este viene variando por la complejidad de los procesadores y tamao, los chips ms grandes y complejos son ms caros que los pequeos y sencillos. Entre mayor sea el rea que se requiere para las funciones incluidas, mas grande ser el chip. Y el costo de fabricacin del chip crece con mucha ms rapidez que su rea por esta razn los diseadores a menudo hablan del costo en trminos del rea requerida para un circuito.

Qu otra cosa podemos hacer para reducir la longitud de la trayectoria de ejecucin? Una solucin fcil es que la ALU tenga dos buses de entradas completos, un bus A y un bus B, para un total de tres buses, todos o casi todos los registros debern tener acceso a ambos buses de entradas. As se puede sumar dos registros en solo un ciclo y por lo tanto reduciremos la cantidad de ciclos en una instruccin. 2)Mejoramiento del desempeo Todos los fabricantes de computadoras quieren que sus sistemas operen con la mayor rapidez posible y los usuarios tambin buscan lo mismo. Las ideas que plantearemos se pueden clasificar en dos categoras: mejoras en la implementacin y mejoras en la arquitectura. Las mejoras en la implementacin son formas de construir una nueva CPU o memoria para hacer que el sistema opere ms rpidamente sin cambiar la arquitectura. Modificar la implementacin sin alterar la arquitectura implica que los programas viejos podrn ejecutarse en la nueva mquina, lo cual es un atractivo que eleva las ventas. Algunos tipos de mejoras solo pueden lograrse modificando la arquitectura. A veces tales cambios son incrementales, como aadir nuevas instrucciones o registros, de modo que los programas viejos puedan seguir funcionando en los modelos nuevos, pero debera existir una recompilacin en el software para aprovechar al mximo estas nuevas caractersticas. Mejora en la memoria cache: El considerable aumento en la velocidad de los procesadores a ltimas fechas no ha sido acompaado de un aumento correspondiente en la velocidad de las memorias. En comparacin con las CPU las memorias se han vuelto ms lentas desde hace dcadas. Dada a la enorme importancia de la memoria principal, esta situacin a limitado severamente el desarrollo de sistemas de alto desempeo, y ha estimulado investigaciones sobre formas de resolver este problema de

memorias, que son mucho ms lentas que los CPU problema que empeora cada vez ms al avanzar en trminos de velocidad el CPU. Los procesadores modernos someten a los sistemas de memoria a demandas abrumadoras, tanto en trminos de de latencia (lo que tarda en proporcionar un operando) como en ancho de banda (la cantidad de datos que se proporcionan por unidad de tiempo) lamentablemente estos dos aspectos de un sistema de memoria son en gran medida opuestos muchas tcnicas para aumentar el ancho de banda lo logran nicamente aumentando la latencia. Una forma de atacar este problema es incluir caches, un cache contiene las palabras de memoria que se usaron ms recientemente en una memoria pequea y rpida, con lo que se agiliza el acceso a ellas. Si un porcentaje suficientemente grande de las palabras de memoria que se necesitan estn en la cache la latencia de memoria efectiva se puede reducir enormemente. Una de las tcnicas ms eficaces para mejorar tanto el ancho de banda como la latencia se basa en el empleo de mltiples cachs. Una tcnica fundamental que resulta muy eficaz es introducir cachs individuales para instrucciones y para datos, lo que se conoce como cach dividida. Esto tiene varias ventajas. Primero las operaciones de memoria se pueden iniciar de forma independiente en cada cach lo que duplica efectivamente el ancho de banda del sistema de memoria. Esta es la razn por la que conviene tener dos puertos de memorias distintos, cabe sealar que cada cach tiene acceso independientemente a la memoria principal. Las caches dependen de dos tipos de direcciones para lograr su objetivo. Localidad espacial es la observacin de que es probable que en el futuro cercano se acceda a localidades de memorias con direcciones numricamente similares a una localidad de memoria a la que se accedi recientemente. Las caches aprovechan esta propiedad trayendo ms datos de lo que se solicitaron con la expectativa de anticipar solicitudes futuras. Ocurre localidad temporal cuando se

vuelven a acceder a localidades de memorias a las que se accedi recientemente. Esto puede ocurrir por ejemplo, con localidades de memorias cercanas al tope de la pila, o instruccin dentro de un ciclo. La localidad temporal se aprovecha primordialmente en los diseos de cach al tomar la decisin de que debe desecharse cuando no se encuentra algo en ella (fallo de cach). Muchos algoritmos de remplazo de cach aprovechan la localidad temporal desechando las entradas a las que no se han accedido recientemente. Prediccin de ramificaciones: Predice el flujo del programa a travs de varias ramificaciones, mediante un algoritmo de prediccin de ramificaciones mltiples, el procesador puede anticipar los saltos en el flujo de las instrucciones. ste predice dnde pueden encontrarse las siguientes instrucciones en la memoria con una increble precisin del 90% o mayor. Esto es posible porque mientras el procesador est buscando y trayendo instrucciones, tambin busca las instrucciones que estn ms adelante en el programa. Esta tcnica acelera el flujo de trabajo enviado al procesador. Ejecucin fuera de orden y cambio de nombres de registros: Es un paradigma utilizado en la mayora de los microprocesadores de alto rendimiento como forma de aprovechar los ciclos de instruccin que de otro modo seran desperdiciados producindose cierta demora de trabajo. Gran parte de los diseos modernos de CPU soportan la ejecucin fuera de orden. Procesadores fuera de orden Este nuevo paradigma rompe con lo anterior basndose en el siguiente orden: 1. Captura de la instruccin. 2. Envo de la instruccin a una cola (tambin llamada buffer o estacin de reserva).

3. La instruccin espera en cola hasta que los operandos de entrada estn disponibles, de manera que una instruccin ms reciente puede abandonar el buffer antes que otra anterior si ya tiene los datos disponibles. 4. La instruccin es enviada a la correspondiente unidad funcional, que la ejecuta. 5. Se enva el resultado a cola. 6. La instruccin en curso solamente puede escribir en el archivo de registros una vez que todas las anteriores a ella hayan escrito sus correspondientes resultados. La idea clave de la fuera de orden consiste es permitir al procesador evitar ciertos tipos de burbuja que suceden cuando la informacin necesaria para realizar una operacin no est disponible. Siguiendo los pasos antes explicados, el procesador fuera de orden evita las burbujas comentadas en el paso 2 de la ejecucin en orden cuando la instruccin no se puede completar a causa de la falta de datos. Los procesadores con ejecucin fuera de orden rellenan esos "huecos" de tiempo con instrucciones que s estn listas para ejecutarse para despus reordenar los resultados y aparentar que fueron procesadas de manera normal. La forma en que las instrucciones son ordenadas en el cdigo original a ejecutar se conoce como orden de programa, mientras que el orden en que el procesador las maneja es el orden de datos, siendo aquel en que los datos van quedando disponibles para su captura desde los registros del procesador. Se necesita una circuitera bastante compleja para convertir un orden en otro y poder adems mantener el orden lgico de la salida; el propio procesador ejecuta las instrucciones de forma aparentemente aleatoria. Los beneficios del procesamiento de ejecucin fuera de orden crecen a medida que se profundiza en la segmentacin, as como con el crecimiento de la

diferencia de velocidades entre la memoria principal (o memoria cache) y el procesador. En las mquinas modernas, el procesador funciona a velocidades mucho mayores que la memoria, de modo que mientras un procesador en orden pierde tiempo esperando por los datos, uno con ejecucin fuera de orden ya habra procesado un gran nmero de instruccin. Ejecucin especulativa: Es la ejecucin de cdigo por parte del procesador que no tiene por qu ser necesaria a prioridad. En la programacin funcional, suele usarse el trmino "evaluacin especulativa". La ejecucin especulativa no es ms que una optimizacin. Obviamente, slo es til cuando la ejecucin previa requiere menos tiempo y espacio que el que requerira la ejecucin posterior, siendo este ahorro lo suficientemente importante como para compensar el esfuerzo gastado en caso de que el resultado de la operacin nunca llegue a usarse. 3) Ejemplo de nivel de microarquitectura: Microarquitectura Intel Nombre en Cdigo Nehalem La microarquitectura de nueva generacin de Intel, que se demostr por primera vez con el procesador Intel Core i7, representa el siguiente nivel de tecnologa multi-core ms rpida que maximiza con inteligencia el desempeo segn sus necesidades de trabajo. La microarquitectura Intel nombre en cdigo Nehalem, que se ha diseado desde el principio para aprovechar las ventajas de la microarquitectura Intel Core Hi-k de 45nm de prxima generacin, ofrece el desempeo para procesamiento paralelo mediante un controlador de memoria

integrado y Intel QuickPath Technology que brinda interconexiones de alta velocidad por cada ncleo de procesamiento independiente. El siguiente nivel del desempeo multi-core La microarquitectura Intel, nombre en cdigo Nehalem, ofrece la mxima innovacin en procesadores y se distingue por lo siguiente:

Escalabilidad dinmica, ncleos administrables, subprocesos, cach, interfaces y alimentacin de energa para el desempeo ecolgico a pedido. Escalabilidad del diseo y desempeo para servidores, estaciones de trabajos, laptops y PCs compatible con dos y ms de ocho ncleos, y hasta ms de 16 subprocesos mediante Intel Hyper-Threading Technology (Intel HT Technology), as como tamaos de cach escalables, interconexiones del sistema y controladores de memoria integrados.

Desempeo inteligente a pedido con Intel Turbo Boost Technology que saca provecho de la energa y el margen trmico del procesador. Gracias a estas tecnologas se aumenta el desempeo para las cargas de trabajo que ejecutan uno o varios subprocesos.

Mayor desempeo en las aplicaciones muy sofisticadas mediante Intel HT Technology, que integra las aplicaciones de alto desempeo en la informtica de uso general con 1 y ms de 16 subprocesos optimizados para la arquitectura de procesadores multi-core de nueva generacin.

Memoria compartida escalable que se distribuye entre cada procesador con los controladores de memoria integrados y las interconexiones de punto a punto de alta velocidad de Intel QuickPath Technology a fin de dar rienda suelta al desempeo de las futuras versiones de los procesadores Intel multi-core de prxima generacin.

Cach compartida a multinivel que aumenta el desempeo y la eficacia al reducir la latencia de acceso a los datos ms utilizados.

Вам также может понравиться

- Administracion de MemoriaДокумент58 страницAdministracion de MemoriaDaniel Omar GarciaОценок пока нет

- Modelos de Arquitecturas de ComputadorasДокумент7 страницModelos de Arquitecturas de ComputadorasAmsydarkJadeОценок пока нет

- Ensayo Sobre Modelos de Arquitectura de ComputadorasДокумент5 страницEnsayo Sobre Modelos de Arquitectura de ComputadorasAldair Cruz BautistaОценок пока нет

- Jimenez Taller3 MicroPДокумент3 страницыJimenez Taller3 MicroPCamilo Jimenez GОценок пока нет

- Arquitecturas ClásicasДокумент11 страницArquitecturas ClásicasGiovani ArellanoОценок пока нет

- Funciones y Operaciones Del Administrador de MemoriaДокумент46 страницFunciones y Operaciones Del Administrador de MemoriaOberto Jorge Santín CuestaОценок пока нет

- Capitulo 2. Fundamentos TeoricosДокумент22 страницыCapitulo 2. Fundamentos Teoricosalienarandas123Оценок пока нет

- Tipos de ModelosДокумент19 страницTipos de ModelosWicho FloresОценок пока нет

- Arquitectura de ComputadorasДокумент8 страницArquitectura de ComputadorasSorel TorresОценок пока нет

- Montaje y Mantenimiento 1º EjerciciosДокумент3 страницыMontaje y Mantenimiento 1º EjerciciosChristian46RMОценок пока нет

- Ciclo InstruccionДокумент4 страницыCiclo InstruccionFacundoОценок пока нет

- Memoria CachéДокумент12 страницMemoria Cachécarmen diazОценок пока нет

- Modelos de Arquitecturas de Cómputo.Документ7 страницModelos de Arquitecturas de Cómputo.CAAMAL CARLOS ALBERTOОценок пока нет

- MulticoreДокумент25 страницMulticoreMario EnriqueОценок пока нет

- Arquitectura de ComputadorasДокумент47 страницArquitectura de ComputadorasRigoberto He HeОценок пока нет

- Dpso U1 A2 MaghДокумент11 страницDpso U1 A2 MaghMario Ezequiel Garcia HuertaОценок пока нет

- Arquitectura de ComputadorasДокумент53 страницыArquitectura de Computadorastilsma100% (3)

- Gonzalez Ibarra Reporte ArquitecturaДокумент11 страницGonzalez Ibarra Reporte ArquitecturaCarolina GonzalezОценок пока нет

- Arquitecturas de ComputoДокумент34 страницыArquitecturas de ComputoStephanie Martinez100% (1)

- Memoria Compartida Distribuida PDFДокумент22 страницыMemoria Compartida Distribuida PDFMarcos Julián GaliciaОценок пока нет

- Unidad 1 Modelo de Arquitecturas de CómputoДокумент37 страницUnidad 1 Modelo de Arquitecturas de CómputoRosario Ramírez Rios100% (1)

- Exp No 5 Arquitectura Del ProcesadorДокумент32 страницыExp No 5 Arquitectura Del ProcesadorRichy PlonedaОценок пока нет

- Multiprocesamiento, Procesamiento Vectorial y Paralelotura ComputadorДокумент12 страницMultiprocesamiento, Procesamiento Vectorial y Paralelotura ComputadorKevin EnriquezОценок пока нет

- Deber Primer BimestreДокумент9 страницDeber Primer BimestrenetoqvОценок пока нет

- Significado de Los Términos CISC y RISCДокумент8 страницSignificado de Los Términos CISC y RISCRandy EstradaОценок пока нет

- Investigacion - Aspectos de Diseño Sobre Dispositivos de Entrada Salida PDFДокумент13 страницInvestigacion - Aspectos de Diseño Sobre Dispositivos de Entrada Salida PDFraza binaria0% (2)

- Apunte - Administraci N de Memoria Central y T ®cnicas de Administraci N de Memoria OKДокумент81 страницаApunte - Administraci N de Memoria Central y T ®cnicas de Administraci N de Memoria OKelian.tamarillaОценок пока нет

- Arquitectura Harvard - FinalДокумент10 страницArquitectura Harvard - FinalOrlandoОценок пока нет

- Tipos de ParalelismoДокумент10 страницTipos de ParalelismoPablo JonasОценок пока нет

- Arquitectura de Computadoras y Modelos de ArquitecturasДокумент15 страницArquitectura de Computadoras y Modelos de ArquitecturasPabloGomezPerezОценок пока нет

- TP 2016-1 333Документ31 страницаTP 2016-1 333Anabell LaresОценок пока нет

- Enciso Luna Cristian Gerardo Isc 19400563Документ5 страницEnciso Luna Cristian Gerardo Isc 19400563Cristian Gerardo Enciso LunaОценок пока нет

- Respuesta A Ejercicios LibrosДокумент14 страницRespuesta A Ejercicios LibrosPIOОценок пока нет

- Ciclo de InstrucciónДокумент7 страницCiclo de InstrucciónSandy TomalaОценок пока нет

- Resumen 5 EdsonДокумент13 страницResumen 5 EdsonEdgar Pando Flores100% (2)

- Antologia de Arquitectura de ComputadorasДокумент95 страницAntologia de Arquitectura de ComputadorasCésar Vicente Morales MoralesОценок пока нет

- Unidad 3 Arquitectura Del ComputadorДокумент8 страницUnidad 3 Arquitectura Del ComputadorApolloSiriОценок пока нет

- Arquitectura VonmewmanДокумент4 страницыArquitectura VonmewmanSorely ReyesОценок пока нет

- Sistemas Operativos - Silberschatz GalvinДокумент457 страницSistemas Operativos - Silberschatz GalvinEduardo Velásquez Alarcón100% (1)

- Arquitectura ParalelaДокумент41 страницаArquitectura ParalelaLexer ParsОценок пока нет

- Elementos Básicos de Un Procesador ModernoДокумент5 страницElementos Básicos de Un Procesador ModernoivanadstОценок пока нет

- Arquitectura CISC y RISCДокумент10 страницArquitectura CISC y RISCWilliams Alexander Trias AscanioОценок пока нет

- Plantilla Aqr ComputadorasДокумент4 страницыPlantilla Aqr Computadorasniki mejiaОценок пока нет

- Trabajo Practico Nº3 de Sistemas Operativos IIДокумент42 страницыTrabajo Practico Nº3 de Sistemas Operativos IICamila ToledoОценок пока нет

- Ensayo Del Libro Abraham Silberschatz Cap 8Документ8 страницEnsayo Del Libro Abraham Silberschatz Cap 8Danilo MoralesОценок пока нет

- Memoria VirtualДокумент46 страницMemoria VirtualTrabalhoNaoseiОценок пока нет

- TEORIA - PreguntasComunesДокумент33 страницыTEORIA - PreguntasComunesRichard AvilésОценок пока нет

- Introduccion Risc y CiscДокумент7 страницIntroduccion Risc y CiscAldo ReignОценок пока нет

- Capítulo 4 - Gestion de Memoria VirtualДокумент21 страницаCapítulo 4 - Gestion de Memoria VirtualPablo Cesar Medina BarretoОценок пока нет

- Explique en Que Consisten Los Cuatro Estados BásicosДокумент30 страницExplique en Que Consisten Los Cuatro Estados BásicosMARIA NANCYОценок пока нет

- Metodo de Distribucion de CargaДокумент69 страницMetodo de Distribucion de Cargaeduardo100% (1)

- Qué Es MEMORIA - OrganizedДокумент11 страницQué Es MEMORIA - OrganizedDannyMárquezОценок пока нет

- Multiprogramación e HilosДокумент24 страницыMultiprogramación e HilosWilian Eduardo Soch TzulОценок пока нет

- Buses Interrupciones Estructura y FuncioДокумент5 страницBuses Interrupciones Estructura y Funciochristian mendozaОценок пока нет

- Administración de MemoriaДокумент5 страницAdministración de MemoriaDaniaLamasОценок пока нет

- Antologia de Arquitectura de ComputadorasДокумент95 страницAntologia de Arquitectura de ComputadorasCésar Vicente Morales Morales100% (1)

- Ejercicio Memoria Parte A S. Reyes 21-Sisn-1-004Документ7 страницEjercicio Memoria Parte A S. Reyes 21-Sisn-1-004sergio reyesОценок пока нет

- Tarea Sistemas DigitalesДокумент3 страницыTarea Sistemas Digitalesluis piscoyaОценок пока нет

- UF0852 - Instalación y actualización de sistemas operativosОт EverandUF0852 - Instalación y actualización de sistemas operativosРейтинг: 5 из 5 звезд5/5 (1)

- Tecnicas de Psicología EnergéticaДокумент28 страницTecnicas de Psicología EnergéticaJosan Fernández75% (4)

- De Forero, N. M. (1992) - Rol de La Enfermera en La Actualidad Deportiva Del Escolar. Avances en Enfermería, 10 (2), 53-62.Документ10 страницDe Forero, N. M. (1992) - Rol de La Enfermera en La Actualidad Deportiva Del Escolar. Avances en Enfermería, 10 (2), 53-62.Al Yarimi MartinezОценок пока нет

- Artículo Especial: Ultrasonido Básico y Anestesia Regional. Accesos Más ImportantesДокумент9 страницArtículo Especial: Ultrasonido Básico y Anestesia Regional. Accesos Más ImportantesJuliana ObandoОценок пока нет

- Aplicaciones en La SaludДокумент3 страницыAplicaciones en La SaludJhosue MundacaОценок пока нет

- Reflexiones Sobre El Hecho EducativoДокумент4 страницыReflexiones Sobre El Hecho Educativoexxedd91% (11)

- Columnas de Anexina PDFДокумент2 страницыColumnas de Anexina PDFSinquefieldОценок пока нет

- Resumen Explicativo de La Adultez Emergente. Unidad 5Документ5 страницResumen Explicativo de La Adultez Emergente. Unidad 5Inés SánchezОценок пока нет

- POD 138 InstrДокумент1 страницаPOD 138 InstrgpocobosОценок пока нет

- La Ortografía, Pandemia Escolar Sin SoluciónДокумент19 страницLa Ortografía, Pandemia Escolar Sin SoluciónMaríaAbrigoОценок пока нет

- Sanacion Del Utero Con Hierbas PDF 20Документ13 страницSanacion Del Utero Con Hierbas PDF 20martin luceroОценок пока нет

- Arquitectura de Computadores Promera EntregaДокумент5 страницArquitectura de Computadores Promera EntregaJOSE SAMUEL VARGAS DAZAОценок пока нет

- Manual El Tarot GeometricoДокумент24 страницыManual El Tarot GeometricoVela MagiaОценок пока нет

- Guia David Segundo CicloДокумент2 страницыGuia David Segundo CicloDannit CifuentesОценок пока нет

- Segundo Material de Derecho RomanoДокумент34 страницыSegundo Material de Derecho RomanoHeidy AjuchanОценок пока нет

- Practica de Tecnologia EducativaДокумент5 страницPractica de Tecnologia EducativaElaineОценок пока нет

- Elementos Basicos de Las ComprasДокумент3 страницыElementos Basicos de Las ComprasmariaОценок пока нет

- Resolución 462 2017Документ10 страницResolución 462 2017JaimColVОценок пока нет

- CALCULOS de TolvaДокумент6 страницCALCULOS de TolvapaulОценок пока нет

- 5312 - Proyecto-Plan-De-Desarrollo-Territorial PUEBLO BELLOДокумент154 страницы5312 - Proyecto-Plan-De-Desarrollo-Territorial PUEBLO BELLOmalejavargasvega81Оценок пока нет

- Exp8 Ebr Secundaria 1y2 Seguimosaprendiendo Tutori Actividad1Документ7 страницExp8 Ebr Secundaria 1y2 Seguimosaprendiendo Tutori Actividad1Zulaidy Esthefanie EDОценок пока нет

- Sociedades Cazadoras y Recolectora PaleolíticoДокумент3 страницыSociedades Cazadoras y Recolectora PaleolíticoALEJANDRO GUAGUAОценок пока нет

- Ejercicios de CompresoresДокумент1 страницаEjercicios de Compresoresraaq2310Оценок пока нет

- Algunos Apuntes y Reflexiones Acerca Del Cuerpo y La CorporeidadДокумент4 страницыAlgunos Apuntes y Reflexiones Acerca Del Cuerpo y La CorporeidadDebora AzarОценок пока нет

- Discontinuidades en El MRДокумент16 страницDiscontinuidades en El MREmmanuel García MunguíaОценок пока нет

- Planificación Digital DOCENTEДокумент41 страницаPlanificación Digital DOCENTEJeremy Brown100% (1)

- USC Gestion AmbientalДокумент16 страницUSC Gestion AmbientalxGavo 69Оценок пока нет

- Tema 4 - HERRAMIENTAS DE INTELIGENCIA ARTIFICIALДокумент25 страницTema 4 - HERRAMIENTAS DE INTELIGENCIA ARTIFICIALDiego EscobarОценок пока нет

- Resumen de La ISO 45001 - Fernanda SánchezДокумент3 страницыResumen de La ISO 45001 - Fernanda SánchezJennifer Valencia MorenoОценок пока нет

- Fenomeno Del Niño CosteroДокумент4 страницыFenomeno Del Niño CosteroCinthya TCОценок пока нет

- Tipos de BiopsiasДокумент6 страницTipos de BiopsiasKevin Carranza VillaoОценок пока нет