Академический Документы

Профессиональный Документы

Культура Документы

Versatile PWM Controller: Features Description

Загружено:

Milorad PaunovicИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Versatile PWM Controller: Features Description

Загружено:

Milorad PaunovicАвторское право:

Доступные форматы

www.fairchildsemi.

com

FAN7554

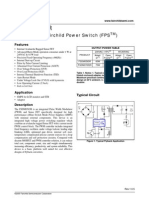

Versatile PWM Controller

Features

Current Mode Control Pulse by pulse current limiting Low external components Lowest cost SMPS solution Under-Voltage Lockout( UVLO): 9V/15V Stand-by Current: Typ. 100uA Power Saving Mode Current: Typ. 200uA Operating Current: Typ. 7mA Soft start On/Off control Over Load Protection(OLP) Over Voltage Protection(OVP) Over Current Protection(OCP) Over Current Limit(OCL) Operating Frequency up to 500kHz 1A Totem-pole Output Current

Description

FAN7554 is fixed frequency current-mode PWM controller. It is specially designed for off-line and DC-to-DC converter applications with minimal external components. These integrated circuits feature a trimmed oscillator for precise duty cycle control, a temperature compensated reference, high gain error amplifier, current sensing comparator, and a high current totempole output. Ideally suited for driving a power MOSFET. In addition to the general protection function of PWM IC, FAN7554 has various protection function such as Over Load Protection, Over Current Protection, Over Voltage Protection, which include Built-in auto-restart circuit, and Over Current Latch. Moreover, it corporates on-off control circuit and soft start circuit. It also offer low power consumption is stand-by condition.

8-DIP

Applications

Off-Line & DC-DC Converter

1

8-SOP

Rev. 5.0

2000 Fairchild Semiconductor International

FAN7554

Internal Block Diagram

Rt/Ct 4

+ 1k 0.3V + 1.5V OSC CLK S Q R 14V +

2R

Vref 8

OVP +

Vcc 7

3.5V

S Q

R off PWR / SAVE

34V

Vref 100uA

Vref

UVLO + 15V/9V

S/S

on

6 FB 1

1mA Vref Offset(0.1V) Vcc 5uA + 6V OLP OVP-out OCL-out UVLO-out S Q R OCL + 2V

MAX. 1V

OUT

PWM

IS

5 GND

Absolute Maximum Ratings

( Ta = 25C, unless otherwise specified ) Parameter Supply Voltage Output Current Input Voltage to FB Pin Input Voltage to IS Pin Power Dissipation Operating Temperature Storage Temperature Symbol Vcc IO VFB VIS PD TOPR TSTG Value 30 1 -0.3 to VSD -0.3 to VOC 1 -25 to +85 -55 to + 150 Unit V A V V W C C

Temperature Characteristics

( -25C Ta 85C ) Parameter Vref Temperature Stability Fosc Temperature Stability Symbol VREF3 FOSC2 Value 0.5 5 Unit % %

FAN7554

PIN Array

Vref Vcc OUT GND

YWW FA N7554

1

FB

2

S/S

3

IS

4

Rt/Ct

PIN Definitions

Pin Number 1 2 3 4 5 6 7 8 Pin Name FB S/S IS Rt/Ct GND OUT Vcc Vref Pin Function Descrition Inverting(-) Input of PWM Comparator, On/Off Control & OLP Sensing Terminal. Soft Start Non-Inverting(+) Input of PWM Comparator, OCL Sensing Terminal Oscillator Time Constant(Rt/Ct) Ground Output of gate Driver Power Supply Output of 5V Reference(Max. 100mA)

FAN7554

Electrical Characteristics

( Refer to circuit Ta = 25C, Vcc=16V, Rt=10k, Ct=3.3nF unless otherwise specified ) Parameter < REFERENCE SECTION > Reference Output Voltage Line Regulation Load Regulation Short Circuit Output Current < OSCILLATOR SECTION > Oscillation Frequency Frequency Change with Vcc Ramp High Voltage Ramp Low Voltage < PWM SECTION > Sense Threshold Voltage(Vocp) Feedback Threshold Voltage Feedback Source Current Max. Duty Cycle Min. Duty Cycle < PROTECTION SECTION > Shutdown Delay Current Shutdown Feedback Voltage Over Current Latch Protection Over Voltage Protection < ON/OFF CONTROL SECTION > Off Mode Sink Current Off Threshold Voltage < SOFT-START SECTION > Soft Start Current Soft Start Limit Voltage <OUTPUT SECTION> Low Output Voltage1 High Output Voltage1 Low Output Voltage2 High Output Voltage2 Rising Time Falling Time <UVLO SECTION> Start Threshold Voltage Min. Operating Voltage VTH(ST) VOPR(M) 13.2 8.2 15 9 16.2 10.2 V V VOL1 VOH1 VOL2 VOH2 tR tF Io = 50mA Io = 50mA Io = 200mA Vcc=18V, Io=200mA Tj=25C, CL = 1nF Tj=25C, CL = 1nF 13 12 0.15 15 1.5 14 80 40 0.4 17 2.5 16 V V V V nS nS IS/S VLIM(S/S) VFB = 5V, VS/S = 0V Vcc = 16V 1.1 5.2 mA V ISINK VOFF VFB < VTH(FB), VS/S = 5V VFB < VTH(FB) 1.2 4 1.5 1.8 mA V ISD VSD VOC VOVP 4V VFB VSD VFB > 5V VIS > 1.5V, ton > 500nS 3.5 5.4 1.6 30 5 6 2 34 6.5 6.6 2.4 38 uA V V V VTH(IS) VTH(FB) IFB D(MAX) D(MIN) VFB =5V VIS =0V VFB = 0V, VS/S = 5V 0.8 0.2 92 1.0 0.3 1.0 95 1.2 0.4 98 0 V V mA % % FOSC FOSC1 VRH VRL Tj=25C Vcc=12V~25V 45 50 0.05 2.8 1.2 55 1.0 kHz % V V VREF VREF1 VREF2 ISC Tj=25C , Iref=1mA Vcc=12V~25V Iref=1mA~20mA Tj=25C 4.90 5.00 6 6 0.1 5.10 20 25 0.18 V mV mV A Symbol Conditions Min. Typ. Max. Unit

FAN7554

Electrical Characteristics (Continued)

( Refer to circuit Ta = 25C, Vcc=16V, Rt=10k, Ct=3.3nF unless otherwise specified ) Parameter Start-up Current Operating Supply Current Off State Current Symbol IST IOP IOFF Vcc = 14V Vcc 30V Vcc=14V,VFB<VTH(FB),VS/S<VOF Conditions Min. Typ. 0.1 7 0.2 Max. 0.2 10 0.4 Unit mA mA mA

<TOTAL STANDBY CURRENT SECTION>

FAN7554

Typical Perfomance Characteristics

[ Rt vs. Freqency ] 10000.0

100.000 [ Ct vs Dead time ]

1000.0

Dead Time [usec]

Frequency[kHz]

100.0

10.0

0.33n 1.1n 3.3n 11n 33n

10.000 1K 2K 5K 10K 20K 50K 100K

1.000

1.0

0.1 1 10 Rt[Kohm] 100

0.100 0.1 1 Ct[nF] 10 100

Figure 1. Rt vs Frequency

[ Ct vs Duty ]

800

Figure 2. Ct vs Dead Time

[ Cload vs Tr & Tf ] 50Khz,95% duty

95.0

700

85.0 75.0 Duty [%] 65.0 55.0 45.0 35.0 25.0 15.0 0.1 1 Ct [nF] 10 100 1K 2K 5K 10K 20K 50K 100K

600 Time [nsec] 500 400 300 200 100 0 1 10 Cload [ nF] 100 Tr Tf

Figure 3. Ct vs Duty

Figure 4. Cload vs Tr & Tf

FAN7554

Typical Perfomance Characteristics(Continued)

tem p. vs Ist 0.120 0.110 Ist [mA] 0.100 0.090 0.080 0.070

-25 0 25 tem p [ ] 50 75

tem p. vs [ Ist / (Ist at 25 ) ] 1.15 1.10 1.05 1.00 0.95 0.90

-25

25 tem p [ ]

50

75

Figure 1. Temperature vs lst (at 25C)

tem p. vs [ Iop / (Iop at 25 ) ] 1.04

Figure 2. Temperature vs lst

tem p. vs Iop 7.30 Iop [mA] 7.10 6.90 6.70 6.50

1.02 1.00 0.98 0.96 -25 0 25 tem p [ ] 50 75

-25

25 tem p [ ]

50

75

Figure 3. Temperature vs lop (at 25C)

tem p. vs [ Vref / (V ref / Vref at 25 ) ]

Figure 4. Temperature vs lop

tem p. vs Vref 4.938

1.002

Vref [V]

1.001 1.000 0.999 0.998 -25 0 25 tem p. [ ] 50 75

4.936 4.934 4.932 4.930 -25 0 25 tem p. [ ] 50 75

Figure 5. Temperature vs Vref (at 25C)

Figure 6. Temperature vs Vref

FAN7554

Typical Perfomance Characteristics(Continued)

tem p. vs [ F osc / ( Fosc at 25 ) ] 1.060

tem p. vs Fosc 56.00 Fosc [kHz] 55.00 54.00 53.00 52.00

1.040 1.020 1.000 0.980 0.960 -25 0 25 tem p [ ] 50 75

-25

25 tem p [ ]

50

75

Figure 7.Temperature vs Fosc(at 25C)

tem p. vs norm a lized Vth(st) 1.020

Figure 8. Temperature vs Fosc

tem p. vs Vth(st) 15.20 Vth(st) [V] 15.00 14.80 14.60 14.40

1.010 1.000 0.990 0.980 -25 0 25 tem p. [ ] 50 75

-25

25 tem p. [ ]

50

75

Figure 9. Temperature vs Norm Alized Vth(st)

tem p. vs norm a lized Vop r(m in) 1.002 1.001 1.000 0.999 0.998 -25 0 25 tem p. [ ] 50 75

Figure 10. Temperature vs Vth(st)

tem p. vs Vopr(m in) 9.31 Vopr(min) [V] 9.30 9.29 9.28 9.27 -25 0 25 tem p. [ ] 50 75

Figure 11. Temperature vs Alized Vopr(min)

Figure 12. Temperature vs Vopr(min)

FAN7554

Operation Description

FAN7554 has all the basic features of the current mode SMPS control IC. Furthermore, as a PWM (Pulse Width Modulation) control IC, FAN7554 modulates the pulse width by comparing the input current sense voltage level to the feedback voltage level. Its basic configuration includes a UVLO with 6V hysteresis, 5V bandgap reference, low start-up current, oscillator that can oscillate up to 500KHz depending on Rt/Ct (connected externally), PWM logic circuit , MOSFET gate drive, feedback circuit that has the current source and soft start function. Its protection circuit has delayed shutdown and over current shutdown functions. Of the two protection functions, the delayed shutdown forces the IC to charge the feedback capacitor Cfb with current source in the IC for the additional delay time if there is an error or overload from a system feedback loop failure or if there is a transient state. Then it forces a system shutdown after a specified time. Then a MOSFET breakdown etc. causes over current to flow. The over current shutdown is the protection function that stops all of control operations to protect the IC and system. As an Auto-restart circuit, the shutdown circuit resets when Vcc becomes less than the under voltage. Start-Up Start-Up circuit drives the FAN7554 IC using the low start up current. It is made up of the Under Voltage Lock Out (UVLO), the protection for low voltage conditions, and a 5V reference (Vref), which supplies Bias voltage to the Control Circuit , after Start Threshold Voltage. The Starting voltage of the UVLO is 15V , and the minimum voltage after turn on is 9V. It has a 6V hysteresis. The minimum operating current for start up threshold is typically 100uA, and this can minimize the power loss from the starting resistor. Vref is designed with the bandgap reference circuit with its superior temperature characteristics and supplies power to all FAN7554 circuits and Rt/Ct, with the exceptions of the ULVO circuit and ON/OFF control circuit. Furthermore, as for the Good Logic block, it either makes the output drive in low or discharges the soft start capacitor or feedback capacitor.

VDD UVLO

Vref

ICC [mA]

SV Vref

Internal Bias Good Logic

7.0

0.01

15V/9V

Figure 1. Low Current Start-Up & Bandgap Reference Circuit

9V

16V

VCC [V]

Figure 2. Start-Up & Circuit Characteristics

Soft Start The SMPS output load usually contains a capacitive load component. During initial start up, the output voltage increases at a fixed time constant because of this component. If the feedback loop, which controls the output voltage, was to start without the soft start circuit, the feedback loop would appear to be open during initial startup , and This would drive the voltage in feedback pin up to 1V as a maximum voltage. During this time, the peak value of the drain current would stay at the maximum value, and the maximum power would be delivered to the secondary load side from the start. If maximum power was supplied to the secondary side at start for a fixed time in the SMPS, this can put severe stress on the entire circuit to prevent such a case, the soft start function is needed and included in this control system. At start up, the soft start capacitor Cs is charged with 1mA and 100uA current sources. The voltage of the inverting terminal of the PWM comparator increases to 1/3 of the Cs voltage at a fixed time constant. Subsequently, the drain peak current is limited by the gradual increase in the Cs voltage and this causes the output voltage to increase smoothly. When the Cs voltage becomes greater than 3V, diode Ds turns off and the inverting terminal voltage becomes no longer a function of the Cs voltage but of the feedback signal. Then, Cs voltage charges to 5V using 100uA. The soft start capacitor Cs is discharged when the UVLO Good Logic starts, so soft start is repeated at re-start.

FAN7554

SO FT SOFT START STA RT 100uA 5V Ds 2R PW M PWM

1mA 1m A

CCs s Cb f 5uA 5V V cc 1 FB

LOGIC LO I C G

V f of

[Soft Start Circuit & Circuit Flow]

Figure 3. Soft Start Circuit & Circuit Flow

Oscillator The oscillator frequency is programmed by values selected for timing components Rt and Ct. Capacitor Ct is charged to almost 2.8V through resistor Rt from the 5V reference and discharged to 1.2V by the current sink. The oscillator generates the clock signal during the timing capacitor's Ct discharge. The gate drive output becomes low during the clock time. Rt and Ct selections determines the oscillator frequency and maximum duty cycle. Charge and discharge times can be calculated through the equations below. Charging time : tc = 0.55RtCt Discharging time : td = RtCtln[(0.0063Rt - 2.7) / (0.0063Rt - 4.0)] where the oscillator frequency : fosc = (tc + td)-1 When Rt > 5K, fosc = 1 / (0.55RtCt) = 1.8 / (RtCt) FAN7554 has almost 100% maximum duty cycle. This duty cycle clamp is useful generally in the flyback or forward converter. To optimize the device's performance, the external clock signal blanks the output to low during deadtime. This limits the maximum duty cycle. Dmax = tc / (tc + td)

Vr e f

Vhi gh ( 2. Vhigh (2.8V) 8V) Sawtooth waveform s awt oot h wave f or m

Rt Rt / Ct 4

Vlow (1.2V)

+

[ Rt > 5 ]

Vl ow ( 1. 2V)

Clock Cl oc k Gatee Drive Ga t Dr i ve

i nt e r na l cl oc k

internal clock Vhigh (2.8V)

Vhi gh ( 2. 8V)

ttc

t td

d

Ct Ct

sw

Discharge Di s c ha r ge

2. 8V / 1. 2V

Sawtooth h wave f or m waveform s awt oot Vlow (1.2V) Vl ow ( 1. 2V)

i internal clock nt e r na l cl oc k

[ Rt << 5 ]

ttc

c

ttd

d

[ Oscillator Circuit ]

[Sawtooth & Clock Waveform]

Figure 4. Oscillator Circuit

Figure 5. Sawtooth & Clock Waveform

10

FAN7554

Feedback The feedback section can control the feedback voltage and execute delayed shutdown simultaneously. The error voltage fed back from the secondary side output voltage and the voltage sensed by the MOSFET sense terminal are compared to drive the gate and modulate the pulse width to control output voltage. For normal operation, the feedback voltage is between 0~3V and, when it is 3V, the MOSFET drain current is maximum. During normal operation, the feedback capacitor is charged through the internally designed current sources, 1mA and 5uA, and is then discharged to the secondary side photo-coupler to control the output voltage.

FB

OSC O SC C1 D 1

Clock Cl ock

G e at Gate D i ve r Drive

DRAIN D IN RA

O ut 6

2R 1m A R + S R

IS Cf b 5uA 5V V cc V f of 3 Rs

[Feedback Feedback &Circuit ] Figure 6. & PWM PWM Circuit

Delayed Shutdown When the feedback loop is operating normally, the feedback voltage remains between 0~3V. If the load at the output terminal overloads or an error develops in the feedback loop, the delayed shutdown circuit starts. If the abnormal state, which feedback capacitor discharge is stopped by the photo-coupler, the delayed shutdown circuit converts to the charging mode. When the feedback voltage is less than 3V, the feedback capacitor is charged through 1mA and 5uA; when the feedback voltage becomes greater than 3V, the capacitor is charged through 5uA because diode D1 turns off. When the feedback voltage is less than 3V, the charge slope becomes an exponential function due to the IC internal resistance, and, greater than 3V, the charge slope becomes linear. When the feedback voltage reaches almost 6V, the delayed shutdown with the latch circuit shutsvdown the IC. The shutdown circuit is configured for auto-restart, so it automatically restarts when when Vcc reaches the under voltage 9V.

FB os c D1 D2 2R -

Clock

Cl oc k

Gate Dr i ve Drive

Ga t e

DRAI N DRAIN Out 6

S R

( X) 1m A Cf b 5uA 5V Vc c + 6V

+ IS Vof f 3 Rs

S R Ove r Cur r e nt Over t or Com r aCurrent pa UVLO Out

Shut down Si gna l

Comparator

Figure 7-A . Delayed Shutdown & Feedback Circuit

11

FAN7554

Vfb 6V

Slope(dv/dt)= 5uA / Cfb

Shutdown Start Point 3V

t1

t2

[D elayed Shutdow n & Feedback W aveform ]

Figure 7-B . Delayed Shutdown & Feedback Waveform

Gate Driver Gate Drive circuit has the Totem-Pole Output configuration. The output has 1A Peak Current and 200mA Average Current drive ability.

Vcc

Clock Vz Q Out 6

DRAIN

Shutdown

Figure 8. Gate Drive Circuit

[Gate Drive Circuit ]

ON/OFF Control The FAN7554 does not have a pin specifically for ON/Off control but is able to use the feedback pin without extra components for on-off control. When the circuit control unit sends the off signal, the current is forced to flow to the photo-coupler diode, completely saturating the photo-coupler transistor. As a result, the feedback voltage discharges through the transistor. When the feedback voltage becomes less than 0.3V, the soft start pin voltage can be droppecl depending on the internal 1K resistor and external capacitor Cs's time constant; when the S/S pin voltage becomes less than 1.5V, turns off the Vref block and cutting off all the circuit in FAN7554, with the exceptions of the ULVO circuit and On/Off control circuit. It drives the output drive in low through the Good Logic block and discharges the Cs potential to the GND. Such double OFF control prevents abnormal operation from a transient state or noise environment and provides for a more stable operation. Because a 5uA current source is connected to Cfb even in off state, Cfb is charged if an ON signal is received. When the feedback voltage exceeds 0.3V, it operates normally by turning on the Vref block. The operating current is about 200uA (Typ.) in off state, so the circuit consumes low power. 12

FAN7554

Vref(5V)

3.5V S Q R 8 Vref UVLO Off PWR_ Save 1K On 1.5V Internal Bias Good Logic 5V Vref

15V/9V

7 Vcc

100uA S/S 2 Cs 0.3V Vo FB 1 Cfb 5uA

Vcc

External Signal

[ON/OFF Control Circuit]

Figure 9. ON/OFF Control Circuit

Vref

Icc

5V 4.5mA

0.2mA t Vs/s 5V Slope(dv/dt) = 1 * Cs 3V Slope(dv/dt) = 100uA / Cs 1.5V Slope(dv/dt) = (1mA+100uA)/Cs t Vfb OFF SIGNAL Slope(dv/dt) = (1mA+5uA) / 0.3V ~ 3V ON SIGNAL 0.3V Slope(dv/dt)= 5uA / Cfb t NORMAL STAGE OFF STATE NORMAL STAGE Cfb

Figure 10. ON-OFF Control Circuit Waveform

13

FAN7554

Protection Circuits FAN7554 has many built-in protection circuits that do not need additional components, providing reliability without cost increase. These protection circuits have the Auto-restart configuration. In this configuration, the protection circuit resets when Vcc is below UVLO stop threshold (9V) and restarts when Vcc is above UVLO start threshold voltage (15V) -. Over Voltage Protection Even if the feedback circuit appear to be open due to an error in the secondary side feedback or no soldering , the switching on the primary side still continues until the protection circuit starts; this causes the secondary side voltage to become much greater than the rated voltage. The over voltage protection circuit of FAN7554 senses Vcc inside the IC. If Vcc becomes greater than 34V, the protection circuit starts to operate. Because Vcc is in proportion to the output line voltage of the flyback converter, Vcc during normal operation should be appropriately maintained at less than 34V. -. Over Load Protection An overload is different from a short load. An overload occurs when a load becomes greater than the preset load during normal operation. for example, the IC stops itself if the SMPS outputs 110W when it exceeds the preset maximum power of 100W. If this protection circuit initiates, then this could perform an undesired execution even during a transient state. Therefore, as a measurement against such a happening, the protection circuit in FAN7554 is forced to wait a specified time before operating to determine whether the recognized overload is a transient or a overload state.

5uA Vo Vfb Cfb #1 D1

1mA OSC. D2 Vfb * R 2R

Vck

FAN7554

S R

KA431

6V

Reset

R S

Shutdown

6V

3V 0 t1 Time Constant = 3R*Cfb 5uA = Cfb*3V/t2 t2 Shutdown t

Figure 11. Delayed Shutdown [ Delayed Shutdown ]

14

FAN7554

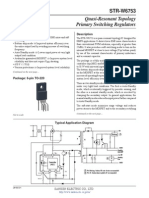

Application Circuit

R EC T C6 R3 R4 D5 R T1 FUS E L1 C2 R5 C1 C4 D2 C12 C 11 L2

+ 1 2V

C3 R6 C5 D4

+5V 10A + 12V 2A5 V

L4

R1

R9 R2 D1 R7 D6 D3 C 13

C 14 R10

C7

8 V r ef

7 V cc

6 OU T

5 GN D

R15

F AN 7554

R 16

F /B S /S 2 Is 3 R t/C t 4

R1 9

1

R11

C8

R 14

C 21

R 17

O P1 R18

R12

C9

C 22

C 10

C20 C 17

O P1 IC3 C 15 C 16

Figure 12. 100W Forward converter circuit with FAN7554

15

FAN7554

Part List

Part RT1 R1 R2 R3 R4 R5 R6 R7 R9 R10 R11 R12 R13 R14 R15 R16 R17 R18 Value NTC:10D-11 33k (1/2W) 33k (1/2W) 56k (2W) 56k (2W) 220k (1W) 220k (1W) 6.8 50k (1%) 50k (1%) 1k 820 47k 20 7k 1k 0.6 (1W) Part R19 C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 C14 C15 C16 C17 Value 2.2k 0.47uF(275V)(1) 472 (1kV)(2) 472 (1kV)(2) 470uF(200V)(3) 470uF(200V)(3) 223 (630V)(3) 33uF(35V)(4) 104(2) 1uF(10V)(3) 101(2) 1000uF (16V)(3) 1000uF (16V)(3) 3300uF (10V)(3) 3300uF (10V)(3) 105(2) Part C20 C21 C22 D1 D2 D3 D4 D5 D6 L1 L2 L3 L4 OP1 FUSE RECT Q1 Value 332(2) 272(2) 333(2) 1N4004 FR157 UF4007 S30SC4M (25A) SBL1040CT (10A) 1N4148 Line Filter 9.2 1ron Power 27 10uH PC817 5A/250VAC PBS406GU SSH8N80 -

*Note *(1) Box Capacitor (2) Ceramic Capacitor (3) Electorlytic Capacitor (4) Film Capacitor

16

FAN7554

Mechanical Dimensions

Package Dimensions in millimeters

8-SOP

17

FAN7554

Mechanical Dimensions (Continued)

Package Dimensions in millimeters

8-DIP

18

FAN7554

Ordering Information

Product Number FAN7554 FAN7554D Package 8-DIP 8-SOP Operationg Temperature -25C ~ 85C

19

FAN7554

DISCLAIMER FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR INTERNATIONAL. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

www.fairchildsemi.com 9/25/00 0.0m 001 Stock#DSxxxxxxxx 2000 Fairchild Semiconductor International

2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

This datasheet has been download from: www.datasheetcatalog.com Datasheets for electronics components.

Вам также может понравиться

- AN7554Документ22 страницыAN7554Corban MihaiОценок пока нет

- FAN7602 - Green Current Mode PWM Controller - Fairchild SemiconductorДокумент17 страницFAN7602 - Green Current Mode PWM Controller - Fairchild SemiconductorVijay MistryОценок пока нет

- DM 0565 RДокумент20 страницDM 0565 R81968Оценок пока нет

- 60 W-Universal Input/90 W-230 Vac Input PWM Switching RegulatorsДокумент14 страниц60 W-Universal Input/90 W-230 Vac Input PWM Switching RegulatorsIBSDIALLO0% (1)

- 1M0365RДокумент11 страниц1M0365RAndro DackОценок пока нет

- CM6800GIPДокумент18 страницCM6800GIPAndré Frota PaivaОценок пока нет

- L 6565Документ17 страницL 6565tatatabuchoОценок пока нет

- Green Current Mode PWM Controller: Features DescriptionДокумент12 страницGreen Current Mode PWM Controller: Features Descriptionceny123Оценок пока нет

- STR W6735Документ14 страницSTR W6735proctepОценок пока нет

- Fan 7530Документ20 страницFan 7530aldo_suviОценок пока нет

- FSDH0165Документ9 страницFSDH0165Giovanni Carrillo VillegasОценок пока нет

- LM 2587 DatasheetДокумент26 страницLM 2587 DatasheetAnonymous vKD3FG6RkОценок пока нет

- SSC2001S Application NoteДокумент18 страницSSC2001S Application NoteGerardo Mendez CamarilloОценок пока нет

- Fs6s1265re PDFДокумент11 страницFs6s1265re PDFHelton AmorimОценок пока нет

- Inverter For Air Conditioner IGBT/Power MOS FET Gate Drive Industrial InverterДокумент9 страницInverter For Air Conditioner IGBT/Power MOS FET Gate Drive Industrial InverterFurqan MemonОценок пока нет

- KA1H0165RДокумент12 страницKA1H0165RJtzabalaОценок пока нет

- Fan 7313Документ11 страницFan 7313KathafiОценок пока нет

- Viper 53Документ24 страницыViper 53Cadena CesarОценок пока нет

- 5 M 0965 QT UДокумент12 страниц5 M 0965 QT UcesarlcaОценок пока нет

- STR W6735 DatasheetДокумент13 страницSTR W6735 DatasheetloagerОценок пока нет

- STR W6753 DatasheetДокумент8 страницSTR W6753 DatasheetjgerabmОценок пока нет

- L4949Документ11 страницL4949Николай КръстевОценок пока нет

- SG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorДокумент10 страницSG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorJayesh SuryavanshiОценок пока нет

- LM350 DatasheetДокумент12 страницLM350 DatasheetOmarVelasquezC.Оценок пока нет

- 161 20551 0 FS7M0880Документ16 страниц161 20551 0 FS7M0880Edwin Vitovis TorresОценок пока нет

- 7 M 0880Документ18 страниц7 M 0880Mahmoued YasinОценок пока нет

- Regulating Pulse Width Modulators with Improved PerformanceДокумент7 страницRegulating Pulse Width Modulators with Improved PerformancekkaytugОценок пока нет

- Data SheetДокумент7 страницData Sheetitamar_123Оценок пока нет

- IC KA3S0680RF DatasheetДокумент12 страницIC KA3S0680RF Datasheetnaupas007Оценок пока нет

- 5H0165RДокумент12 страниц5H0165RDomingo ArroyoОценок пока нет

- Ka 5q0765rt (Sps Fairchild)Документ10 страницKa 5q0765rt (Sps Fairchild)Cristian Steven RuizОценок пока нет

- FSDM07652R DatasheetДокумент16 страницFSDM07652R Datasheetmarianos67Оценок пока нет

- Apl 5930Документ17 страницApl 5930zanaturОценок пока нет

- LM3478 High Efficiency Low-Side N-Channel Controller For Switching RegulatorДокумент22 страницыLM3478 High Efficiency Low-Side N-Channel Controller For Switching RegulatorVinoth Kumar RajendranОценок пока нет

- DL 0165 RДокумент20 страницDL 0165 Rledu035Оценок пока нет

- AZ7500BC D1.3 070427nДокумент13 страницAZ7500BC D1.3 070427nroozbehxoxОценок пока нет

- TLP250 TOSHIBA Photocoupler for IGBT and MOSFET Gate DriveДокумент7 страницTLP250 TOSHIBA Photocoupler for IGBT and MOSFET Gate DriveHeriberto Flores AmpieОценок пока нет

- Ka1 (H0) 265RДокумент10 страницKa1 (H0) 265RminiecateОценок пока нет

- LD7523 DS 00Документ18 страницLD7523 DS 00Eduardo LaloОценок пока нет

- TLP2601 Photocoupler Datasheet SummaryДокумент9 страницTLP2601 Photocoupler Datasheet SummarySherif OkdaОценок пока нет

- Off-Line Quasi-Resonant Switching Regulators Features and Benefits (39Документ9 страницOff-Line Quasi-Resonant Switching Regulators Features and Benefits (39ch3o10836266Оценок пока нет

- TLP358 Datasheet en 20120306Документ16 страницTLP358 Datasheet en 20120306Kumaran ChakravarthyОценок пока нет

- Datasheet STR 6757Документ11 страницDatasheet STR 6757Walter CarreroОценок пока нет

- TLP350 Gate DriverДокумент9 страницTLP350 Gate Driversandeepbabu28Оценок пока нет

- MP1542 r1.5Документ11 страницMP1542 r1.5Joshua KochОценок пока нет

- Lm2577 Adj MDCДокумент27 страницLm2577 Adj MDCroozbehxoxОценок пока нет

- CS2841BD14Документ10 страницCS2841BD14giapy0000Оценок пока нет

- UC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerДокумент16 страницUC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerCortés BernaОценок пока нет

- UC3845ANДокумент15 страницUC3845ANMiloud ChouguiОценок пока нет

- L6565Документ18 страницL6565Sergio Daniel BarretoОценок пока нет

- Transition-Mode PFC Controller: 1 FeaturesДокумент17 страницTransition-Mode PFC Controller: 1 Featuresadriancho66Оценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsОт EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsОценок пока нет

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsОт EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsРейтинг: 3.5 из 5 звезд3.5/5 (6)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Рейтинг: 2.5 из 5 звезд2.5/5 (3)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1От EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Рейтинг: 4.5 из 5 звезд4.5/5 (3)

- Analog Circuit Design Volume Three: Design Note CollectionОт EverandAnalog Circuit Design Volume Three: Design Note CollectionРейтинг: 3 из 5 звезд3/5 (2)

- Exceptions Interrupts TimersДокумент35 страницExceptions Interrupts Timersmeena1827100% (1)

- CDM750/1250/1550 Series Parts List and AccessoriesДокумент10 страницCDM750/1250/1550 Series Parts List and AccessoriesOusmost MostaОценок пока нет

- WinSpice3 User Manual GuideДокумент142 страницыWinSpice3 User Manual GuideRandom PicsОценок пока нет

- EST3Документ4 страницыEST3Juan Dela CruzОценок пока нет

- Service Manual: 6 Disc CD ChangerДокумент15 страницService Manual: 6 Disc CD ChangerAndre VPОценок пока нет

- Project Report On Integrated CircuitДокумент20 страницProject Report On Integrated CircuitSushil Kumar67% (6)

- Digital Signal Processing Soma Biswas 2017Документ19 страницDigital Signal Processing Soma Biswas 2017Bkm Mizanur RahmanОценок пока нет

- A45. Bosch DCN - NGДокумент274 страницыA45. Bosch DCN - NGpablo_666_zarautzОценок пока нет

- Mylk - Mylk (386) LayoutДокумент6 страницMylk - Mylk (386) Layoutmini998Оценок пока нет

- Coaxial Cable (Noise Immunity) HuhuДокумент10 страницCoaxial Cable (Noise Immunity) HuhuMohd Izzat Abd GhaniОценок пока нет

- Sanyo - Denki BS1D200P10 Datasheet PDFДокумент64 страницыSanyo - Denki BS1D200P10 Datasheet PDFCarlos CaballeroОценок пока нет

- Thesis-2008-Printed Monopole Antenna For UltraДокумент271 страницаThesis-2008-Printed Monopole Antenna For UltraDr-Pritam Singh BakariyaОценок пока нет

- Wave GuidesДокумент3 страницыWave Guidessubin4bslОценок пока нет

- Parts PDFДокумент5 страницParts PDFJoão SilvaОценок пока нет

- Digitally-Controlled Analog Volume Control PDFДокумент21 страницаDigitally-Controlled Analog Volume Control PDFBhadreshkumar SharmaОценок пока нет

- RGP10A, RGP10B, RGP10D, RGP10G, RGP10J, RGP10K, RGP10M: Vishay General SemiconductorДокумент4 страницыRGP10A, RGP10B, RGP10D, RGP10G, RGP10J, RGP10K, RGP10M: Vishay General SemiconductorDelos Santos JojoОценок пока нет

- Chapter 1 - 2 - 3 FINALДокумент15 страницChapter 1 - 2 - 3 FINALNin Ninjoe JoeОценок пока нет

- 06.0 PLC Processor 174 PDFДокумент1 страница06.0 PLC Processor 174 PDFSatyasrinivas PulavarthiОценок пока нет

- UNIT - 1 - AC Characteristics and Frequency ResponceДокумент18 страницUNIT - 1 - AC Characteristics and Frequency ResponceGauthiОценок пока нет

- Mechatronics Lab Manual - (01!10!2020)Документ24 страницыMechatronics Lab Manual - (01!10!2020)Shreyas HuilgolОценок пока нет

- Industrial Training Presentation on 132KV Interlinking and 220/132KV SubstationДокумент24 страницыIndustrial Training Presentation on 132KV Interlinking and 220/132KV SubstationVinay ChandelОценок пока нет

- Avr MicrocontrollerДокумент21 страницаAvr MicrocontrollerRohit KanyalОценок пока нет

- EET107 Digital Electronics Tutorial 3 Flip-Flop CircuitsДокумент7 страницEET107 Digital Electronics Tutorial 3 Flip-Flop CircuitszulОценок пока нет

- Routine Production Testing of Voltage RegulatorsДокумент2 страницыRoutine Production Testing of Voltage RegulatorssoltaniОценок пока нет

- SAMSUNG LCD Service Manual Internal) - ES15UДокумент81 страницаSAMSUNG LCD Service Manual Internal) - ES15Uqwerzwill905560Оценок пока нет

- Lab2 DCДокумент52 страницыLab2 DCRavi Krishna MalkaОценок пока нет

- Sector SWAP Identification GuideДокумент10 страницSector SWAP Identification Guideakpan.u100% (2)

- CompilationДокумент23 страницыCompilationChester MinguilloОценок пока нет

- Owner'S Manual: Xa SeriesДокумент12 страницOwner'S Manual: Xa SeriesAmin AminuddinОценок пока нет

- SUA3000IДокумент5 страницSUA3000Iprabhakar.rvmhОценок пока нет