Академический Документы

Профессиональный Документы

Культура Документы

EE 241 Digital Logic Design - Course Outline

Загружено:

Nasir Ud Din GoharИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

EE 241 Digital Logic Design - Course Outline

Загружено:

Nasir Ud Din GoharАвторское право:

Доступные форматы

NUST School of Electrical Engineering and Computer Science

A center of excellence for quality education and research

EE 241

Prerequisite: None

Digital Logic Design

Fall 2011

Email:nasir.gohar@seecs.edu.pk Tel: 051-9085-2250 Office Hours Fri: 15:00-16:50 Lab Instructor: Mr. Yasir Ateeq

Instructor: Dr. Nasir ud Din Gohar Office: Faculty Bloc k Room # A119 Time and Place: Tue: CR-10 09:00-09:50 & 15:00-15:30 Thu: CR-11 15:00-15:50 Lab: Wed: 09:00-11:50

Course Objective:

This course aims to provide the electronic engineering students their first exposure to design digital circuits using conventional as well as modern design techniques. Having gone thru the basic logic gates, they will learn how to implement any digital electronic circuit using these basic gates. Building on their skills in these basic gates, they will learn how to design combinational as well as sequential logic circuits. They will also be exposed to logic circuit two-level optimization/simplification using K-Maps/QM reduction techniques. [Moreover, side-by-side, they will learn how to design and simulate these logic circuits using CAD tools such as ModelSim while programming in Verilog HDL. Finally, if time permits, use of ROM as well as other PLDs to design simple logic circuits will be discussed leading to their first exposure to FPGA technology.]

Text Book:

1.

Digital Design, 4th Edition, by Morris Mano & Michael D. Ciletti, by Pearson Education, Inc. Prentice Hall, 2007. [ISBN 0 13 -198924-3]

Reference Books: (Although not limited to but to name a few)

1. 2. 3. Logic and Computer Design Fundamentals, 2nd Edition, by M. Mano and C. Kime, published by Prentice Hall, 2000. [ISBN 0-13-012468-0] Digital Systems: Principles and Applications, 7th Ed. by Tocci and Widmer, published by Prentice Hall, 1998. [ISBN 0-13-649492-7] Digital Fundamentals, 7th Ed. By T. L. Floyd, , published by Prentice Hall, Inc. 2000. [ISBN 0-13-085268-6]

Main Topics to be Covered:

1. 2. 3. Introduction Number Systems and Their Conversion Combinational Logic Circuits o Boolean Algebra o Logic Gates o K Map/QM Techniques 4. 5. 6. 7. Combinational Logic Design Sequential Logic Design Verilog HDL Representation and Design of Simple Digital Systems (Optional) Memory and Programmable Logic Devices (PLD) and their Applications (Optional)

Policy Matters:

1. 2. 3. 4. 5. 6. Assignments [02%]: Number of assignments will be issued and each will be due exactly one week after its issue date unless otherwise specified. No late submissions will be allowed. Quizzes [08%]: At least 6 Quizzes will be conducted in class in the first 15-20 minutes, and late comers will suffer. No make-up provisions. Labs/Mini-Project [20+5=25%]. Lab would be conducted on weekly basis. During the last leg of the course, Class Projects will be issued. Project Report will be due within 4 weeks from the issue date. No late submission allowed. Two One Hour Tests [12.5+12.5 =25%] during 6th week and 12th week. Dont ask for any postponement, which is impossible. Final Test [40%] in 18th week. It is mandatory to maintain at least 75% class attendance to be allowed to sit in Final Test. Please try to observe Instructor/TA Office Hours for any help.

7.

N. D. Gohar

Page-1/1

Spring-2011

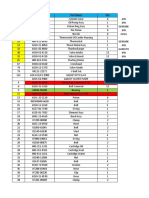

Digital Logic and Design-Lecture Breakdown

Week No 1. Lecture No 1. Topics Introduction: Digital Systems and motivation for study Number Systems: Binary, Octal, Decimal and Hexadecimal Numbers and Base Conversions. Complements: Subtraction of Unsigned Numbers using Complements. Signed Binary Numbers, Arithmetic Addition and Subtraction of Signed Binary Numbers. Binary Codes Binary storage and Registers: Binary Logic; Definition of Binary Logic and Logic Gates. Introduction: Boolean Algebra: Basic and Axiomatic Definition of Boolean Algebra; TwoValued Boolean Algebra. Basic Theorems and Properties of Boolean Algebra Boolean Functions. Canonical and Standard Forms. Other Logic Operations. Digital Logic Gates and Integrated Circuits. Introduction: The K-Map Method; Two, and Three Variable K-Maps. Sum-of-Products and Product-of-Sums simplification using FourVariable K-Maps; Essential and Non-essential Prime Implicants. Five-Variable K-Maps; Sumof-Products and Product-ofSums simplification using Five-Variable K-Maps. Text Book Reference 1-1 Other References Remarks

2.

1-2,1-3,&1-4

3.

1-5

2.

4*.

1-6

5*. 6.

1-7 1-8&1-9

7.

2-1&2-2

8.

2-3

3.

9. 10. 11.

2-4 2-5 2-6 2-7&2-8 3-1

4.

12. 13.

14.

3-2&3-4

5.

15.

3-3

N. D. Gohar

Page-2/1

Spring-2011

16. 17. 6. 7. 18. 19. 20.

Dont Care conditions. NAND and NOR implementations. Other Two-Level implementations. Exclusive-OR function: Parity Generation and Checking. Verilog Hardware Description Language (Verilog HDL): Design Entry using Source Code (Optional) Introduction: Combinational Circuits and their Analysis Procedure. Design Procedure with Code Conversion Example. Half and Full Adders: 4-BIT Adder Design using Full Adders. Design of 4-Bit Adder using Carry Look-ahead Generator. Binary Sub-tractor and Overflow Decimal Adder. Binary Multiplier. Magnitude Comparator. Decoders. Encoders. Multiplexers and Tri-State Gates. HDL for Combinational Circuits (Optional) HDL for Combinational Circuits (Optional) Introduction: Sequential Circuits and different types of Latches. Flip-Flops: Edge-Triggered D Flip-Flop. Other Flip-Flops. Analysis of ClockedSequential Circuits. Analysis with D Flip-Flops, JK Flip-Flops, and T FlipFlops.

3-5 3-6 3-7 3-8 3-9 1 OHT

st

8.

21.

4-1&4-2

22. 23.

4-3 4-4

9.

24. 25. 26.

4-4 4-4 4-5 4-6 4-7 4-8 4-9 4-10 4-11 4-11 5-1&5-2

10.

27. 28. 29.

11.

30. 31. 32.

12.

33. 34.

35. 13. 14. 36. 37.

5-3 5-3 5-4 2 OHT

nd

38.

5-4

N. D. Gohar

Page-3/1

Spring-2011

15.

39. 40.

Mealy and Moore Models. State Reduction and Assignment. Design ProcedureSynthesis using D Flip-Flops, JK Flip-Flops, and T FlipFlops. HDL for Sequential Circuits (Optional) HDL for Sequential Circuits (Optional) Introduction: Registers with Parallel Load. Shift Registers; 4-Bit Shift Register; Serial Transfer and Serial Addition. 4-Bit Universal Shift Registers. Ripple Counters; Binary and BCD Ripple Counters. Synchronous Counters: Binary and BCD Counters. Other Counters; Counter with unused States. Other Counters: Counters with unused states, Ring Counters and Johnson Counters. HDL for Sequential Circuits (Optional) HDL for Sequential Circuits (Optional) Revision -

5-4 5-6

41.

5-7

16.

42. 43. 44.

5-5 5-5 6-1 6-2

17.

45.

46. 47. 18. 48. 49. 50.

6-2 6-3 6-4 6-5 6-5

19.

51. 52. 53.

6-6 6-6

20.

Final Exam

N. D. Gohar

Page-4/1

Spring-2011

Вам также может понравиться

- Ece103 Digital-logic-Design Eth 1.10 Ac29Документ2 страницыEce103 Digital-logic-Design Eth 1.10 Ac29netgalaxy2010Оценок пока нет

- Module Descriptor For Digital ElectronicsДокумент4 страницыModule Descriptor For Digital ElectronicsTashi DendupОценок пока нет

- EE204 Digital Electrncs N Logic DesignДокумент3 страницыEE204 Digital Electrncs N Logic DesignsaniljayamohanОценок пока нет

- GTU Digital Electronics Syllabus Explains Concepts & DesignДокумент3 страницыGTU Digital Electronics Syllabus Explains Concepts & Designsjbv.hardik582Оценок пока нет

- Digital Electronics Circuits Course FileДокумент23 страницыDigital Electronics Circuits Course FileraghuippiliОценок пока нет

- Course File Final Heena A DigitalДокумент23 страницыCourse File Final Heena A DigitalraghuippiliОценок пока нет

- 2131004Документ3 страницы2131004Parthiv Oza MasterMindОценок пока нет

- NUST Syllabus For DLDДокумент2 страницыNUST Syllabus For DLDwistfulmemory100% (1)

- Comparison Between E54 and EC41: Tashi Asst. Lecturer Ece, CST Rinchending, Phuentsholing Aug. 2012Документ15 страницComparison Between E54 and EC41: Tashi Asst. Lecturer Ece, CST Rinchending, Phuentsholing Aug. 2012tashidendupОценок пока нет

- Digital System Design: L T P C 3 0 0 3Документ4 страницыDigital System Design: L T P C 3 0 0 3Nishant KumarОценок пока нет

- Digital Logic DesignДокумент4 страницыDigital Logic DesignkiranОценок пока нет

- ECE Digital Principles Lesson PlanДокумент4 страницыECE Digital Principles Lesson PlanDharani KumarОценок пока нет

- DSD Syll - Merged DSD GtuДокумент8 страницDSD Syll - Merged DSD GtuSandeep kumarОценок пока нет

- Gujarat Technological University: W.E.F. AY 2018-19Документ3 страницыGujarat Technological University: W.E.F. AY 2018-19Alok MauryaОценок пока нет

- Subject Made Easy - Digital ElectronicsДокумент21 страницаSubject Made Easy - Digital Electronicsradha_chaudhary20034343100% (1)

- DDE 1313 Digital Electronics 1 LOДокумент6 страницDDE 1313 Digital Electronics 1 LOAhmad FadzlyОценок пока нет

- Electronics 4Документ4 страницыElectronics 4drkhamuruddeenОценок пока нет

- EEE241-DLD Course OutlineДокумент2 страницыEEE241-DLD Course OutlineZeeshan TahirОценок пока нет

- BEEE206L - DIGITAL-ELECTRONICS - TH - 1.0 - 67 - Digital ElectronicsДокумент3 страницыBEEE206L - DIGITAL-ELECTRONICS - TH - 1.0 - 67 - Digital ElectronicsNithish kumar RajendranОценок пока нет

- Digital Principles and System Design Course Plan (CS 6201Документ5 страницDigital Principles and System Design Course Plan (CS 62011627sakthiОценок пока нет

- B.tech Cse VTR Uge2021 de SyllabusДокумент4 страницыB.tech Cse VTR Uge2021 de SyllabusBOLLIGARLA MOHAN SAI AKASH,CSE2021 Vel Tech, ChennaiОценок пока нет

- 9 - 28 - 0 - 0 - 40 - 5th Electrical DE&MPДокумент165 страниц9 - 28 - 0 - 0 - 40 - 5th Electrical DE&MPvijay kumar GuptaОценок пока нет

- Digital Electronics Laboratory Manual (ECE 2002L) : For 4 Semester B.TechДокумент62 страницыDigital Electronics Laboratory Manual (ECE 2002L) : For 4 Semester B.TechTushar PatelОценок пока нет

- Digital Electronic Design: 1 Lecturers and Departmental AdministratorДокумент16 страницDigital Electronic Design: 1 Lecturers and Departmental AdministratorTam TrieuvanОценок пока нет

- ECE COURSE DESCRIPTIONДокумент8 страницECE COURSE DESCRIPTIONNaresh BopparathiОценок пока нет

- Digital Systems Lab - Catalog DescriptionДокумент3 страницыDigital Systems Lab - Catalog Descriptionmani_vlsiОценок пока нет

- EECE 320 Ch1: Intro to Digital Systems DesignДокумент11 страницEECE 320 Ch1: Intro to Digital Systems DesignHussein HakimОценок пока нет

- FALLSEM2022-23 BECE102L TH VL2022230104438 Reference Material I 21-07-2022 BECE102LДокумент3 страницыFALLSEM2022-23 BECE102L TH VL2022230104438 Reference Material I 21-07-2022 BECE102LUrjoshi AichОценок пока нет

- Updated Course Outline EE 221 - Digital - Logic - Design - Spring - 2023Документ9 страницUpdated Course Outline EE 221 - Digital - Logic - Design - Spring - 2023Laiqa AliОценок пока нет

- EE 421-Digital System Design-Dr. Shahid Masud-Updated PDFДокумент4 страницыEE 421-Digital System Design-Dr. Shahid Masud-Updated PDFUbaid UmarОценок пока нет

- Chapter 1 - IntroductionДокумент18 страницChapter 1 - IntroductionKarimovaRaikhanovnaОценок пока нет

- Bece102l - Digital-Systems-Design - TH - 1.0 - 71 - Bece102l - 66 AcpДокумент2 страницыBece102l - Digital-Systems-Design - TH - 1.0 - 71 - Bece102l - 66 AcpsggrfgfОценок пока нет

- Switching Thoery and Logic DesignДокумент159 страницSwitching Thoery and Logic DesignamarОценок пока нет

- EE 421-Digital System Design-Dr. Shahid MasoodДокумент4 страницыEE 421-Digital System Design-Dr. Shahid MasoodSher Hassan RazaОценок пока нет

- An Ability To Understand The Basic Number Systems Used in Digital DesignДокумент2 страницыAn Ability To Understand The Basic Number Systems Used in Digital DesignAnitha RaviОценок пока нет

- CompДокумент40 страницCompharshal2000Оценок пока нет

- Digital Electronics ProjectsДокумент244 страницыDigital Electronics ProjectsBenjamin DoverОценок пока нет

- Syllabus 2140910Документ4 страницыSyllabus 2140910Hardik AgravattОценок пока нет

- Revision of FundamentalsДокумент23 страницыRevision of FundamentalsAnup S. Vibhute DITОценок пока нет

- Bti 402 Digital ElectronicsДокумент1 страницаBti 402 Digital ElectronicsSanjay Kr SinghОценок пока нет

- L1 EEE 2022 - ElectronicsДокумент6 страницL1 EEE 2022 - ElectronicsSuresh ThanakodiОценок пока нет

- Course: Core Paper VII - : HPHCR3072T & HPHCR3072PДокумент3 страницыCourse: Core Paper VII - : HPHCR3072T & HPHCR3072PAdhara MukherjeeОценок пока нет

- Ece-Iv Semester SyllabusДокумент13 страницEce-Iv Semester Syllabuskrishna_sharma17Оценок пока нет

- Purdue University Calumet ECET Digital Logic CourseДокумент4 страницыPurdue University Calumet ECET Digital Logic CourseMoez Ul Hassan0% (1)

- Digital Electronics-SyllabusДокумент2 страницыDigital Electronics-Syllabussaravya RajОценок пока нет

- Gujarat Technological University: W.E.F. AY 2018-19Документ4 страницыGujarat Technological University: W.E.F. AY 2018-19useless9925Оценок пока нет

- De Course File 2013-14Документ75 страницDe Course File 2013-14ragvshahОценок пока нет

- Assignment Module - 1HDLДокумент2 страницыAssignment Module - 1HDLvijayarani.katkamОценок пока нет

- Cse - Final PDFДокумент81 страницаCse - Final PDFAnugraha DevanОценок пока нет

- DSD Using VerilogДокумент1 страницаDSD Using VerilogMansi JhambОценок пока нет

- Amity, Digital Electronics-1 (B.tech Ece-4th Sem0Документ1 страницаAmity, Digital Electronics-1 (B.tech Ece-4th Sem0deepak173Оценок пока нет

- Logic Synthesis and Verification: Course InfoДокумент7 страницLogic Synthesis and Verification: Course InfoManisha JadavОценок пока нет

- STLD NotesДокумент159 страницSTLD NotesanithaОценок пока нет

- Digital Circuits Course OverviewДокумент3 страницыDigital Circuits Course OverviewPRANAV VIKRAMAN S S ECE DEPTОценок пока нет

- A204SE T212 StudyGuide - FinalДокумент9 страницA204SE T212 StudyGuide - FinalLe Nguyen Tran QuangОценок пока нет

- Practical Design of Digital Circuits: Basic Logic to MicroprocessorsОт EverandPractical Design of Digital Circuits: Basic Logic to MicroprocessorsРейтинг: 4.5 из 5 звезд4.5/5 (2)

- Top-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsОт EverandTop-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsОценок пока нет

- Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLОт EverandIntroduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLОценок пока нет

- Computational Number Theory and Modern CryptographyОт EverandComputational Number Theory and Modern CryptographyРейтинг: 3.5 из 5 звезд3.5/5 (2)

- Release Notes Sap 2000 V 2331Документ8 страницRelease Notes Sap 2000 V 2331sami touatiОценок пока нет

- GT Solar Inverters for Multi-Megawatt Solar Power PlantsДокумент8 страницGT Solar Inverters for Multi-Megawatt Solar Power PlantsRajesh Kumar MamidiОценок пока нет

- Ansible PresentationДокумент23 страницыAnsible Presentationstanislaw.jachuraОценок пока нет

- Design and Costing of 3kW Home Solar PlantДокумент2 страницыDesign and Costing of 3kW Home Solar Plant002Pradeep002Оценок пока нет

- Adele Kuzmiakova - The Creation and Management of Database Systems-Arcler Press (2023)Документ262 страницыAdele Kuzmiakova - The Creation and Management of Database Systems-Arcler Press (2023)alote1146Оценок пока нет

- Reference Guide FTTH PONДокумент116 страницReference Guide FTTH PONameeq77100% (2)

- GS-KB55S Operating InstuctionsДокумент8 страницGS-KB55S Operating InstuctionsPiero CaprettiОценок пока нет

- PC Software EddyAssist EДокумент14 страницPC Software EddyAssist EizmitlimonОценок пока нет

- RMA Case StudyДокумент8 страницRMA Case StudyJohnny NguyenОценок пока нет

- How To Extract .SAR File For Windows - My Code CommunityДокумент3 страницыHow To Extract .SAR File For Windows - My Code CommunityRangabashyamОценок пока нет

- Installing Process Instrumentation and Controlling Cabling and TubingДокумент48 страницInstalling Process Instrumentation and Controlling Cabling and TubingAbela DrrsОценок пока нет

- Innovating To Create IT-Based New Business Opportunities at UPSДокумент17 страницInnovating To Create IT-Based New Business Opportunities at UPSjieminaОценок пока нет

- GS43D07N10-08EN - 005 Oprex Managed Service - Cloud EditionДокумент22 страницыGS43D07N10-08EN - 005 Oprex Managed Service - Cloud Editionhamzah yudha perwiraОценок пока нет

- ANSI SLAS 4-2004 Standard for Microplate Well PositionsДокумент13 страницANSI SLAS 4-2004 Standard for Microplate Well PositionsnikkiharОценок пока нет

- Engine Parts Listing with 40 PartsДокумент9 страницEngine Parts Listing with 40 PartsGeno CideОценок пока нет

- Test Logic Insertion For Optimization of Testing Parameters On Lower Technology NodeДокумент6 страницTest Logic Insertion For Optimization of Testing Parameters On Lower Technology NodeshaguftaОценок пока нет

- Boltec LC - 9851 2201 01eДокумент4 страницыBoltec LC - 9851 2201 01ePablo Luis Pérez PostigoОценок пока нет

- HUAWEI WATCH GT3 42mm User Guide - (MIL-B19,01, EN-GB)Документ39 страницHUAWEI WATCH GT3 42mm User Guide - (MIL-B19,01, EN-GB)wijayanataОценок пока нет

- Spark 35DSGДокумент1 страницаSpark 35DSGMoez JbeliОценок пока нет

- Marine Elevators (200902)Документ6 страницMarine Elevators (200902)Arky HarkyanОценок пока нет

- 3G Counter LevelДокумент27 страниц3G Counter LevelDjungdjunan ArdyОценок пока нет

- Total Car Check Report For WP05BDOДокумент8 страницTotal Car Check Report For WP05BDONimsoc UgogОценок пока нет

- Operation Management Assignment 1 Provides Overview of Mass Customization and Inventory AccuracyДокумент7 страницOperation Management Assignment 1 Provides Overview of Mass Customization and Inventory AccuracyHarprit SinghОценок пока нет

- Performance Management SetupsДокумент34 страницыPerformance Management Setupshamdy2001100% (6)

- PLC and SCADA Lab Experiments for Instrumentation CourseДокумент4 страницыPLC and SCADA Lab Experiments for Instrumentation CourseAnonymous FKMfvCbОценок пока нет

- EasyLift Brochure UKДокумент2 страницыEasyLift Brochure UKCreaciones VilberОценок пока нет

- 21st Century Path to Software Engineering Immersive BootcampДокумент11 страниц21st Century Path to Software Engineering Immersive BootcampDe VoОценок пока нет

- Integritest 5 Instrument: Specifications SheetДокумент8 страницIntegritest 5 Instrument: Specifications SheetMinh Sơn NguyễnОценок пока нет

- VSAM To OSAM PDFДокумент37 страницVSAM To OSAM PDFMurali Mohan NОценок пока нет

- SAP Design To Operate (D2O)Документ59 страницSAP Design To Operate (D2O)Akshay Rajan100% (1)