Академический Документы

Профессиональный Документы

Культура Документы

Adder

Загружено:

Shashank KhobragadeИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Adder

Загружено:

Shashank KhobragadeАвторское право:

Доступные форматы

TUTORIAL ON USING XILINX ISE DESIGN SUITE 10.

1: Design Entry Using VHDL (Full Adder) for Spartan-II E (Digilent D2E Board)

Shawki Areibi September 28, 2009

Introduction

The objective of this tutorial is to show the basic concepts of VHDL. VHDL (Very High-SpeedIntegrated-Circuit Description Language) is a very powerful digital design language. It allows a designer to specify a digital circuit at a very high level.

Start a new project

We wish to enter our design using a Hardware Description Language specically VHDL. 1. Load the Project Navigator from the All Programs Development Xilinx ISE Design Suite 10.1 ISE Project Navigator. 2. The Project Navigator window will appear. Select File New Project 3. The New Project Wizard window will appear.

Enter a name for the project. Specify the directory in which you want to store it in. For Top-Level Source Type select HDL. click 4. Another New Project Wizard dialog box will appear prompting you for device, synthesis and simulation settings for the project.

In this dialog box verify the following settings: Device Family Spartan2E. Device xc2s200e. Package pq208. Speed Grade -6. Synthesis Tool XST (VHDL/Verilog). Simulator ISE Simulator (VHDL/Verilog). Generated Simulation Language VHDL. If the information is correct click Next. 5. The next dialog box will ask if you wish to add a new source le to the project. Click New Source.... A new dialog box will appear prompting you for the le type, name and location. Select VHDL module from the list of le types and name the le MyAdder. The default location should be the project directory and ensure the Add to project box is checked. 6. In the Dene VHDL Source dialog box that appears, add ports A, B and CI as inputs and CO and S as outputs. Click Next when this is done. 7. The next dialog box will allow you to conrm the previous choices. Click correct. 2 if they are

8. You will now return to the New Project dialog box and the MyAdder.vhd source template that you have created will now be listed. Click Next. The next dialog box is used to add existing source les to the project. Since we are only using new source les in this project, click Next. Finally, a conrmation dialog box will appear. Click Finish if the information is correct.

Using the HDL Editor for VHDL

1. The VHDL editor window should show the following code:

library IEEE; use IEEE.STD LOGIC 1164.ALL; use IEEE.STD LOGIC ARITH.ALL; use IEEE.STD LOGIC UNSIGNED.ALL; Uncomment the following lines to use the declarations that are provided for instantiating Xilinx primitive components. library UNISIM; use UNISIM.VComponents.all; entity MyAdder is Port ( A : in std logic; B : in std logic; CI : in std logic; CO : out std logic; S : out std logic); end MyAdder; architecture Behavioral of MyAdder is begin

We are now ready to start working with the HDL Editor.

end Behavioral;

2. Between begin and end Behavioral add the following lines:

S <= ((A xor B) xor CI); CO <= ((A and B) or (CI and (A xor B)));

3. We must now check that the syntax of the VHDL code is correct. In the Project Navigator window highlight the VHDL source in the Sources in Project pane. Expand if it is not already and double click A process will be spawned to verify the VHDL code for syntax errors. If there are none, a green check mark will appear next to the Check Syntax process. If errors where found, A red cross will appear next to the Check Syntax process. The errors will be listed in the Errors tab of the transcript window located at the bottom of 3

the Project Navigator window. In it you will see a listing of the errors and the lines on which they occur. If you double click on an error message a red dot will appear in the VHDL editor pane next to (or close to) the line where the error was found. 4. Once you have eliminated all of the errors, save your work. 5. Next, we will assign the pins in our design to actual pins on the FPGA.

Creating a UCF le

A User Constraint File (UCF) is used to assign I/O pins in a design to the actual pins on the FPGA. Please refer to Appendix B for more information. 1. Highlight and right-click on the VHDL source in the Sources in Project pane of the Project Navigator and select New Source... from the oating menu. 2. From the list of le types select Implementation Constraints File. Name the le MyAdder and click Next. 3. The next dialog box is used to associate the UCF le with a specic source le. There is only one source le in the project, MyAdder.vhd, so click Next. 4. The nal dialog box is for conrming the information input in the previous dialog boxes. Click Finish if the information is correct. 5. In the Sources in Project pane ensure MyAdder.ucf is highlighted and in the Processes to expand the section and double click for Source pane click on the + in Edit Constraints (Text) in the list. 6. The UCF le has the following format: NET <pin name in VHDL design> LOC=P<pin number on FPGA> NOTE: Make sure to use upper case letters for the pin names. 7. Let us assign the inputs to the dips switches on the FPGA and the outputs to the LEDs. Please refer to the DIO1 board schematic for more information about pin connections. We will make CI switch 1, A switch 2, B switch 3, S LED 1 and CO LED 2. Design pin CI A B S CO FPGA pin 126 129 133 154 161 Description SW8 SW7 SW6 LED8 LED7

8. Enter the following code: NET CI LOC=P126; NET A LOC=P129; NET B LOC=P133; NET S LOC=P154; NET CO LOC=P161;

Compiling the design

1. Now go back to the Project Navigator window. Highlight the VHDL source in the Sources in in the Processes for Source pane to synthesize Project pane and double click the design 2. When the synthesis stage has completed, double click to implement the design. When the implementation process has completed a yellow exclaimation mark will appear. This can be safely ignored. 3. Finally, double click to generate the programming le that will be downloaded to the FPGA. It is possible to go straight to generating the programming le, and the Project Navigator will determine which of the previous step need to be run to produce an up to date programming le.

Downloading the design to the FPGA

Downloading a le to the FPGA is accomplished through the iMPACT tool. Please check Appendix A for setting up the DE2 and DIO1 boards before downloading the desing on the FPGA board. 1. Select 2. Double click in the Processes pane to start the iIMPACT tool.

3. In the Congure Devices dialog box that appears verify the Boundary-Scan Mode radio button is selected and click Next. 4. In the next dialog box ensure the Automatically connect to cable and identify BoundaryScan chain radio button is selected and click Finish. 5. A message window titled Boundary-Scan Chain Contents Summary will appear stating iMPACT will ask for the desired programming le. Click OK. 6. In the Assign New Conguration File dialog box select MyAdder.bit and click Open. 7. A message box will appear with a warning that the BIT le is for a dierent device than was found in the boundary scan. This can be safely ignored. Click Yes. 5

8. Another warning will appear stating that the Startup Clock has been changed to JtagClk in the bitstream. Click OK. 9. Move the cursor over the device that appears in the Boundary-Scan tab and press the left mouse button and select Program.... 10. In the Program Options dialog box that appears verify none of the options are selected and click OK.

Testing the design

Depending on the state of the inputs, you may or may not see some of the LEDs on the bargraph display glowing. We have assigned our Sum bit to LEDs LD1. The carry-out bit (C) is displayed on LED LD2. We are using the slide switches for our A and B inputs. The A inputs is assigned to SW switch 1. The B input is assigned to SW switch 2 Moving a switch to the ON position puts a 1 on the input. Moving a switch to the OFF position puts a 0 on the input. Try dierent combinations of inputs and verify that the circuit is working correctly.

Appendix A - Setting up the D2E and DIO1 Boards

This is intended to allow the student to quickly set up the D2E board with the DIO1 board for this tutorial. It does not attempt to explain the conguration and is in no way a substitute for the documentation provided with the two boards. It will allow you to use the slide switches as input and the LEDs as outputs. 1. Ensure that the slide switch located next to the DB25 connector is in the JTAG position. 2. Connect the parallel cable to the D2E board. 3. Ask your lab instructor to verify your jumper settings before applying power to the board. 4. Plug the 9V DC center positive adapter into the D2E board. A small red LED labeled LED2 should glow.

Appendix B - User Constrained File (UCF)

A User Constraint File (UCF) is used to assign I/O pins in a design to the actual pins on the FPGA. The UCF le has the following format: NET <pin name in VHDL design> LOC=P<pin number on FPGA>

9.1

LEDs

The Digilent DIO1 Board provides a series of eight LEDs (LD1LD8) and four multiplexed 7segment displays (DSP1) for use by a Digilent 2E FPGA Board. All of these LEDs are Large active high meaning that an LED segment will glow when a logic-high is applied to it. The following tables show the connection from the Digilent 2E Board to the LEDs on the DIO1 Board expressed as UCF constraints. Description NET SEGA NET SEGB NET SEGC NET SEGD NET SEGE NET SEGF NET SEGG NET SEGDP Location LOC=P127 LOC=P132 LOC=P134 LOC=P136 LOC=P139 LOC=P141 LOC=P146 LOC=P148

Table 1: Connections between DIO1 7-Segment display and Digilent 2E

Description NET LD < 1 > NET LD < 2 > NET LD < 3 > NET LD < 4 > NET LD < 5 > NET LD < 6 > NET LD < 7 > NET LD < 8 >

Location LOC=P154 LOC=P161 LOC=P163 LOC=P165 LOC=P167 LOC=P169 LOC=P174 LOC=P176

Table 2: Connections between the DIO1 LEDs and Digilent 2E

Description NET SW < 1 > NET SW < 2 > NET SW < 3 > NET SW < 4 > NET SW < 5 > NET SW < 6 > NET SW < 7 > NET SW < 8 >

Location LOC=P126 LOC=P129 LOC=P133 LOC=P135 LOC=P138 LOC=P140 LOC=P145 LOC=P147

Table 3: Connections between the DIO1 slide switches and Digilent 2E Description NET BTN < 1 > NET BTN < 2 > NET BTN < 3 > NET BTN < 4 > NET BTN < 5 > Location LOC=P149 LOC=P150 LOC=P151 LOC=P152 LOC=P178

Table 4: Connections between the DIO1 pushbuttons and Digilent 2E

9.2

Switches

The DIO1 has bank of eight slide switches and ve pushbuttons (labeled BTN1 through BTN5) that are accessible from an Digilent 2E Board. When closed or ON, each DIP switch pulls the connected pin of the D2E Board to ground. When the DIP switch is open or OFF, the pin is pulled high through a 10K resistor. When pressed, each pushbutton pulls the connected pin of the D2E Board to ground. Otherwise, the pin is pulled high through a 10K resistor. The table below show the connections from the Digilent D2E Board to the switches on the Digilent IO1 Board expressed as UCF constraints.

Вам также может понравиться

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- 11 Ramp Generators PDFДокумент50 страниц11 Ramp Generators PDFAntonОценок пока нет

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Clipping ClampingДокумент12 страницClipping ClampingmanojpeehuОценок пока нет

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Datasheet Navio Board PDFДокумент2 страницыDatasheet Navio Board PDFluckyluck00100% (1)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Whirlpool Awod 41135Документ20 страницWhirlpool Awod 41135smara_1009Оценок пока нет

- Pic16f887 MicrocontrollerДокумент12 страницPic16f887 MicrocontrollerShameerОценок пока нет

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- Microprocessors and Peripheral Devices - PDF NotesДокумент70 страницMicroprocessors and Peripheral Devices - PDF Noteszsarthak99Оценок пока нет

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- ORO551 Renewable Energy Sources QB 3Документ2 страницыORO551 Renewable Energy Sources QB 3Nallappan Rajj AОценок пока нет

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- EEL Product BriefДокумент4 страницыEEL Product BriefHaroon ShaikhОценок пока нет

- LM20020 A AHF AHK Installation Instructions 02 15Документ12 страницLM20020 A AHF AHK Installation Instructions 02 15Lisa TerzoОценок пока нет

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- AKTU - Even Sem - Virtual Lab Mapping2Документ73 страницыAKTU - Even Sem - Virtual Lab Mapping2anuragОценок пока нет

- Aquaforce: Summary Performance Report For Ch-1-Cu-AlДокумент6 страницAquaforce: Summary Performance Report For Ch-1-Cu-AlHVAC SimplifiedОценок пока нет

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Dynamics of Linear Systems PDFДокумент3 страницыDynamics of Linear Systems PDFBhautik Daxini100% (2)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Infineon TLE8386 DS v01 - 00 enДокумент32 страницыInfineon TLE8386 DS v01 - 00 enbetodias30Оценок пока нет

- Tanfilm Chip Carrier Resistor Network: Electrical DataДокумент4 страницыTanfilm Chip Carrier Resistor Network: Electrical Datantan10Оценок пока нет

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- Bgy85 Catv AmplifierДокумент8 страницBgy85 Catv Amplifiercriman45Оценок пока нет

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- fs9001 PDFДокумент16 страницfs9001 PDFforoОценок пока нет

- Laptop & Desktop Motherboard Chip Level 2 Repairing - NYX TechnologiesДокумент6 страницLaptop & Desktop Motherboard Chip Level 2 Repairing - NYX TechnologiesRamalingam Rathinasabapathy EllappanОценок пока нет

- High Voltage Engineering (EEE-491) : Course Teacher: Fahim Mahmud Lecturer Department of EEE, CUETДокумент17 страницHigh Voltage Engineering (EEE-491) : Course Teacher: Fahim Mahmud Lecturer Department of EEE, CUETMD. MAHADI HASAN SAJIB 1602124Оценок пока нет

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- Scalar Wave Medicine PDFДокумент20 страницScalar Wave Medicine PDFsadiku100% (2)

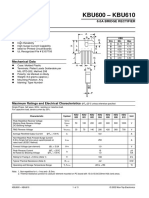

- KBU608Документ4 страницыKBU608José AdelinoОценок пока нет

- ENO-1612 ENO 1612: - Power The World With Highest EfficiencyДокумент2 страницыENO-1612 ENO 1612: - Power The World With Highest Efficiencyrobsontecladista4164Оценок пока нет

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- Be1-Flex (Uub)Документ2 страницыBe1-Flex (Uub)Eliyanto E BudiartoОценок пока нет

- RAN3308: Flexi RFM 3T6R 2100Документ2 страницыRAN3308: Flexi RFM 3T6R 2100Reza BordbarОценок пока нет

- HOVERДокумент297 страницHOVERWilmerOswaldoVeraQuintanaОценок пока нет

- Lios en - Sure: Power Cable MonitoringДокумент2 страницыLios en - Sure: Power Cable MonitoringM KhОценок пока нет

- MAX30105 High-Sensitivity Optical Sensor For Smoke Detection ApplicationsДокумент35 страницMAX30105 High-Sensitivity Optical Sensor For Smoke Detection ApplicationsAvima HaameshaОценок пока нет

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- Product Data Sheet 6ES7214-1BD23-0XB0Документ6 страницProduct Data Sheet 6ES7214-1BD23-0XB0essameldinОценок пока нет

- Pw5 Transformer v1Документ5 страницPw5 Transformer v1Hairul Anuar MasrolОценок пока нет

- 9300.97 12-13-19 XFIIRE Models 300B - 1000B Type H & WH IPLДокумент7 страниц9300.97 12-13-19 XFIIRE Models 300B - 1000B Type H & WH IPLHector FajardoОценок пока нет

- DH87RL ManualДокумент87 страницDH87RL ManualRichard TroianoОценок пока нет