Академический Документы

Профессиональный Документы

Культура Документы

Micros

Загружено:

Cesar Eljure RoselАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Micros

Загружено:

Cesar Eljure RoselАвторское право:

Доступные форматы

Memorias El bus de direcciones es 2n 1k=210 Microprocesador: Es el encargado de procesar la informacin se usa en la computadora (es el cerebro de la computadora) Microcontrolador: el que

toma las decisiones se encarga del control La memoria se divide en principal y auxiliar La principal es RAM Y ROM. La RAM puede ser esttica o dinmica. La esttica es hecha con flipflop y la dinmica con capacitores. Firmware: sistema bsico de entrada y salida es el BIOS Memoria real: Memoria RAM real que tenemos para trabajar con la que cuenta fsicamente la PC Memoria virtual: cuando se toma parte de la memoria del disco duro para usarla como memoria RAM Swapping: proceso en el que se da el intercambio de informacin entre la memoria real y la memoria virtual Stack: rea de memoria (pila de datos) RAM donde se guarda la informacin al revs Pgina de memoria: pedazos de memoria numerados y del mismo tamao Segmentos: contienen el mismo tipo de informacin de longitud variable

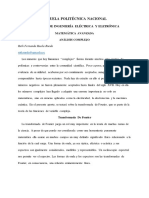

EU(EXECUTION UNID)

BIU(BUS INTERFACE UNID)

AX BX CX DX BP SP DI SI ALU

CS DS SS ES IP

B U S D E D I R E C C I O N E S

B U S D E C O N T R O L

B U S D E D A T O S

UNIDAD DE CONTROL

FLAGS

COLA DE INSTRUCCIONES

Memoria cach: memoria extra muy rpida entre el microprocesador y la memoria RAM, es chica utilizada para guardar instrucciones o datos que se utilizan mucho

Para el mapeo se divide 16 entre el numero despus de la x por ejemplo para una de 2kx8 abran 2 memorias una de que va de d0-d7 y una de d8-d15 Poner en binario el rango hacer el mapeo segn la direccin pasarla a binario pinto mi raya antes de la pata que corresponda por ejemplo 1k = 10 patas pinto mi raya al final de A9 y la diez me sirve para seleccionar. En base eso hago mi decoder dibujo mi latch (mis direcciones van de a0 a a9) conecto ALE a mi enable del latch (al latch solo van direcciones y salen direcciones) se conecta la pata que me sirve para elegir cual memoria al Chip select el RD del micro va al RD de la memoria y el wr al wr la salida del latch va a las direcciones de la memoria el bus de datos de la memoria se divide en 4 paquetes de 4 bits. Porque el bus de datos es de 16 se divide entre los ltimos dos dgitos 16 entre los otros ltimos dos nmeros para saber cuntos paquetes A0-A15 bus de datos A0-A19 bus de direcciones Hold pone al micro en tercer estado para la solicitud de buses Hlda activa el reconocimiento de solicitud de buses M/I0 si esa en 1 trabaja con la memoria si esta en 0 es un dispositivo de entrada y salida DT/R para hacer transferencias con dispositivos lentos Data enable: cuando est activa funciona como dato Ale= si esta activa es una direccin Inta: sirve para decirle al dispositivo si acepta o no la interrupcin Lock: cuando no va a aceptar los buses

Modos de direccionamiento: modo o forma en que el micro accesa a los operandos Modo de registro: el operando est en un registro Modo inmediato: cuando se da el dato directamente viene explcito en la instruccin MOV AX,10H Modo directo: cuando se da la direccin de la localidad de la memoria donde est el dato

Modo indexado: cuando el operando se encuentra en memoria en una tabla de datos se pone entre corchetes Modo implcito: no tengo que especificar operando ya sabe cmo va a trabajar Modo relativo dependiendo de la direccin en la que me encuentro es a la que voy a ir (se refiere a los saltos) Modo base indexado: usa los registros base e indexado MOV AX,NUMEROS[BX+SI]

Cola de instrucciones La cola de instrucciones es una pila de tipo FIFO (primero en entrar, primero en salir) donde las instrucciones son almacenadas antes de que la unidad de ejecucin las ejecute AX (Acumulador) Este registro es el encargado de almacenar el resultado de algunas operaciones aritmticas y lgicas. BX (Base) Este registro es utilizado para calcular direcciones relativas de datos en la memoria. CX (Contador) Su funcin principal es la de almacenar el nmero de veces que un ciclo de instrucciones debe repetirse. DX (Datos) Por lo general se utiliza para acceder a las variables almacenadas en la memoria Existen dos registros llamados SI y DI que estn estrechamente ligados con operaciones de cadenas de datos. SI (ndice Fuente) Proporciona la direccin inicial para que una cadena sea manipulada. DI (ndice Destino) Proporciona la direccin de destino donde por lo general una cadena ser almacenada despus de alguna operacin de transferencia. Registros de segmento El 8086 cuenta con cuatro registros especiales llamados registros de segmento. CS (Segmento de cdigo) Contiene la direccin base del lugar donde inicia el programa almacenado en memoria. DS (Segmento de datos) Contiene la direccin base del lugar del rea de memoria donde fueron almacenadas las variables del programa. ES (Segmento extra) Este registro por lo general contiene la misma direccin que el registro DS. SS (Segmento de Pila) Contiene la direccin base del lugar donde inicia el rea de memoria reservada para la pila. Registro apuntador de instrucciones IP (Apuntador de instrucciones) Este registro contiene la direccin de desplazamiento del lugar de memoria donde est la siguiente instruccin que ser ejecutada por el microprocesador.

Hay distintas formas de identificar la fuente de una determinada interrupcin. La primera alternativa que se consider fue asignar una lnea (un bit) para cada interrupcin pero esto supona un gran costo en cuanto a la relacin de nmero de dispositivos y nmero de bits

usados y a menudo fijaba el lmite de dispositivos que se podan conectar. Por tanto, se pens con posterioridad que en cada patilla de interrupcin deberan poder conectarse ms de un dispositivo, pero entonces tendramos que imponer una metodologa que permitiese identificar de forma unvoca de qu dispositivo se trataba. Para ello hay varias directrices: Polling. Se trata de que la CPU comprueba de manera sistemtica todos los dispositivos de manera que "busca" cul de ellos fue el que solicit la interrupcin. Esto tiene una ventaja y es que es barato a nivel de coste hardware ya que el "polling" se implementa en software, no obstante tiene otras desventajas que no podemos olvidar y es que suele ser lento porque tiene que comprobar en serie todos los dispositivos y establece una prioridad en los dispositivos (el orden de sondeo) y por tanto puede provocar inanicin.

Вам также может понравиться

- Problema Resuelto No1Документ2 страницыProblema Resuelto No1shemonick zambranoОценок пока нет

- Especificaciones TecnicasДокумент2 страницыEspecificaciones TecnicasLlxNelsonxllCutimboОценок пока нет

- 1TMF202006R1250 Ar fh202 Ac 25 0 03Документ3 страницы1TMF202006R1250 Ar fh202 Ac 25 0 03Jose LopezОценок пока нет

- La Mini Bobina de TeslaДокумент3 страницыLa Mini Bobina de TeslaPaul Apaza RamosОценок пока нет

- Precios Sicodi 2009Документ305 страницPrecios Sicodi 2009Johnny Ninantay TorresОценок пока нет

- Lab 6 F.-C.E.IДокумент9 страницLab 6 F.-C.E.IJesus QVasquezОценок пока нет

- E-BOOK - Fallas en Sistemas Electricos de PotenciaДокумент130 страницE-BOOK - Fallas en Sistemas Electricos de PotenciaWalfer Orlando Bolos FloresОценок пока нет

- Oximetro de Pulso Nellcor Oximax N-65Документ2 страницыOximetro de Pulso Nellcor Oximax N-65sermedОценок пока нет

- Specsheet Pararrayos PDFДокумент2 страницыSpecsheet Pararrayos PDFingguedezandresОценок пока нет

- Taller3 IE 2018 NuevoДокумент8 страницTaller3 IE 2018 NuevoEddy Yohanna Martinez RoaОценок пока нет

- Torres de San Ignacio Memoria TecnicaДокумент23 страницыTorres de San Ignacio Memoria TecnicaDianaОценок пока нет

- Historia de Las ComputadorasДокумент2 страницыHistoria de Las ComputadorasErandyОценок пока нет

- Lab 3-Caracterización de Elementos de CircuitosДокумент16 страницLab 3-Caracterización de Elementos de CircuitosDani Medina B'Оценок пока нет

- Ud1 TESTДокумент2 страницыUd1 TESTEduardo García RoblesОценок пока нет

- Medida de La Conductividad Eléctrica de MetalesДокумент6 страницMedida de La Conductividad Eléctrica de MetalesdarkjakОценок пока нет

- Caso Practico de Inspeccion VisualДокумент6 страницCaso Practico de Inspeccion VisualJuan Carlos Ramírez Chaírez0% (1)

- Memoria de Calculo Mecánico de ConductoresДокумент35 страницMemoria de Calculo Mecánico de ConductoresCesar Antonio Pareja VasquezОценок пока нет

- Ruth Rueda Aporte Analisis ComplejoДокумент3 страницыRuth Rueda Aporte Analisis ComplejoFerni_3rОценок пока нет

- Electrónica - Semana 4 - PДокумент5 страницElectrónica - Semana 4 - PSjd SjdОценок пока нет

- Informe #9 - Laboratorio Sistemas de Control II - Rondinel Buleje IvanДокумент11 страницInforme #9 - Laboratorio Sistemas de Control II - Rondinel Buleje IvanIvan Rondinel BulejeОценок пока нет

- INFORME N°9-Circuitos Electronicos IIДокумент14 страницINFORME N°9-Circuitos Electronicos IICarlosОценок пока нет

- 019-IT-VpVc-001 Informe Med Voltaje de Paso y Contacto PFV Luders Rev 0Документ7 страниц019-IT-VpVc-001 Informe Med Voltaje de Paso y Contacto PFV Luders Rev 0Angelo ZapataОценок пока нет

- Memoria DescriptivaДокумент12 страницMemoria DescriptivaCarlos Junior Nole IzquierdoОценок пока нет

- Ondas Senoidales. CaracterísticasДокумент6 страницOndas Senoidales. CaracterísticasglamaizveОценок пока нет

- Informe Practica 4 PotenciaДокумент3 страницыInforme Practica 4 Potenciahernan contrerasОценок пока нет

- Weatc2n EsДокумент23 страницыWeatc2n EsKROWN33Оценок пока нет

- Manual de Uso Sekur 2014Документ205 страницManual de Uso Sekur 2014Richard Espinola DuarteОценок пока нет

- Informe Previo SimulacionesДокумент27 страницInforme Previo SimulacionesLUIS KEVIN ZORIA TACILLAОценок пока нет

- Semana 3 - Átomo de Bohr-Números Cuánticos Configuración ElectrónicaДокумент24 страницыSemana 3 - Átomo de Bohr-Números Cuánticos Configuración ElectrónicaKenny SantaanaОценок пока нет