Академический Документы

Профессиональный Документы

Культура Документы

Decimation 2

Загружено:

Preeti SharmaИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Decimation 2

Загружено:

Preeti SharmaАвторское право:

Доступные форматы

558

IEEE TRANSACTIONS ON WIRELESS COMMUNICATIONS, VOL. 1, NO. 4, OCTOBER 2002

On Design and Implementation of a Decimation Filter for Multistandard Wireless Transceivers

Adel Ghazel, Senior Member, IEEE, Lirida Naviner, Member, IEEE, and Khaled Grati, Student Member, IEEE

AbstractIn this work, we deal with the design and implementation of a decimation filter to be used in wideband radio-frequency receiver. The paper outlines architecture considerations for multistandard wireless transceivers. Also, it describes the design steps and the tradeoffs concerning the hardware implementation. GSM and DECT standards specifications are met by the proposed filtering cascade structure. The filter processes six-bits data stream input from a fourth-order sigmadelta modulator and has been prototyped in a field-programmable gate array device. Index TermsDecimation filtering, hardware implementation, sigmadelta conversion, wireless communications.

I. INTRODUCTION HE development of single-chip receivers became absolutely necessary in the last years. In fact, an expanding growth of wireless communications systems accomplished of a multitude of standards has been observed [1][3]. Moreover, the competitive market imposes low-cost and low-power devices working with several standards. In order to assure the adaptability to different standards, digital processing is more advisable than analog processing. In reception process, when analog-to-digital conversion is performed before channel selection, it covers severe specifications due to the presence of strong adjacent channel blockers along with the desired signal. Because of the high in-band signal-to-noise ratio (SNR) proposed by sigmadelta converter, this kind of converter is currently included in transceivers schemes [4], [5]. Sigmadelta converters are designed to shape the noise away from the band of interest [6]. This oversampling based technique supposes the use of a digital filter to prevent quantization noise aliasing during sampling rate decreasing. This decimator filter needs to perform both filtering of the out of band quantization noise and the adjacent channel blockers. It means that is required from the filter design to exhibit a high-dynamic range, a programmable bandwidth to accommodate different standards, and precise tuning to select the desired channel within a standard. Decimation filters must be very efficient computationally since the filtering is usually performed at a high rate. Moreover, compactness and cost constraints impose low power and a small chip area.

Manuscript received October 24, 2001; revised December 8, 2001; accepted April 25, 2002. The editor coordinating the review of this paper and approving it for publication is S. S. Lawson. This work was supported in part by the TunisianFrench Technical Collaboration Program. A. Ghazel and K. Grati are with the UTIC, Ecole Suprieure des Communications de Tunis (SUPCOM), 2088 Tunis, Tunisia (e-mail: adel.ghazel@supcom.rnu.tn; khaled.grati@supcom.rnu.tn.). L. Naviner is with the ComElec, Ecole Nationale Suprieure des Tlcommunications de Paris (ENST-Paris), 75634, Paris Cedex 13, France (e-mail: lirida.naviner@enst.fr). Digital Object Identifier 10.1109/TWC.2002.805093

Several design and implementations of decimation filters for sigmadelta converters are presented in recent papers. White and Elmasry have proposed low-power design techniques for multimode multistage decimation filter adapted to both Mobitex and Ardix wireless networks specifications [7]. In their paper, a third order comb filter and a first-stage finite-impulse response (FIR) filter are common to the two standards and only a second-stage FIR filter has coefficients and frequencies depending on the mode. In [8], authors proposed filter structure with decimation and sampling rates adapted to global system for mobile communications (GSM) and digital european cordless telephone (DECT) applications, they described a low power implementation architecture by using nonrecursive architecture for the comb filter and by simplifying FIR filter multiplications to shifts and adds operations. Implementations based on scalability and on the use of the DECOR transformation to reduce power and area of decimation filters are respectively found in [9] and [10]. By considering GSM and DECT standards requirements, FIR and infinite impulse response (IIR) structures of digital filters have been studied, by authors in [11], then, compared in terms of performances and computational complexity. IIR filter solution with almost linear phase is designed and gives good results with less order than FIR filters. But analysis of computational complexity shows that, for a decimation factor less or equal to four, half-band polyphase FIR filters require less number of multiplications since their coefficients are symmetric and odd ones are equal to zero [11]. This paper deals with the design and implementation of a decimation filter to be used in wideband radio-frequency wireless systems. A decimation filter cascade structure is designed to meet the GSM and DECT standards specifications [1], [2] and to be very efficient computationally. Since the computation power depends on the filter order and this one depends on the filter specifications, the authors propose a practical method to look for relaxed filter specifications that take into consideration multistage structure. This paper is organized as follows. Section II deals with the receiver architecture choice. Considerations on filter design and its performance analysis are seen in Section III. Hardware implementation is presented in Section IV. Finally, some conclusions and future work are outlined in Section V. II. RECEIVER ARCHITECTURE CONSIDERATIONS A multistandard wireless system must meet the performance requirements for each standard and adjust to the different channel bandwidths and carrier frequencies. Many receivers architectures have been proposed: the conventional super-heterodyne architecture [12][15], the low intermediate frequency (Low-IF) architecture [4], the wideband intermediate frequency

1536-1276/02$17.00 2002 IEEE

IEEE TRANSACTIONS ON WIRELESS COMMUNICATIONS, VOL. 1, NO. 4, OCTOBER 2002

559

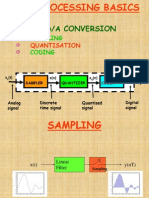

Fig. 2. Multistage decimation filter structure.

Fig. 1.

Direct conversion homodyne receiver.

with double conversion (WIF) architecture [5] and direct homodyne conversion [16], [17]. In this work, we consider the direct homodyne conversion receiver because it eliminates many off-chip components. In homodyne architecture, all of the channels are frequency translated to baseband before any channel filtering is performed [16][19]. Channel selection can be performed in the analog domain or in digital domain. Analog domain channel selection imposes an R-C high dynamic range, highly linear channel select filter and a difficult programmability, but a relatively easy analog-to-digital conversion [20], [21]. Inversely, digital channel selection imposes a high dynamic range of the analog-to-digital converter, but easier possibility of on-chip programmable filter structures to accommodate the variable channel bandwidth [22]. So, digital channel selection has been retained for this work (see Fig. 1). A fourth-order sigmadelta analog-to-digital converter with a 6-b data stream output is considered, with oversampling ratios (OSR) given by 64 (for GSM) and 32 (for DECT). With these oversampling rates, dynamic range requirement of 98 dB for GSM and 85 dB for DECT can be achieved [23]. III. FILTER STRUCTURE AND DESIGN Specification of the filter consists on specification of sam, passband frequency , stopband frepling frequency , transition band , passband ripples quency , stopband ripples and phase linearity. The stopband frequency is the half of the Nyquist rate. The ). Knowledge passband is as large as possible (ideally of the transmission processing allows efficient design by pertinently limit the passband. In fact, filters in the transmitter reduce effective information band. Passband ripples is dependent of the modulation scheme used in the transmission. Suppleness is obtained if the information is not on the signal amplitude (but on the frequency/phase). Stopband ripples is in report with the total noise present in the stopband (quantization noise and blockers/interferers channels). Many bands may be defined in order to optimize the stopband requirements, each one composed by blockers/interferers channels and quantization noise. If only one stopband is considered, the attenuation must to be enough to reduce the worst case blocker noise power according to carrier-to-noise radio (CNR) requirements [24]. The performance of a decimation filter depends on the type, the order, and the architecture of the filter. The filter order depends on the ratio between width of transition band and of the filter (see [25, eq. (1)]) sampling frequency (1) where function depending on and

Because sigmadelta converters are oversampled, carries to high order filters and so too high power computation. To overcome this problem, the filter can be implemented in a multistage approach [23]. Each stage implements a part of the filtering and is followed by a down sampling. The filters running at higher sampling rates have larger transition bands and filters presenting narrower transition bands run at lower sampling rates, carrying to lower overall computation needs. Both output noise power and decimation filter passband ripples can be calculated at the end of each stage using an equivalent low-pass transfer function and classic techniques of digital filtering processing [25]. Comb filters are very interesting for first-stage of decimation process because they need no multiplier (see [26, eq. (2)]). Unfortunately, they present two drawbacks: an insufficient attenuation in stopband and distortion in passband. Insufficient attenuation in stop band can be overcome by cascading several filters. Using a corrector filter can compensate distortion in passband. (2) The comb filter is an efficient way to decimate the converter output to four times the Nyquist rate [26]. For the remaining four times of decimation, previous works used a cascade composed of two half-band filters and a corrector FIR filter [8], [11], [27], [28]. After analyzing other possible filtering structures a low computation complexity for required specifications is obtained with a cascade structure composed of Comb filter followed by one half band filter and a FIR filter (Fig. 2). Because we consider a sigmadelta modulator with order , a cascade of comb filters is necessary [23]. This comb cascade performs a decimation for the GSM and for the DECT. For factor remaining stages the following method is defined to determine filters specifications. For half-band filter passband frequency is chosen equal is deto channel bandwidth. The stopband frequency . According fined by considering the symmetry to is calcuto blockers profiles the stopband attenuation lated to obtain an attenuation of out-of-band noise 10 dB below noise present in transition band. According to interis calculated ferers profiles the stopband attenuation to obtain an attenuation of in band aliased noise 10 dB below signal level. The worst case is considered for filter attenuation. is chosen For last stage FIR filter passband frequency equal to 82% channel bandwidth. The transition band is from 82% to 100% channel bandwidth. According to blockers and interferes profiles the stopband attenuation is calculated in order to obtain required CNR by considering in-band signal power and power of noise components aliased into Nyquist band. The worst case is considered for filter attenuation.

560

IEEE TRANSACTIONS ON WIRELESS COMMUNICATIONS, VOL. 1, NO. 4, OCTOBER 2002

Fig. 3. GSM and DECT blockers and interferers specifications at receiver antenna input.

Fig. 4. Comb filter implementation architecture.

By applying this method for decimation filters design to meet the carrier to noise requirement for the worst case blocking profile and adjacent channel interferers for GSM and DECT standards (Fig. 3) the following specifications are obtained for each filter. Half-band filter stage: For GSM standard, a transition dB band of 100 kHz and a stopband rejection of are considered. For DECT standard, a transition band dB are of 700 kHz and a stopband rejection of considered. FIR filter stage: For GSM standard, a transition band of dB are considered. 18 kHz and a stopband rejection of For DECT standard, a transition band of 126 kHz and a dB are considered. stopband rejection of

Fig. 5. FIR filter implementation architecture.

IV. FILTER IMPLEMENTATION CONSIDERATIONS Comb filter can be efficiently implemented by separating its into numerator and denominator secmagnitude response tions and by moving the numerator section after the down-sampling operation (Fig. 4). The denominator is a cascade of accumulators and the numerator is a cascade of subtractors. A 2s complement wrap-around arithmetic is used to avoid overflow problem as long as the register width is greater or equal to value given by (3) (3)

Half-band and FIR filters can be efficiently implemented with a polyphase direct-form filter, which allows the filter to run at the decimated rate instead of the input rate, reducing the computation complexity by approximately one-half. For FIR filters, which are based on multiplying operations, three hardware implementations have been envisaged [28]. In the first solution, a generic multiplier is in charge of all data-coefficient products. The second solution uses generic adders for multiplication. The third solution is based on wired adders for each coefficient. The differences among these solutions concern granularity (parallel multiplying for one and serial multiplying for two) and specificity (generality for onetwo and dedicated coefficients for three) of the processing. The filter has been prototyped in a field-programmable gate array (FPGA). FPGAs are composed of basic logic cells (LCELLs) and provide reconfigurable hardware, flexible interconnect, and field-programmable ability. Nevertheless,

IEEE TRANSACTIONS ON WIRELESS COMMUNICATIONS, VOL. 1, NO. 4, OCTOBER 2002

561

Fig. 6.

Experimental performances of decimation filter.

TABLE I FILTERS COMPUTATIONAL RESULTS

of all, we have evaluated the necessary computation power for the processing. After this, we have developed an FPGA-adapted model for the corresponding operators with VHDL. The chosen solution is those satisfying the demanded computation power and carrying to the lowest number of LCELLs. According to experimental results of this study the best compromise between cells number and propagation time, for GSM and DECT filters, is obtained with the generic multiplier-based implementation solution (Fig. 5) (Table I). Fig. 6 presents signal spectrum at the decimation filter input and at the decimation filter output. A 10-bit resolution for filter coefficients digital format representation is considered to represent coefficients variation range (0.05 to 0.451).

V. CONCLUSION In this paper, we have described the architecture, the synthesis and the hardware implementation of a decimation filter designed for 6-bit data stream input, from a fourth-order sigmadelta modulator adapted for multistandard wireless receiver. The prototyped filter is based on fifth-order comb filter, one half-band filter stages and a FIR correction filter. Obtained results show that the use of carry ripple adders allows minimizing LCELL amount for comb filter implementation. For half-band and FIR correction filters, which are based on multiplying operations, a single generic multiplier based architecture is the more suitable solution. Almost all of decimation filters for radio communications related in literature are using FIR filters because of the ease with which exactly linear phase could be achieved. However, linear phase over the entire band is not often required. Future works include looking for a simplified new method to design an almost linear phase IIR filters for a given specification of the allowed phase.

when implementing functions with FPGAs, we need to take into account two important factors: operative granularity and routing resources. Basic logic cells input width determinates the optimal granularity for the input functions to be implemented. Also, limited routing resources can carry to congestion problems, which increases propagation delay and degrades area efficiency. Both these limitations were taken into account in our oriented VHDL modeling [28]. The hardware-optimized implementation has obtained with the following approach. First

562

IEEE TRANSACTIONS ON WIRELESS COMMUNICATIONS, VOL. 1, NO. 4, OCTOBER 2002

REFERENCES

[1] DECT Standard. Document ETSI ETS 300 175-1 Ed.2 (199609). [2] ETSI, Radio Transmission and Reception, GSM 05.05, 1996. [3] UMTS: Universal mobile telecommunications system; user equipment radio transmission and reception (FDD)-3G Tech. Spec., ETSI, 125 101 v3.2.0 (2000-03), 2000. [4] J. Crols and M. Steyaert, A single-chip 900 MHz CMOS receiver front-end with a high performance low-IF topology, IEEE J. Solid-State Circuits, pp. 14831492, Dec. 1995. [5] J. Rudell et al., A 1.9 GHz wideband IF double conversion CMOS integrated receiver for cordless telephone applications, in Int. Solid-State Circuits Conf., vol. 8, June 2000, pp. 20712088. [6] J. C. Candy, Decimation for sigma-delta modulation, IEEE Trans. Commun., vol. COM-34, pp. 7276, Jan. 1986. [7] B.-A. White and M. I. Elmasry, Low-power design of decimation filters for a digital IF receiver, IEEE Trans. VLSI Syst., vol. 8, pp. 339345, June 2000. [8] Y. Gao, L. Jia, and H. Tejhumen, A fifth-order comb decimation filter for multistandard transceiver applications, presented at the IEEE Int. Symp. Circuits and Systems, Geneva, Switzerland, May 2000. [9] P. C. Maulik, M. S. Chadha, W. L. Lee, and P. J. Crawley, A 16-bit 250 kHz delta-sigma modulator and decimation filter, IEEE J. Solid-State Circuits, vol. 35, pp. 458467, Apr. 2000. [10] D. Seo, N.-R. Shanbhag, and M. Feng, Low-power decimation filters for over-sampling ADCs via the decorrelating (DECOR) transform, presented at the IEEE Int. Symp. Circuits Systems, Geneva, Switzerland, May 2000. [11] K. Grati, A. Ghazel, L. Naviner, and S. Tabbane, Comparison of FIR and IIR structures for decimation filtering in radio communications, presented at the 5th Multi-Conf. Systemics, Cyb. and Informatics, Orlando, FL, July 2001. [12] T. Stetzler et al., A 2.7 V to 4.5 V single-chip GSM transceiver RF integrated circuit, presented at the IEEE Int. Solid-State Circuits Conf.-Dig. Tech. Papers, San Francisco, CA, 1995. [13] K. Irie et al., A 2.7 V GSM RF transceiver IC, presented at the IEEE Int. Solids-State Circuits Conf., San Francisco, CA, Feb. 1997. [14] L. Der and B. Razavi, A 2 GHz CMOS image-reject receiver with sign-sign LMS calibration, presented at the IEEE Int. Solid-State Circuits Conf., San Francisco, CA, 2001. [15] S. Hisayasu et al., A 1.9 GHz single-chip if transceiver for digital cordless phones, presented at the Int. Solid-State Circuits Conf.-Dig. Tech. Papers, San Francisco, CA, 1996.

[16] J. Sevenhans et al., An integrated Si bipolar RF transceiver for a zero IF 900 MHz GSM digital mobile radio front end of a hand portable phone, in Proc. 5th Annu. IEEE Int. ASIC Conf. Exhibit, 1992, pp. 561564. [17] C. Hull, J. L. Tham, and R. R. Chu, A direct-conversion receiver for 900 MHz (ISM band) spread-sectrum digital cordless telephone, in Proc. IEEE Int. Solid-State Circuits Conf., Dec. 1996, pp. 19551963. [18] M. Masegawa, T. Fukagawa, M. Mimura, and M. Makimoto, Homodyne receiver technology for small and low-power consumption mobile communications equipment, presented at the Int. Symp. Signals, Systems Electronics, San Francisco, CA, 1995. [19] A. Abidi, A. Rofougaran, G. Chang, J. Rael, J. Chang, M. Rofougaran, and P. Chang, The future of CMOS wireless transceivers, in Proc. IEEE Int. Solid-State Circuits Conf., Feb. 1997, pp. 118119. [20] H. Khorramabadi, M. J. Tarsia, and N. S. Woo, Baseband filters for IS-95 CDMA receiver aplications featuring digital automatic frequency tuning, in Proc. IEEE Int. Solid-State Circuits Conf., Feb. 1996, pp. 172173. [21] T. Cho et al., A power-optimized CMOS baseband channel filter and ADC for cordless applications, in Proc. Symp. VLSI Circuits, Jan. 1996, pp. 6465. [22] A. Feldman, High-Speed, Low-Power Sigma-Delta Modulators for RF Baseband Channel Applications. Berkeley, CA: Univ. California, 1997. [23] S. R. Norsworthy and R. E. Crochiere, Decimation and interpolation for sigma delta conversion, in Delta Sigma Data Converters. Piscataway, NJ: IEEE Press, 1997. [24] L. Naviner and P. Loumeau, A method to specify sigma delta converters in radio receivers, presented at the IEEE 8th Int. Conf. MIXDES2001, Zakopane, Pologne, 2001. [25] R. E. Crochiere and L. R. Rabiner, Multirate Digital Signal Processing. Englewood Cliffs, NJ: Prentice-Hall, 1983. [26] S. Chu and C. S. Burrus, Multirate filter design using Comb filters, IEEE Trans. Circuits Systems, vol. CAS-31, pp. 913924, Nov. 1984. [27] K. Grati, A. Ghazel, L. Naviner, and F. Moatamri, Design and Implementation of Decimation Filter Cascade for Radio Communications, presented at the 8th IEEE Int. Conf. Electronics Circuits Systems, Malta, Sept. 2001. [28] A. Ghazel, L. Naviner, and F. Moatamri, FPGA-based architecture of decimation filter for multistandard wireless transceiver, presented at the Smart Systems Devices Conf., Hammamet, Tunisia, Mar. 2001.

Вам также может понравиться

- Mahesh 2010Документ14 страницMahesh 2010Syfunnisa ShaikОценок пока нет

- Optimized Digital Filter Architectures For Multi-Standard RF TransceiversДокумент15 страницOptimized Digital Filter Architectures For Multi-Standard RF TransceiversvvigyaОценок пока нет

- Comb-Based Decimation Filters For 61 A/D Converters: Novel Schemes and ComparisonsДокумент11 страницComb-Based Decimation Filters For 61 A/D Converters: Novel Schemes and ComparisonsVale Conde CuatzoОценок пока нет

- Software Radio: Sampling Rate Selection, Design and SynchronizationОт EverandSoftware Radio: Sampling Rate Selection, Design and SynchronizationОценок пока нет

- Implementation of SRRC Filter in Mobile Wimax With DWT Based Ofdm SystemДокумент8 страницImplementation of SRRC Filter in Mobile Wimax With DWT Based Ofdm SystemrohitvanОценок пока нет

- International Journal of Engineering Research and Development (IJERD)Документ4 страницыInternational Journal of Engineering Research and Development (IJERD)IJERDОценок пока нет

- International Journal of Engineering Research and Development (IJERD)Документ8 страницInternational Journal of Engineering Research and Development (IJERD)IJERDОценок пока нет

- Welcome To International Journal of Engineering Research and Development (IJERD)Документ11 страницWelcome To International Journal of Engineering Research and Development (IJERD)IJERDОценок пока нет

- LTE Coverage Network Planning and Comparison With Different Propagation ModelsДокумент10 страницLTE Coverage Network Planning and Comparison With Different Propagation Modelshmalrizzo469Оценок пока нет

- CETCME-2020 - NIET - Vineet ShekherДокумент9 страницCETCME-2020 - NIET - Vineet Shekherडाँ सूर्यदेव चौधरीОценок пока нет

- Design of Proposed STBC-MC-DS - WIMAX Systems Based On DWT and Phase MatrixДокумент10 страницDesign of Proposed STBC-MC-DS - WIMAX Systems Based On DWT and Phase MatrixJournal of TelecommunicationsОценок пока нет

- Wideband Channelization Architectures in ASICs and FPGAsДокумент13 страницWideband Channelization Architectures in ASICs and FPGAsyanivscribdОценок пока нет

- F0283111611-Ijsce Paper - SubirДокумент5 страницF0283111611-Ijsce Paper - SubirSubir MaityОценок пока нет

- A Wideband Digital RF Receiver Front-End Employing A New Discrete-Time Filter For M-WimaxДокумент10 страницA Wideband Digital RF Receiver Front-End Employing A New Discrete-Time Filter For M-WimaxFarhan AliОценок пока нет

- A Seminar Report: Department of Electronics & CommunicationsДокумент7 страницA Seminar Report: Department of Electronics & CommunicationsVipul PatelОценок пока нет

- Characteristics of Digital Fixed Wireless Systems Below About 17 GHZДокумент24 страницыCharacteristics of Digital Fixed Wireless Systems Below About 17 GHZBoy azОценок пока нет

- DiplexerДокумент5 страницDiplexertamilarasansrtОценок пока нет

- A Novel Low Cost Microstrip Bandpass FilДокумент8 страницA Novel Low Cost Microstrip Bandpass FilAllam Naveen Kumar 21MCE0006Оценок пока нет

- VLSI Design of Half-Band IIR Interpolation and Decimation FilterДокумент7 страницVLSI Design of Half-Band IIR Interpolation and Decimation FiltertansnvarmaОценок пока нет

- Design of STBC-WIMAX System by Using DWT With Four Transmit Antennas in Fading ChannelДокумент10 страницDesign of STBC-WIMAX System by Using DWT With Four Transmit Antennas in Fading ChannelJournal of TelecommunicationsОценок пока нет

- Electronics: Compact Low-Cost Filter For 5G Interference Reduction in UHF Broadcasting BandДокумент14 страницElectronics: Compact Low-Cost Filter For 5G Interference Reduction in UHF Broadcasting BandIkie BarieОценок пока нет

- 173-Article Text-490-1-10-20181113 - 2Документ9 страниц173-Article Text-490-1-10-20181113 - 2Fa Mido ChemseddineОценок пока нет

- Coverage/Capacity Analysis For 4 Generation Long Term Evolution (Lte)Документ6 страницCoverage/Capacity Analysis For 4 Generation Long Term Evolution (Lte)Alit Putra WijayaОценок пока нет

- Tunable NPath NotchFilter ForBlockerSuppression 11489294Документ31 страницаTunable NPath NotchFilter ForBlockerSuppression 11489294AnindyaSahaОценок пока нет

- BROAD BAND ACCESS (Wired and Wireless)Документ31 страницаBROAD BAND ACCESS (Wired and Wireless)Apeksha KulkarniОценок пока нет

- OFDM Simulator Using MATLAB: International Journal of Emerging Technology and Advanced EngineeringДокумент4 страницыOFDM Simulator Using MATLAB: International Journal of Emerging Technology and Advanced Engineeringhungpm2013Оценок пока нет

- SDR Applications Using VLSI Design of Reconfigurable DevicesДокумент6 страницSDR Applications Using VLSI Design of Reconfigurable DevicesSteveОценок пока нет

- Single-Carrier Modulation Versus OFDM For Millimeter-Wave Wireless MIMOДокумент14 страницSingle-Carrier Modulation Versus OFDM For Millimeter-Wave Wireless MIMOcompluuytthiex hmjjiuyytОценок пока нет

- Project Proposal - Comparison Microwave Low Pass FilterДокумент17 страницProject Proposal - Comparison Microwave Low Pass FilterJubril AkinwandeОценок пока нет

- LTE Coverage Network Planning and Comparison With Different Propagation ModelsДокумент10 страницLTE Coverage Network Planning and Comparison With Different Propagation ModelszakiОценок пока нет

- A Miniaturized Bandpass Filter Using Microstrip LinesДокумент5 страницA Miniaturized Bandpass Filter Using Microstrip LinesThierno Amadou Mouctar BaldeОценок пока нет

- FPGA Implementation of OFDM PDFДокумент6 страницFPGA Implementation of OFDM PDFFausto Paco ValenzuelaОценок пока нет

- Microwave Front-End Subsystems Design For ITSGPS AДокумент11 страницMicrowave Front-End Subsystems Design For ITSGPS AyyryОценок пока нет

- Papr Reduction Techniques and Their Bit Error Rate Measurement at Ofdm in Lte SystemДокумент16 страницPapr Reduction Techniques and Their Bit Error Rate Measurement at Ofdm in Lte SystemijansjournalОценок пока нет

- 1-Bandwidth Enhancement in Band Pass Filter BPF Using Microstrip Couple Lines For WLAN 2.4GHZ ApplicationsДокумент4 страницы1-Bandwidth Enhancement in Band Pass Filter BPF Using Microstrip Couple Lines For WLAN 2.4GHZ ApplicationsJohn JohnОценок пока нет

- Bandpass Continuous-Time Delta-Sigma Modulator For Wireless Receiver ICДокумент4 страницыBandpass Continuous-Time Delta-Sigma Modulator For Wireless Receiver ICBalthier8745Оценок пока нет

- Comparative Study of Ofdm and Cdma Technique: Lalit Singh Garia, Amit Shah, Deepesh RawatДокумент5 страницComparative Study of Ofdm and Cdma Technique: Lalit Singh Garia, Amit Shah, Deepesh RawatInternational Organization of Scientific Research (IOSR)Оценок пока нет

- The 3g Long-Term Evolution Radi Interface PDFДокумент5 страницThe 3g Long-Term Evolution Radi Interface PDFSehat SitorusОценок пока нет

- Ofdm PDFДокумент5 страницOfdm PDFnikitajanu100% (1)

- A Survey On Reconfigurable Architecture Based On Fpga For Ofdm TransmitterДокумент6 страницA Survey On Reconfigurable Architecture Based On Fpga For Ofdm TransmitterSanjay ShelarОценок пока нет

- Interference Cancelation Scheme WithДокумент10 страницInterference Cancelation Scheme WithhosamkhaledОценок пока нет

- LTE RF Design and OptimizationДокумент33 страницыLTE RF Design and Optimizationashu17100% (5)

- DectДокумент18 страницDectmkiran02Оценок пока нет

- Department of ECE, RNSITДокумент10 страницDepartment of ECE, RNSITNischita KeerthiОценок пока нет

- Microwave Filters-Applications and TechnologyДокумент12 страницMicrowave Filters-Applications and Technologyalokcena007Оценок пока нет

- Transmit Antenna Selection Strategies For SC-FDMA - IDMA Massive MIMO SystemsДокумент8 страницTransmit Antenna Selection Strategies For SC-FDMA - IDMA Massive MIMO SystemsRoopali AgarwalОценок пока нет

- Design of Microstrip Hairpin Bandpass Filter For X-Band Radar NavigationДокумент6 страницDesign of Microstrip Hairpin Bandpass Filter For X-Band Radar Navigationtrance 2k17Оценок пока нет

- Improving The System Spectral EfficiencyДокумент5 страницImproving The System Spectral Efficiencypchopade1238374Оценок пока нет

- Design of Microstrip Dual-Band Filter Using Short-Circuited SIRДокумент5 страницDesign of Microstrip Dual-Band Filter Using Short-Circuited SIRerpublicationОценок пока нет

- RF Integrated Circuits in Standard CMOS TechnologiesДокумент8 страницRF Integrated Circuits in Standard CMOS TechnologiesSaitejaTallapellyОценок пока нет

- Cdma Air Interface Overview: 2.1 Cellular Wireless CommunicationsДокумент22 страницыCdma Air Interface Overview: 2.1 Cellular Wireless CommunicationsSub Divisional Engineer MGGОценок пока нет

- Paper PpuДокумент8 страницPaper Ppusachin10dulkarОценок пока нет

- An Economical Class of Digital Filters For Decimation and Interpolation-FoLДокумент8 страницAn Economical Class of Digital Filters For Decimation and Interpolation-FoLKishlay KumarОценок пока нет

- Indoor Radio Planning: A Practical Guide for 2G, 3G and 4GОт EverandIndoor Radio Planning: A Practical Guide for 2G, 3G and 4GРейтинг: 5 из 5 звезд5/5 (1)

- 01 Abhijit GuptaДокумент5 страниц01 Abhijit GuptagabhiguptaОценок пока нет

- Microwave and Millimeter Wave Circuits and Systems: Emerging Design, Technologies and ApplicationsОт EverandMicrowave and Millimeter Wave Circuits and Systems: Emerging Design, Technologies and ApplicationsОценок пока нет

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDОт EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDОценок пока нет

- Multirate Signal ProcessingДокумент33 страницыMultirate Signal ProcessingSharath PadaruОценок пока нет

- Real-Time Time-Domain Pitch Tracking Using WaveletsДокумент12 страницReal-Time Time-Domain Pitch Tracking Using WaveletsyoudiezОценок пока нет

- Sti Pav 4 ComplianceДокумент7 страницSti Pav 4 ComplianceDaniel AndoziaОценок пока нет

- Sampling and Multirate Techniques For Complex and Bandpass SignalsДокумент58 страницSampling and Multirate Techniques For Complex and Bandpass SignalsRomualdo Begale PrudêncioОценок пока нет

- 14 Interpolation DecimationДокумент32 страницы14 Interpolation Decimationleenu123Оценок пока нет

- M.Tech Degree I Semester Examination in Electronics: (Signal Processing)Документ2 страницыM.Tech Degree I Semester Examination in Electronics: (Signal Processing)safu_117Оценок пока нет

- Reyes Et Al. (2017) Fast Nonlinear Response History AnalysisДокумент11 страницReyes Et Al. (2017) Fast Nonlinear Response History Analysisfirai5Оценок пока нет

- A Brief Introduction To Sigma Delta ConversionДокумент7 страницA Brief Introduction To Sigma Delta ConversionraphaelcuecaОценок пока нет

- 14 Interpolation DecimationДокумент32 страницы14 Interpolation DecimationBorominОценок пока нет

- Decimation in TimeДокумент9 страницDecimation in TimeGrisel MoralesОценок пока нет

- Carias Lab4 Ecc311l E51Документ12 страницCarias Lab4 Ecc311l E51CJ Valete JacobОценок пока нет

- EECE/CS 253 Image Processing: Richard Alan Peters IIДокумент44 страницыEECE/CS 253 Image Processing: Richard Alan Peters IIAshoka VanjareОценок пока нет

- Multirate Digital Signal Processing PDFДокумент85 страницMultirate Digital Signal Processing PDFSachita Nand MishraОценок пока нет

- Signal Generation and PreprocessingДокумент15 страницSignal Generation and Preprocessingkarthik2055Оценок пока нет

- DSP SyllabusДокумент2 страницыDSP SyllabuskumarОценок пока нет

- Digital Lab 1Документ14 страницDigital Lab 1MahmoudȜbdElHafizОценок пока нет

- Digital Signal Processing in RF Applications: Thomas SchilcherДокумент44 страницыDigital Signal Processing in RF Applications: Thomas SchilcherletialgoОценок пока нет

- NIT Warangal EEE CurriculumДокумент27 страницNIT Warangal EEE Curriculumjagadeesh_kumar_20Оценок пока нет

- Chapter 13Документ33 страницыChapter 13Mustafa FarragОценок пока нет

- AD1871Документ28 страницAD1871Fredi Carlos AfonsoОценок пока нет

- November-December 2011 R07 ALL in ONEДокумент25 страницNovember-December 2011 R07 ALL in ONEAlwyzz Happie RaamzzОценок пока нет

- Belajar SimulinkДокумент24 страницыBelajar SimulinkRaKa AltecОценок пока нет

- Ex05b - PDSP Question Paper - Te - 1Документ4 страницыEx05b - PDSP Question Paper - Te - 1shankarОценок пока нет

- Sampling TheoremДокумент34 страницыSampling Theoremgaurav_juneja_4Оценок пока нет

- Signals in MatLab PDFДокумент18 страницSignals in MatLab PDFPratik SarkarОценок пока нет

- Implementing Downsampling FIR Filters in Xilinx FPGAsДокумент9 страницImplementing Downsampling FIR Filters in Xilinx FPGAsdegdougОценок пока нет

- Questions & Answers On Multirate Digital Signal ProcesingДокумент7 страницQuestions & Answers On Multirate Digital Signal Procesingkibrom atsbhaОценок пока нет

- Seminar ReportДокумент30 страницSeminar Reportmonty08350% (2)

- DSP Objective Type Type QuestionsДокумент4 страницыDSP Objective Type Type QuestionsRamapriyavlsiОценок пока нет

- DSSSSPДокумент3 страницыDSSSSPChris BalmacedaОценок пока нет