Академический Документы

Профессиональный Документы

Культура Документы

Chuong 12 - LCD - ADC - Cam Bien - Smith.N Studio

Загружено:

Smith Nguyen StudioОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Chuong 12 - LCD - ADC - Cam Bien - Smith.N Studio

Загружено:

Smith Nguyen StudioАвторское право:

Доступные форматы

Smith Nguyen Studio.

Chng 12 Phi ghp vi th gii thc: LCD, ADC v cc cm bin

Chng ny khm ph mt s ng dng ca 8051 vi th gii thc. Chng ta gii thch lm cch no phi ghp 8051 vi cc thit b nh l LCD, ADC v cc cm bin. 12.1 Phi ghp mt LCD vi 8051. phn ny ta s m t cc ch hot ng ca cc LCD v sau m t cch lp trnh v phi ghp mt LCD ti 8051. 12.1.1 Hot ng ca LCD. Trong nhng nm gn y LCD ang ngy cng c s dng rng ri thay th dn cho cc n LED (cc n LED 7 on hay nhiu on). l v cc nguyn nhn sau: 1. Cc LCD c gi thnh h. 2. Kh nng hin th cc s, cc k t v ho tt hn nhiu so vi cc n LED (v cc n LED ch hin th c cc s v mt s k t). 3. Nh kt hp mt b iu khin lm ti vo LCD lm gii phng cho CPU cng vic lm ti LCD. Trong khi n LED phi c lm ti bng CPU (hoc bng cch no ) duy tr vic hin th d liu. 4. D dng lp trnh cho cc k t v ho. 12.1.2 M t cc chn ca LCD. LCD c ni trong mc ny c 14 chn, chc nng ca cc chn c cho trong bng 12.1. V tr ca cc chn c m t trn hnh 12.1 cho nhiu LCD khc nhau. 1. Chn VCC, VSS v VEE: Cc chn VCC, VSS v VEE: Cp dng ngun - 5v v t tng ng th VEE c dng iu khin tng phn ca LCD. 2. Chn chn thanh ghi RS (Register Select). C hai thanh ghi rt quan trng bn trong LCD, chn RS c dng chn cc thanh ghi ny nh sau: Nu RS = 0 th thanh ghi m lnh c chn cho php ngi dng gi mt lnh chng hn nh xo mn hnh, a con tr v u dng v.v Nu RS = 1 th thanh ghi d liu c chn cho php ngi dng gi d liu cn hin th trn LCD. 3. Chn c/ ghi (R/W). u vo c/ ghi cho php ngi dng ghi thng tin ln LCD khi R/W = 0 hoc c thng tin t n khi R/W = 1. 4. Chn cho php E (Enable). Chn cho php E c s dng bi LCD cht thng tin hin hu trn chn d liu ca n. Khi d liu c cp n chn d liu th mt xung mc cao xung thp phi c p n chn ny LCD cht d liu trn cc chn d liu. Xung ny phi rng ti thiu l 450ns. 5. Chn D0 - D7. y l 8 chn d liu 8 bt, c dng gi thng tin ln LCD hoc c ni dung ca cc thanh ghi trong LCD. hin th cc ch ci v cc con s, chng ta gi cc m ASCII ca cc ch ci t A n Z, a n f v cc con s t 0 - 9 n cc chn ny khi bt RS = 1.

Smith Nguyen Studio.

Cng c cc m lnh m c th c gi n LCD xo mn hnh hoc a con tr v u dng hoc nhp nhy con tr. Bng 12.2 lit k cc m lnh. Chng ta cng s dng RS = 0 kim tra bt c bn xem LCD c sn sng nhn thng tin. C bn l D7 v c th cc khi R/W = 1 v RS = 0 nh sau: Nu R/W = 1, RS = 0 khi D7 = 1 (c bn 1) th LCD bn bi cc cng vic bn trong v s khng nhn bt k thng tin mi no. Khi D7 = 0 th LCD sn sng nhn thng tin mi. Lu chng ta nn kim tra c bn trc khi ghi bt k d liu no ln LCD. Bng 12.1: M t cc chn ca LCD. Chn 1 2 3 4 5 6 7 8 9 10 11 12 13 14 K hiu VSS VCC VEE RS R/W E DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 I/O I I I/O I/O I/O I/O I/O I/O I/O I/O I/O M t t Dng ngun 5v Cp ngun iu khin phn RS = 0 chn thanh ghi lnh. RS = 1 chn thanh d liu R/W = 1 c d liu. R/W = 0 ghi Cho php Cc bt d liu Cc bt d liu Cc bt d liu Cc bt d liu Cc bt d liu Cc bt d liu Cc bt d liu Cc bt d liu

Bng 12.2: Cc m lnh LCD. M (Hex) 1 2 4 6 5 7 8 A C E F 10 14 18 Lnh n thanh ghi ca LCD Xo mn hnh hin th Tr v u dng Gi con tr (dch con tr sang tri) Tng con tr (dch con tr sang phi) Dch hin th sang phi Dch hin th sang tri Tt con tr, tt hin th Tt hin th, bt con tr Bt hin th, tt con tr Bt hin th, nhp nhy con tr Tt con tr, nhp nhy con tr Dch v tr con tr sang tri Dch v tr con tr sang phi Dch ton b hin th sang tri

Smith Nguyen Studio.

1C 80 C0 38 Dch ton b hin th sang phi p con tr V u dng th nht p con tr V u dng th hai Hai dng v ma trn 5 7

Ghi ch: Bng ny c m rng t bng 12.4.

12 14 14 2 DMC1610A DMC1606C DMC16117 DMC16128 DMC16129 DMC1616433 DMC20434 14 DMC16106B 21 DMC16207 DMC16230 DMC20215 DMC32216 1 DMC20261 DMC24227 DMC24138 DMC32132 DMC32239 DMC40131 DMC40218 13

Hnh 12.1: Cc v tr chn ca cc LCD khc nhau ca Optrex. 12.1.3 Gi cc lnh v d liu n LCD vi mt tr. gi mt lnh bt k t bng 12.2 n LCD ta phi a chn RS v 0. i vi d liu th bt RS = 1 sau gi mt sn xung cao xung thp n chn E cho php cht d liu trong LCD. iu ny c ch ra trong on m chng trnh di y (xem hnh 12.2).

; gi thi gian tr trc khi gi d liu/ lnh k tip. ; chn P1.0 n P1.7 c ni ti chn d d liu D0 - D7 ca LCD. ; Chn P2.0 c ni ti chn RS ca LCD. ; Chn P2.1 c ni ti chn R/W ca LCD. ; Chn P2.2 c ni n chn E ca LCD. ORG MOV A, # 38H ; Khi to LCD hai dng vi ma trn 5 7 ACALL COMNWRT ; Gi chng trnh con lnh ACALL DELAY ; Cho LCD mt tr MOV A, # 0EH ; Hin th mn hnh v con tr ACALL COMNWRT ; Gi chng trnh con lnh ACALL DELAY ; Cp mt tr cho LCD MOV AM # 01 ; Xo LCD ACALL COMNWRT ; Gi chng trnh con lnh ACALL DELAY ; To tr cho LCD MOV A, # 06H ; Dch con tr sang phi ACALL COMNWRT ; Gi chng trnh con lnh ACALL DELAY ; To tr cho LCD MOV AM # 48H ; a con tr v dng 1 ct 4 ACALL COMNWRT ; Gi chng trnh con lnh

Smith Nguyen Studio.

ACALL MOV ACALL ACALL MOV ACALL SJMP MOV CLR CLR SETB CLR RET MOV SETB CLR SETB CLR RET MOV MOV DJNZ DJNZ RET END DELAY A, # N DATAWRT DELAY AM # 0 DATAWRT AGAIN P1, A P2.0 P2.1 P2.2 P2.2 P1, A P2.0 P2.1 P2.2 P2.2 R3, # 50 R4, # 255 R4, HERE R3, HERE2 ; To tr cho LCD ; Hin th ch N ; Gi chng trnh con hin thij DISPLAY ; To tr cho LCD ; Hin th ch 0 ; Gi DISPLAY ; Ch y ; Gi lnh n LCD ; Sao chp thanh ghi A n cng P1 ; t RS = 0 gi lnh ; t R/W = 0 ghi d liu ; t E = 1 cho xung cao ; t E = 0 cho xung cao xung thp ; Ghi d liu ra LCD ; Sao chp thanh ghi A n cng P1 ; t RS = 1 gi d liu ; t R/W = 0 ghi ; t E = 1 cho xung cao ; t E = 0 cho xung cao xung thp ; t tr 50ms hoc cao hn cho CPU nhanh ; t R4 = 255 ; i y cho n khi R4 = 0

AGAIN: COMNWRT:

DATAWRT:

DELAY: HERE2: HERE:

LCD 8051 D0 VCC VEE P1.0 P1.0 P2.1 P2.2 D7 V RS R/W E SS

+5v 10K POT

Hnh 12.2: Ni ghp LCD. 12.1.4 Gi m lnh hoc d liu n LCD c kim tra c bn. on chng trnh trn y ch ra cch gi cc lnh n LCD m khng c kim tra c bn (Busy Flag). Lu rng chng ta phi t mt tr ln trong qu tnh xut d liu hoc lnh ra LCD. Tuy nhin, mt cch tt hn nhiu l hin th c bn trc khi xut mt lnh hoc d liu ti LCD. Di y l mt chng trnh nh vy.

; Kim tra c bn trc khi gi d liu, lnh ra LCD ; t P1 l cng d liu

Smith Nguyen Studio.

; t P2.0 ni ti cng RS ; t P2.1 ni ti chn R/W ; t P2.2 ni ti chn E ORG MOV A, # 38H ACALL COMMAND MOV A, # 0EH ACALL COMMAND MOV A, # 01H ACALL COMMAND MOV A, # 86H ACALL COMMAND MOV A, # N ACALL DATA DISPLAY MOV A, # 0 ACALL DATA DISPLAY HERE: SJMP HERE COMMAND: ACALL READY MOV P1, A CLR P2.0 CLR P2.1 SETB P2.2 CLR P2.2 RET DATA-DISPLAY:: ACALL READY MOV P1, A SETB P2.0 CLR P2.1 SETB P2.2 CLR P2.2 RET DELAY: SETB P1.7 CLR P2.0 SETB P2.1 ; c thanh ghi lnh v kim tra c lnh BACK: CLR P2.2 SETB P2.2 JB P1.7, BACK RET END

; Khi to LCD hai dng vi ma trn 5 7 ; Xut lnh ; Dch con tr sang phi ; Xut lnh ; Xo lnh LCD ; Xut lnh ; Dch con tr sang phi ; a con tr v dng 1 lnh 6 ; Hin th ch N ; Hin th ch 0 ; Ch y ; LCD sn sng cha? ; Xut m lnh ; t RS = 0 cho xut lnh ; t R/W = 0 ghi d liu ti LCD ; t E = 1 i vi xung cao xung thp ; t E = 0 cht d liu ; LCD sn sng cha? ; Xut d liu ; t RS = 1 cho xut d liu ; t R/W = 0 ghi d liu ra LCD ; t E = 1 i vi xung cao xung thp ; t E = 0 cht d liu ; Ly P1.7 lm cng vo ; t RS = 0 truy cp thanh ghi lnh ; t R/W = 1 c thanh ghi lnh ; E = 1 i vi xung cao xung thp ; E = 0 cho xung cao xung thp? ; i y cho n khi c bn = 0

Lu rng trong chng trnh c bn D7 ca thanh ghi lnh. c thanh ghi lnh ta phi t RS = 0, R/W = 1 v xung cao - xung - thp cho bt E cp thanh ghi lnh cho chng ta. Sau khi c thanh ghi lnh, nu bt D7 (c bn) mc cao th LCD bn v khng c thng tin (lnh) no c xut n n ch khi no D7 = 0 mi c th gi d liu hoc lnh n LCD. Lu trong phng pht ny khng s dng tr thi gian no v ta ang kim tra c bn trc khi xut lnh hoc d liu ln LCD. 12.1.5 Bng d liu ca LCD. Trong LCD ta c th t d liu vo bt c ch no. di y l cc v tr a ch v cch chng c truy cp.

Smith Nguyen Studio.

RS 0 E/W 0 DB7 1 DB6 A DB5 A DB4 A DB3 A DB2 A DB1 A DB0 A

Khi AAAAAAA = 0000000 n 0100111 cho dng lnh 1 v AAAAAAA = 1100111 cho dng lnh2. Xem bng 12.3. Bng 12.3: nh a ch cho LCD. Dng 1 (min) Dng 1 (max) Dng 2 (min) Dng 2 (max) DB7 1 1 1 1 DB6 0 0 1 1 DB5 0 1 0 1 DB4 0 0 0 0 DB3 0 0 0 0 DB2 0 1 0 1 DB1 0 1 0 1 DB0 0 1 0 1

Di a ch cao c th l 0100111 cho LCD. 40 k t trong khi i vi CLD 20 k t ch n 010011 (19 thp phn = 10011 nh phn). rng di trn 0100111 (nh phn) = 39 thp phn ng vi v tr 0 n 39 cho LCD kch thc 40 2. T nhng iu ni trn y ta c th nhn c cc a ch ca v tr con tr c cc kch thc LCD khc nhau. Xem hnh 12.3 ch rng tt c mi a ch u dng s Hex. Hnh 12.4 cho mt biu ca vic phn thi gian ca LCD. Bng 12.4 l danh sch lit k chi tit cc lnh v ch lnh ca LCD. Bng 12.2 c m rng t bng ny.

16 2 LCD 20 1 LCD 20 2 LCD 20 4 LCD 80 C0 80 80 C0 80 C0 94 D4 80 C0 81 C0 81 81 C0 81 C0 95 D5 81 C0 82 C2 82 82 C2 82 C2 96 D6 82 C2 83 C3 83 83 C3 83 C3 97 D7 83 C3 84 C4 Through Through Through Through Through Through Through Through Through 85 C5 93 93 D3 93 D3 A7 E7 A7 E7 86 C6 Through Through 8F CF

20 2 LCD Note: All data is in hex.

Hnh 12.3: Cc a ch con tr i vi mt s LCD.

Smith Nguyen Studio.

Data

tDSW tAS tPWH

tH tAH

R/W

RS

tPwh = Enable pulse width = 450 ns (minimum) tDSW = Data set up time = 195 ns (minimum) tH = Data hold time 10 ns (minimum) tAS = Set up time prior to E (going high) for both RS and R/W = 140 ns (minimum) tAH = Hold time afterr E has come down for both RS and R/W = 10 ns (minimum)

Hnh 12.4: Phn khe thi gian ca LCD. Bng 12.4: Danh sch lit k cc lnh v a ch lnh ca LCD.

Lnh DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 R/W RS M t Thi gian thc hin

Xo 0 mn hnh Tr v 0 u dng t ch 0 truy nhp iu 0 khin Bt/tt hin th Dch 0 hin th v con tr t 0 chc nng

0 0 0

0 0 0

0 0 0

0 0 0

0 0 0

0 0 0

0 0 1

0 1 1/ D C

1 S

Xo ton b mn hnh v t a ch 0 ca DD RAM vo b m a ch t a ch 0 ca DD RAM nh b m a ch. Tr hin th dch v v tr gc DD RAM khng thay i t hng chuyn dch con tr v xc nh dch hin th cc thao tc ny c thc hin khi c v ghi d liu t Bt/ tt mn hnh (D) Bt/ tt con tr (C) v nhp nhy k t v tr con tr (B) Dch con tr v dch hin th m khng thay i DD RAM Thit lp di d liu (DL) s dng hin th (L) v phng k t (F)

1.64 ms 1.64 ms 40 ms

40 ms

S / C N

R / L F

40 ms

D L

40 ms

Smith Nguyen Studio.

t a ch CGRA M Thit lp a ch DD RAM C bn c v a ch Ghi d liu CG hoc DD RAM c d liu CG hoc DD RAM 0 0 0 1 AGC Thit lp a ch C6 RAM d liu CG RAM c gi i v nhn sau thit lp ny Thit lp a ch DD RAM d liu DD RAM c gi v nhn sau thit lp ny C bn c (BF) bo hot ng bn trong ang c thc hin v c ni dung b m a ch Ghi d liu vo DD RAM hoc CG RAM 40 ms

ADD

40 ms

0 1

1 0

BF

ADD Ghi d liu

40 ms 40 ms

c d liu

c d liu t DD RAM hoc CG RAM

40 ms

Ghi ch: 1. Thi gian thc l thi gian cc i khi tn s fCP hoc fosc l 250KHz 2. Thi gian thc thay i khi tn s thay i. Khi tn s fEP hay fosc L 270kHz th thi gian thc hin c tnh 250/270 40 = 35ms v.v 3. Cc k hiu vit tt trong bng l: 4.

DD RAM CG RAM ACC ADD AC RAM. 1/D = 1 S=1 S/C = 1 R/L = 1 DL = 1 N=1 F=1 BF = 1

RAM d liu hin th (Display Data RAM) RAM my pht k t (character Generator) a cha ca RAM my pht k t a ch ca RAM d liu hin th ph hp vi a ch con tr. B m a ch (Address Counter) c dng cho cc a ch DD RAM v CG Tng Km dch hin th Dch hin th Dch sang phi 8 bt 2 dng Ma trn im 5 10 Bn 1/D = 0 S/C = 0 R/L = 0 DL = 0 N=1 F=0 BF = 0 Gim Dch con tr Dch tri 4 bt 1 dng Ma trn im 5 7 C th nhn lnh

12.2 Phi ghp 8051 vi ADC v cc cm bin. Phn ny s khm ph ghp cc chp ADC (b chuyn i tng t s) v cc cm bin nhit vi 8051. 12.1.1 Cc thit b ADC. Cc b chuyn i ADC thuc trong nhng thit b c s dng rng ri nht thu d liu. Cc my tnh s s dng cc gi tr nh phn, nhng trong th gii vt l th mi i lng dng tng t (lin tc). Nhit , p sut (kh hoc

Smith Nguyen Studio.

cht lng), m v vn tc v mt s t trng nhng i lng vt l ca th gii thc m ta gp hng ngy. Mt i lng vt l c chuyn v dng in hoc in p qua mt thit b c gi l cc b bin i. Cc b bin i cng c th c coi nh cc b cm bin. Mc d ch c cc b cm bin nhit, tc , p sut, nh sng v nhiu i lng t nhin khc nhng chng u cho ra cc tn hiu dng dng in hoc in p dng lin tc. Do vy, ta cn mt b chuyn i tng t s sao cho b vi iu khin c th c c chng. Mt chp ADC c s dng rng ri l ADC 804. 12.2.2 Chp ADC 804. Chp ADC 804 l b chuyn i tng t s trong h cc lot ADC 800 t hng National Semiconductor. N cng c nhiu hng khc sn xut, n lm vic vi +5v v c phn gii l 8 bt. Ngoi phn gii th thi gian chuyn i cng l mt yu t quan trng khc khi nh gi mt b ADC. Thi gian chuyn i c nh ngha nh l thi gian m b ADC cn chuyn mt u vo tng t thnh mt s nh phn. Trong ADC 804 thi gian chuyn i thay i ph thuc vo tn s ng h c cp ti chn CLK v CLK IN nhng khng th nhanh hn 110ms. Cc chn ca ADC 804 c m t nh sau: 1. Chn CS - chn chp: L mt u vo tch cc mc thp c s dng kch hot chp ADC 804. truy cp ADC 804 th chn ny phi mc thp. 2. Chn RD (c): y l mt tn hiu u vo c tch cc mc thp. Cc b ADC chuyn i u vo tng t thnh s nh phn tng ng vi n v gi n trong mt thanh ghi trong. RD c s dng nhn d liu c chuyn i u ra ca ADC 804. Khi CS = 0 nu mt xung cao - xung - thp c p n chn RD th u ra s 8 bt c hin din cc chn d liu D0 - D7. Chn RD cng c coi nh cho php u ra. 3. Chn ghi WR (thc ra tn chnh xc l Bt u chuyn i). y l chn u vo tch cc mc thp c dng bo cho ADC 804 bt u qu trnh chuyn i. Nu CS = 0 khi WR to ra xung cao - xung - thp th b ADC 804 bt u chuyn i gi tr u vo tng t Vin v s nh phn 8 bt. Lng thi gian cn thit chuyn i thay i ph thuc vo tn s a n chn CLK IN v CLK R. Khi vic chuyn i d liu c hon tt th chn INTR c p xung thp bi ADC 804. 4. Chn CLK IN v CLK R. Chn CLK IN l mt chn u vo c ni ti mt ngun ng h ngoi khi ng h ngoi c s dng to ra thi gian. Tuy nhin 804 cng c mt my to xung ng h. s dng my to xung ng h trong (cng cn c gi l my to ng h ring) ca 804 th cc chn CLK IN v CLK R c ni ti mt t in v mt in tr nh ch ra trn hnh 12.5. Trong trng hp ny tn s ng h c xc nh bng biu thc:

f= 1 1,1RC

gi tr tiu biu ca cc i lng trn l R = 10kW v C= 150pF v tn s nhn c l f = 606kHz v thi gian chuyn i s mt l 110ms.

Smith Nguyen Studio.

ADC0804 +5V 10k

POT

1 1 1 9 19

20 Vin(+) Vin(-) A GND Vref/2 CLK R CLK in CS RD D GND Vcc D0 D1 D2 D3 D4 D5 D6 D7 WR INTR 18 17 16 15 14 13 12 11 3 5

to

LEDs

10k

150pF

4 1 2 10

Nomally

Open START

Hnh 12.5: Kim tra ADC 804 ch chy t do. 5. Chn ngt INTR (ngt hay gi chnh xc hn l kt thc chuyn i). y l chn u ra tch cc mc thp. Bnh thng n trng thi cao v khi vic chuyn i hon tt th n xung thp bo cho CPU bit l d liu c chuyn i sn sng ly i. Sau khi INTR xung thp, ta t CS = 0 v gi mt xung cao 0 xung - thp ti chn RD ly d liu ra ca 804. 6. Chn Vin (+) v Vin (-). y l cc u vo tng t vi sai m Vin = Vin (+) - Vin (-). Thng thng Vin (-) c ni xung t v Vin (+) c dng nh u vo tng t c chuyn i v dng s. 7. Chn VCC. y l chn ngun nui +5v, n cng c dng nh in p tham chiu khi u vo Vref/2 (chn 9) h. 8. Chn Vref/2. Chn 9 l mt in p u vo c dng cho in p tham chiu. Nu chn ny h (khng c ni) th in p u vo tng t cho ADC 804 nm trong di 0 n +5v (ging nh chn VCC). Tuy nhin, c nhiu ng dng m u vo tng t p n Vin cn phi khc ngoi di 0 n 5v. Chn Vref/2 cdng thc thi cc in p u vo khc ngoi di 0 - 5v. V d, nu di u vo tng t cn phi l 0 n 4v th Vref/2 c ni vi +2v. Bng 12.5 biu din di in p Vin i vi cc u vo Vref/2 khc nhau. Bng 12.5: in p Vref/2 lin h vi di Vin.

Smith Nguyen Studio.

Vref/ 2(V) H * 2.0 1.5 1.28 1.0 0.5 Vin(V) 0 n 5 0 n 4 0 n 3 0 n 2.56 0 n 2 0 n 1 Step Size (mV) 5/256 = 19.53 4/255 = 15.62 3/256 = 11.71 2.56/256 = 10 2/256 = 7.81 1/256 = 3.90

Ghi ch: - VCC = 5V - * Khi Vref/2 h th o c khong 2,5V - Kch thc bc ( phn di) l s thay i nh nht m ADC c th phn bit c. 9. Cc chn d liu D0 - D7. Cc chn d liu D0 - D7 (D7 l bt cao nht MSB v D0 l bt thp nht LSB) l cc chn u ra d liu s. y l nhng chn c m ba trng thi v d liu c chuyn i ch c truy cp khi chn CS = 0 v chn RD b a xung thp. tnh in p u ra ta c th s dng cng thc sau:

D out = V in kich thuoc buoc

Vi Dout l u ra d liu s (dng thp phn). Vin l in p u vo tng t v phn di l s thay i nh nht c tnh nh l (2 Vref/2) chia cho 256 i vi ADC 8 bt. 10. Chn t tng t v chn t s. y l nhng chn u vo cp t chung cho c tn hiu s v tng t. t tng t c ni ti t ca chn Vin tng t, cn t s c ni ti t ca chn Vcc. L do m ta phi c hai t l cch ly tn hiu tng t Vin t cc in p k sinh to ra vic chuyn mch s c chnh xc. Trong phn trnh by ca chng ta th cc chn ny c ni chung vi mt t. Tuy nhin, trong thc t thu o d liu cc chn t ny c ni tch bit. T nhng iu trn ta kt lun rng cc bc cn phi thc hin khi chuyn i d liu bi ADC 804 l: a) Bt CS = 0 v gi mt xung thp ln cao ti chn WR bt u chuyn i. b) Duy tr hin th chn INTR . Nu INTR xung thp th vic chuyn i c hon tt v ta c th sang bc k tip. Nu INTR cao tip tc thm d cho n khi n xung thp. c) Sau khi chn INTR xung thp, ta bt CS = 0 v gi mt xung cao - xung - thp n chn RD ly d liu ra khi chp ADC 804. Phn chia thi gian cho qu trnh ny c trnh by trn hnh 12.6.

Smith Nguyen Studio.

CS

WR

D0 D7 Data out

INTR RD

Start conversion End conversion

Read it

Hnh 12.6: Phn chia thi gian c v ghi ca ADC 804. 12.2.3 Kim tra ADC 804. Chng ta c th kim tra ADC 804 bng cch s dng s mch trn hnh 12.7. thit lp ny c gi l ch kim tra chy t do v c nh sn xut khuyn cao nn s dng. Hnh 12.5 trnh by mt bin tr c dng cp mt in p tng t t 0 n 5V ti chn u vo. Vin(+) ca ADC 804 cc u ra nh phn c hin th trn cc n LED ca bng hun luyn s. Cn phi lu rng trong ch kim tra chy t do th u vo CS c ni ti t v u vo WR c ni ti u ra INTR . Tuy nhin, theo ti liu ca hng National Semiconductor nt WR v INTR phi c tm thi a xung thp k sau chu trnh cp ngun bo m hot ng.

8051 P2.5 P2.6 P1.0 ADC804 5V

10k

RD WR

D0

VCC CLK R CLK IN Vin(+) Vin(-) A GND Vref/2 GND

150pF 10k POT

P1.7 P2.7

D7 INTR

CS

Hnh 12.7: Ni ghp ADC 804 vi ngun ng h ring.

Smith Nguyen Studio.

V d 12.7: Hy th ni ghp ADC 804 vi 8051 theo s 12.7. Vit mt chng trnh hin th chn INTR v ly u vo tng t vo thanh ghi A. Sau gi mt chng trnh chuyn i m Hex ra ASCII v mt chng trnh hin th d liu. Thc hin iu ny lin tc. Li gii:

; t P2.6 = WR (bt u chuyn i cn 1 xung thp ln cao) ; t chn P2.7 = 0 khi kt thc chuyn i ; t P2.5 = RD (xung cao - xung - thp s c d liu t ADC) ; P1.0 P1.7 ca ADC 804 MOV P1, # 0FFH ; Chn P1 l cng u vo BACK: CLR P2.6 ; t WR = 0 SETB P2.6 ; t WR = 1 bt u chuyn i HERE: JB P2.7, HERE ; Ch cho P2.7 to kt thc chuyn i CLR P2.5 ; Kt thc chuyn i, cho php c RD MOV A, P1 ; c d liu vo thanh ghi A ACALL CONVERSION ; Chuyn i s Hex ra m ASCII ACALL DATA-DISPLAY ; Hin th d liu SETB P2.5 ; a RD = 1 cho ln c sau. SJMP BACK 8051 P2.5 P2.6 P1.0 ADC804 5V

RD WR

D0

VCC CLK R CLK IN Vin(+) Vin(-) A GND Vref/2 GND

10k POT

Q

P1.7 P2.7 D0 INTR

CS

Q

74LS74

Hnh 12.8: Ni ghp ADC 804 vi ng h t XTAL2 ca 8051. Trn hnh 12.8 ta c th thy rng tn hiu ng h i vo ADC 804 l t tn s thch anh ca 8051. V tn s ny qu cao nn ta s dng hai mch lt Rlip - Flop kiu D (74LS74) chia tn s ny cho 4. Mt mch lt chia tn s cho 2 nu ta ni u Q ti u vo D. i vi tn s cao hn th ta cn s dng nhiu mch Flip Plop hn. 12.2.4 Phi ghp vi mt cm bin nhit ca 8051.

Smith Nguyen Studio.

Cc b bin i (Transducer) chuyn i cc i lng vt l v d nh nhit , cng nh sng, lu tc v tc thnh cc tn hiu in ph thuc vo b bin i m u ra c th l tn hiu dng in p, dng, tr khng hay dung khng. V d, nhit c bin i thnh v cc tn hiu in s dng mt b bin i gi l Rhermistor (b cm bin nhit), mt b cm bin nhit p ng s thay i nhit bng cch thay i tr khng nhng p ng ca n khng tuyn tnh (xem bng 12.6). Bng 12.6: Tr khng ca b cm bin nhit theo nhit . Nhit (0C) 0 25 50 75 100 Tr khng ca cm bin (kW) 29.490 10.000 3.893 1.700 0.817

Bng 12.7: Hng dn chn lot cc cm bin h LM34. M k hiu LM34A LM34 LM34CA LM34C LM34D Di nhit -55 F to + 300 C -55 F to + 300 C -40 F to + 230 C -40 F to + 230 C -32 F to + 212 C chnh xc + 2.0 F + 3.0 F + 2.0 F + 3.0 F + 4.0 F u ra 10mV/F 10mV/F 10mV/F 10mV/F 10mV/F

Bng 12.8: Hng dn chn lot cc cm bin nhit h LM35. M sn phm LM35A LM35 LM35CA LM35C LM35D Di nhit -55 C to + 150 C -55 C to + 150 C -40 C to + 110 C -40 C to + 110 C 0 C to + 100 C chnh xc + 1.0 C + 1.5 C + 1.0 C + 1.5 C + 2.0 C u ra 10 mV/F 10 mV/F 10 mV/F 10 mV/F 10 mV/F

Tnh cht gn lin vi vic vit phn mm cho cc thit b phi tuyn nh vy a nhiu nh sn xut tung ra th trng cc lot b cm bin nhit tuyn tnh. Cc b cm bin nhit n gin v c s dng rng ri bao gm cc lot h LM34 v LM35 ca hng National Semiconductor Corp. 12.2.5 Cc b cm bin nhit h LM34 v LM35. Lot cc b cm bin LM34 l cc b cm bin nhit mch tch hp chnh xc cao m in p u ra ca n t l tuyn tnh v nhit Fahrenheit (xem hnh 12.7). lot LM34 khng yu cu cn chnh bn ngoi v vn n c cn chnh ri. N a ra in p 10mV cho s thay i nhit 10F. bng 12.7 hng dn ta chn cc cm bin lot LM34.

Smith Nguyen Studio.

Lot cc b cm bin LM35 cng l cc b cm bin nhit mch tch hp chnh xc cao m in p u ra ca n t l tuyn tnh vi nhit theo thang Celsius. Chng cng khng yu cu cn chnh ngoi v vn chng c cn chnh. Chng a ra in p 10Mv cho mi s thay i 10C. Bng 12.8 hng dn ta chn cc cm bin h LM35. 12.2.6 Phi hp tn hiu v phi ghp LM35 vi 8051. Phi hp tn hiu l mt thut ng c s dng rng ri trong lnh vc thu o d liu. Hu ht cc b bin i u a ra cc tn hiu in dng in p, dng in, dung khng hoc tr khng. Tuy nhin, chng ta cn chuyn i cc tn hiu ny v in p nhm gi u vo n b chuyn i ADC. S chuyn i (bin i) ny c gi chung l phi hp tn hiu. Phi hp tn hiu c th l vic chuyn i dng in thnh in p hoc s khuych i tn hiu. V d, b cm bin nhit thay i tr khng vi nhit . S thay i tr khng phi c chuyn thnh in p c th c s dng cho cc ADC. Xt trng hp ni mt LM35 ti mt ADC 804 v ADC 804 c phn di 8 bt vi ti a 256 bc (28) v LM35 (hoc ML34) to in p 10mV cho mi s thay i nhit 10C nn ta c th to iu kin Vin ca ADC 804 to ra mt Vout = 2560mV (2,56V) cho u ra u thang o. do vy, nhm to ra Vout y thang 2,56V cho ADC 804 ta cn t in p Vref/2 = 1,28V. iu ny lm cho Vout ca ADC 804 p ng trc tip vi nhit c hin th trn LM35 (xem bng 12.9). Cc gi tr ca Vref/2 c cho bng 12.5. Bng 12.9: Nhit . Nhit (0C) 0 1 2 3 10 30 Vin (mV) 0 10 20 30 100 300 Vout (D7 D0) 0000 0000 0000 0001 0000 0010 0000 0011 0000 1010 0001 1110

Cc i lng vt l (nhit , p sut, lu tc v.v) B bin i Phi hp tn hiu ADC B vi iu khin

Smith Nguyen Studio.

Hnh 12.9: Thu o cc i lng vt l.

8051 P2.5 P2.6 P1.0 ADC804 5V LM35 or LM34

RD WR

D0

VCC CLK R CLK IN Vin(+) Vin(-) A GND Vref/2 GND

GND

2.5k

Q

P1.7 P2.7 D7 INTR

LM336

CS

Set to 1.28V

10k

Hnh 12.10 Hnh 12.10: Ni ghp 8051 vi DAC 804 v cm bin nhit . Hnh 12.10 biu din ni ghp ca b cm bin nhit n ADC 804. Lu rng ta s dng i t zener LM336 - 2.5 c nh in p qua bin tr 10kW ti 2,5V. Vic s dng LM336 - 2.5 c th vt qua c mi dao ng ln xung ca ngun nui. 12.2.7 Chp ADC 808/809 vi 8 knh tng t. Mt chp hu ch khc ca National Semiconductor l ADC 808/809 (xem hnh 12.11). Trong khi ADC 804 ch c mt u vo tng t th chp ny c 8 knh u vo. Nh vy n cho php ta hin th ln 8 b bin i khc nhau ch qua mt chp duy nht. Lu rng, ADC 808/809 c u ra d liu 8 bt nh ADC 804. 8 knh u vo tng t c dn knh v c chn theo bng 12.10 s dng ba chn a ch A, B v C.

IN0

GND

Clock

Vcc

D0

IN7

ADC808/809

Vref(+) EOC Vref(-) OE SC ALE A C C

D7

(LSB)

Smith Nguyen Studio.

Hnh 12.11: B bin i ADC 808/809. Bng 12.10: Chn knh tng t ca ADC 808. Chn knh tng t IN0 IN1 IN2 IN3 IN4 IN5 IN6 IN7 C 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 A 0 1 0 1 0 1 0 1

Trong ADC 808/809 th Vrer(+) v Vref(-) thit lp in p tham chiu. Nu Vref (-1) = Gnd v Vref (+) = 5V th phn di l 5V/256 = 19,53mV. Do vy, c phn di 10mV ta cn t Vref (+) = 2,56V v Vref (-) = Gnd. T hnh 12.11 ta thy c chn ALE. Ta s dng cc a ch A, B v C chn knh u vo IN0 IN7 v kch hot chn ALE cht a ch. Chn SetComplete bt u chuyn i (Start Conversion). Chn EOC c dng kt thc chuyn i (End - Of - Conversion) v chn OE l cho php c u ra (Out put Enable). 12.2.7 Cc bc lp trnh cho ADC 808/809. Cc bc chuyn d liu t u vo ca ADC 808/809 vo b vi iu khin nh sau: 1. Chn mt knh tng t bng cch to a ch A, B v C theo bng 12.10. 2. Kch hot chn ALE (cho php cht a ch Address Latch Enable). N cn xung thp ln cao cht a ch. 3. Kch hot chn SCbng xung cao xung thp bt u chuyn i. 4. Hin th OEC bo kt thc chuyn i. u ra cao - xung - thp bo rng d liu c chuyn i v cn phi c ly i. 5. Kch hot OE cho php c d liu ra ca ADC. Mt xung cao xung thp ti chn OE s em d liu s ra khi chp ADC. Lu rng trong ADC 808/809 khng c ng h ring v do vy phi cp xung ng b ngoi n chn CLK. Mc d tc chuyn i ph thuc vo tn s ng h c ni n CLK nhng n khng nhanh hn 100ms.

Вам также может понравиться

- Interface A 2x16 LCD With 8051 in 8-BitSMPДокумент18 страницInterface A 2x16 LCD With 8051 in 8-BitSMPSUNIL MP100% (2)

- Unit - 5 8051 Interfacing Andapplications Interfacing of 8051with: Analog Sensors, Keypad & LCD Display, ADC, DAC, DC Motor. LCD InterfacingДокумент31 страницаUnit - 5 8051 Interfacing Andapplications Interfacing of 8051with: Analog Sensors, Keypad & LCD Display, ADC, DAC, DC Motor. LCD InterfacingNusret YılmazОценок пока нет

- LCD Excersise 8051Документ4 страницыLCD Excersise 8051mshanmuganОценок пока нет

- LCD Interfacing PIC16F877aДокумент5 страницLCD Interfacing PIC16F877avipulkondekar100% (1)

- Interfacing of 16x2 LCD With 8051 MicrocontrollerДокумент7 страницInterfacing of 16x2 LCD With 8051 MicrocontrollerVinothkumar Uruman100% (1)

- Interfacing 16×2 LCD With 8051Документ39 страницInterfacing 16×2 LCD With 8051gunda manasaОценок пока нет

- HJ1602A DatasheetДокумент11 страницHJ1602A DatasheetsunthomaОценок пока нет

- LCD 16X2Документ5 страницLCD 16X2srivastavasid26Оценок пока нет

- TTT 8051 PPT1Документ25 страницTTT 8051 PPT1Shylu SamОценок пока нет

- 7segment Keypad EEPROMДокумент20 страниц7segment Keypad EEPROMgkkishorekumarОценок пока нет

- Graphic Display AGM-12864A-801Документ15 страницGraphic Display AGM-12864A-801Anonymous nMZN9dJvaZОценок пока нет

- LCD InterfacingДокумент4 страницыLCD InterfacingSavinda SenevirathneОценок пока нет

- LCD & KeyboardДокумент19 страницLCD & KeyboardAditya AgarwalОценок пока нет

- LAB-7: Interfacing Liquid Crystal Display (LCD) : ObjectivesДокумент6 страницLAB-7: Interfacing Liquid Crystal Display (LCD) : ObjectivesTahir NisarОценок пока нет

- LMC-SSC2E16-01 Serial: User ManualДокумент12 страницLMC-SSC2E16-01 Serial: User ManualFred ShihОценок пока нет

- Lab 4 - Interfacing To Keypad and LCD ObjectivesДокумент19 страницLab 4 - Interfacing To Keypad and LCD ObjectivesidkОценок пока нет

- LCD Interfacing:: PIN No Name FunctionДокумент6 страницLCD Interfacing:: PIN No Name FunctionPiyush chaudhariОценок пока нет

- LCD 4 Bit InterfacingДокумент6 страницLCD 4 Bit InterfacingYogesh Hardiya100% (1)

- Interfacing Graphical LCD With 8051: Submitted By: Rohan Dhakad Submitted To: Ambuj PanditДокумент24 страницыInterfacing Graphical LCD With 8051: Submitted By: Rohan Dhakad Submitted To: Ambuj PanditRohan DhakadОценок пока нет

- LCD Interface With AT89C2051Документ5 страницLCD Interface With AT89C2051sandipnair06Оценок пока нет

- MPMC-Unit-3 NotesДокумент46 страницMPMC-Unit-3 NotesBhure VedikaОценок пока нет

- Micrcontroller Based Electronic Voting MachineДокумент39 страницMicrcontroller Based Electronic Voting Machinegayush20Оценок пока нет

- Arduino - LiquidCrystalДокумент5 страницArduino - LiquidCrystalIonutm100% (1)

- Understanding LCDДокумент7 страницUnderstanding LCDOscar LyeОценок пока нет

- Interfacing 16×2 LCD With 8051Документ11 страницInterfacing 16×2 LCD With 8051Malia MendezОценок пока нет

- Lecture 07 Experiment-11Документ9 страницLecture 07 Experiment-11linn.pa.pa.khaing.2020.2021.fbОценок пока нет

- Bascom and AVR, Using An LCD.: Peter Ouwehand'sДокумент10 страницBascom and AVR, Using An LCD.: Peter Ouwehand'sAulia RahmayantiОценок пока нет

- Daewoo DPC-7200PDДокумент42 страницыDaewoo DPC-7200PDЕвгений СафоновОценок пока нет

- LCD Tutorial PDFДокумент46 страницLCD Tutorial PDFRoshan ShresthaОценок пока нет

- LCD Interfacing With 8051 DocumentationДокумент7 страницLCD Interfacing With 8051 DocumentationSrideviKumaresan100% (3)

- INTERFACING LCD WITH 8051 MIROCONTROLLER With CodeДокумент14 страницINTERFACING LCD WITH 8051 MIROCONTROLLER With CodeRajagiri CollegeОценок пока нет

- Display LCDДокумент4 страницыDisplay LCDwilliams missael100% (2)

- LCD TutorialДокумент8 страницLCD TutorialAnwerZaib KhanОценок пока нет

- 8051 Microcontroller Lab Manual Lab 07Документ5 страниц8051 Microcontroller Lab Manual Lab 07sidiqbal100% (1)

- LMB 162 AdcДокумент11 страницLMB 162 AdcMohamedSalahОценок пока нет

- Unit - Iii MPMC-1Документ79 страницUnit - Iii MPMC-1gunda manasa100% (1)

- Programming Pic Microcontrollers in Picbasic Pro - LCD Lesson 1 Cornerstone Electronics Technology and Robotics IiДокумент15 страницProgramming Pic Microcontrollers in Picbasic Pro - LCD Lesson 1 Cornerstone Electronics Technology and Robotics IiDomDoretoОценок пока нет

- Lab5 - 1 EngДокумент13 страницLab5 - 1 EngMai Huỳnh TháiОценок пока нет

- LCD Interfacing With MicrocontrollersДокумент21 страницаLCD Interfacing With Microcontrollerstrinhdieuhvktqs100% (2)

- L06 Embedded 22Документ16 страницL06 Embedded 22kingОценок пока нет

- LCD Keyboard Interfacing: Unit-VДокумент31 страницаLCD Keyboard Interfacing: Unit-VMadhuri Rudravelli100% (1)

- LCD12A64Документ9 страницLCD12A64henrickramalhoОценок пока нет

- 24c256 Interfacing With 8051 Assembly CodeДокумент4 страницы24c256 Interfacing With 8051 Assembly CodeTrần MạnhОценок пока нет

- Micropro Compilation ReinierДокумент16 страницMicropro Compilation ReinierKei DeeОценок пока нет

- Introduction To LCD ProgrammingДокумент8 страницIntroduction To LCD ProgrammingCesar RangelОценок пока нет

- G12864C LCD Module ManualДокумент13 страницG12864C LCD Module Manualsigit jokoОценок пока нет

- LCD Keyboard InterfaceДокумент29 страницLCD Keyboard InterfaceSuryah SGОценок пока нет

- Arduino Hello WorldДокумент6 страницArduino Hello WorldKimZhiMieОценок пока нет

- Lab Record: Name Register Number Slot Faculty NameДокумент6 страницLab Record: Name Register Number Slot Faculty NamePRIYA SINGH 17BEE0017Оценок пока нет

- LCD and Keyboard InterfacingДокумент21 страницаLCD and Keyboard InterfacingAmmar EhabОценок пока нет

- 8051 Interfacing With Display SevicesДокумент5 страниц8051 Interfacing With Display Sevicesramjee26100% (1)

- LCD Interfacing For Pic 18f452Документ20 страницLCD Interfacing For Pic 18f452Bhautik DaxiniОценок пока нет

- LCD (Liquid Crystal Display) InterfaceДокумент12 страницLCD (Liquid Crystal Display) Interfacezbhp zОценок пока нет

- Proton Compiler ManualДокумент10 страницProton Compiler ManualAlexis AldásОценок пока нет

- Hello WorlvvvvvdДокумент8 страницHello WorlvvvvvdbrodryuОценок пока нет

- 2x16 LCD and 4x4 Keypad Interfacing With 8051 in Assembly LanguageДокумент19 страниц2x16 LCD and 4x4 Keypad Interfacing With 8051 in Assembly LanguageAbraham Muñoz50% (2)

- 8051 Interfacing LCD With 8051: SearchДокумент11 страниц8051 Interfacing LCD With 8051: SearchArun PaiОценок пока нет

- Arduino Liquid Crystal Library LCD Interface: Materials NeededДокумент4 страницыArduino Liquid Crystal Library LCD Interface: Materials NeededanuprkОценок пока нет

- Etc Lmg-Ssc12a64Документ10 страницEtc Lmg-Ssc12a64Dubis EszterОценок пока нет

- In This Chapter: Networking Collection of The Windows Server 2003 Technical Reference (Or SeeДокумент9 страницIn This Chapter: Networking Collection of The Windows Server 2003 Technical Reference (Or SeeSmith Nguyen StudioОценок пока нет

- Workflow in Microsoft Dynamics® CRM 4.0 - 01 - Smith.N StudioДокумент30 страницWorkflow in Microsoft Dynamics® CRM 4.0 - 01 - Smith.N StudioSmith Nguyen StudioОценок пока нет

- Deploying Wins Smith.N StudioДокумент36 страницDeploying Wins Smith.N StudioSmith Nguyen StudioОценок пока нет

- 03-JoinDomain - Smith.N StudioДокумент8 страниц03-JoinDomain - Smith.N StudioSmith Nguyen StudioОценок пока нет

- Ccna Exp2 - Chapter01 - Smith.N StudioДокумент69 страницCcna Exp2 - Chapter01 - Smith.N StudioSmith Nguyen StudioОценок пока нет

- Enetwork Basic Configuration PT Practice Sba Smith.N StudioДокумент11 страницEnetwork Basic Configuration PT Practice Sba Smith.N StudioSmith Nguyen StudioОценок пока нет

- Chuong 09 - Bo Dem Va Dinh Thoi - Smith.N StudioДокумент18 страницChuong 09 - Bo Dem Va Dinh Thoi - Smith.N StudioSmith Nguyen StudioОценок пока нет

- Chuong 03 - Cac Lenh Nhay - Smith.N StudioДокумент12 страницChuong 03 - Cac Lenh Nhay - Smith.N StudioSmith Nguyen StudioОценок пока нет

- Chuong 07 - Lenh Lo-Gic - Smith.N StudioДокумент9 страницChuong 07 - Lenh Lo-Gic - Smith.N StudioSmith Nguyen StudioОценок пока нет

- Chuong 04 - Lap Trinh Cong Vao Ra - Smith.N StudioДокумент9 страницChuong 04 - Lap Trinh Cong Vao Ra - Smith.N StudioSmith Nguyen StudioОценок пока нет

- Vi Dieu Khien 8051 - Smith.N StudioДокумент193 страницыVi Dieu Khien 8051 - Smith.N StudioSmith Nguyen StudioОценок пока нет

- Chuong 06 - Lenh So Hoc Va Chuong Trinh - Smith.N StudioДокумент11 страницChuong 06 - Lenh So Hoc Va Chuong Trinh - Smith.N StudioSmith Nguyen StudioОценок пока нет

- Xay Dung Nhom Lam ViecДокумент39 страницXay Dung Nhom Lam ViecVan Tuan TranОценок пока нет

- Phat Trien Ky Nang Lanh DaoДокумент31 страницаPhat Trien Ky Nang Lanh DaoLoc PhanОценок пока нет

- Tutorial C and C++ - Smith.N StudioДокумент267 страницTutorial C and C++ - Smith.N StudioSmith Nguyen StudioОценок пока нет

- Hen Ban Tren Dinh Thanh CongДокумент105 страницHen Ban Tren Dinh Thanh CongNo LimitОценок пока нет

- Lap Trinh C++ - Smith.N StudioДокумент122 страницыLap Trinh C++ - Smith.N StudioSmith Nguyen StudioОценок пока нет

- 1400 Service Manual2Документ40 страниц1400 Service Manual2Gabriel Catanescu100% (1)

- Labstan 1Документ2 страницыLabstan 1Samuel WalshОценок пока нет

- Oem Functional Specifications For DVAS-2810 (810MB) 2.5-Inch Hard Disk Drive With SCSI Interface Rev. (1.0)Документ43 страницыOem Functional Specifications For DVAS-2810 (810MB) 2.5-Inch Hard Disk Drive With SCSI Interface Rev. (1.0)Farhad FarajyanОценок пока нет

- Aisladores 34.5 KV Marca Gamma PDFДокумент8 страницAisladores 34.5 KV Marca Gamma PDFRicardo MotiñoОценок пока нет

- Sample Opposition To Motion To Strike Portions of Complaint in United States District CourtДокумент2 страницыSample Opposition To Motion To Strike Portions of Complaint in United States District CourtStan Burman100% (1)

- Digital LiteracyДокумент19 страницDigital Literacynagasms100% (1)

- Cabling and Connection System PDFДокумент16 страницCabling and Connection System PDFLyndryl ProvidoОценок пока нет

- Social Media Marketing Advice To Get You StartedmhogmДокумент2 страницыSocial Media Marketing Advice To Get You StartedmhogmSanchezCowan8Оценок пока нет

- Electricity 10thДокумент45 страницElectricity 10thSuryank sharmaОценок пока нет

- 1 PBДокумент14 страниц1 PBSaepul HayatОценок пока нет

- GL 186400 Case DigestДокумент2 страницыGL 186400 Case DigestRuss TuazonОценок пока нет

- Health Insurance in Switzerland ETHДокумент57 страницHealth Insurance in Switzerland ETHguzman87Оценок пока нет

- Star Link SafetyДокумент2 страницыStar Link SafetyJeronimo FernandezОценок пока нет

- Lockbox Br100 v1.22Документ36 страницLockbox Br100 v1.22Manoj BhogaleОценок пока нет

- Manufacturing StrategyДокумент31 страницаManufacturing Strategyrajendra1pansare0% (1)

- Fedex Service Guide: Everything You Need To Know Is OnlineДокумент152 страницыFedex Service Guide: Everything You Need To Know Is OnlineAlex RuizОценок пока нет

- Exp. 5 - Terminal Characteristis and Parallel Operation of Single Phase Transformers.Документ7 страницExp. 5 - Terminal Characteristis and Parallel Operation of Single Phase Transformers.AbhishEk SinghОценок пока нет

- EnerconДокумент7 страницEnerconAlex MarquezОценок пока нет

- Edita's Opertionalization StrategyДокумент13 страницEdita's Opertionalization StrategyMaryОценок пока нет

- An RambTel Monopole Presentation 280111Документ29 страницAn RambTel Monopole Presentation 280111Timmy SurarsoОценок пока нет

- BMA Recital Hall Booking FormДокумент2 страницыBMA Recital Hall Booking FormPaul Michael BakerОценок пока нет

- Use of EnglishДокумент4 страницыUse of EnglishBelén SalituriОценок пока нет

- Cancellation of Deed of Conditional SalДокумент5 страницCancellation of Deed of Conditional SalJohn RositoОценок пока нет

- RevisionHistory APFIFF33 To V219Документ12 страницRevisionHistory APFIFF33 To V219younesОценок пока нет

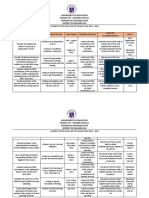

- Action Plan Lis 2021-2022Документ3 страницыAction Plan Lis 2021-2022Vervie BingalogОценок пока нет

- Brand Positioning of PepsiCoДокумент9 страницBrand Positioning of PepsiCoAbhishek DhawanОценок пока нет

- Datasheet Qsfp28 PAMДокумент43 страницыDatasheet Qsfp28 PAMJonny TОценок пока нет

- Schmidt Family Sales Flyer English HighДокумент6 страницSchmidt Family Sales Flyer English HighmdeenkОценок пока нет

- Interoperability Standards For Voip Atm Components: Volume 4: RecordingДокумент75 страницInteroperability Standards For Voip Atm Components: Volume 4: RecordingjuananpspОценок пока нет

- CANELA Learning Activity - NSPE Code of EthicsДокумент4 страницыCANELA Learning Activity - NSPE Code of EthicsChristian CanelaОценок пока нет