Академический Документы

Профессиональный Документы

Культура Документы

Illinois Exam2 Practice Solfa08

Загружено:

bittronicИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Illinois Exam2 Practice Solfa08

Загружено:

bittronicАвторское право:

Доступные форматы

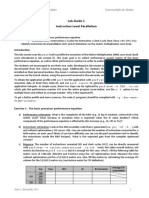

Question 1: Single-cycle CPU implementation (40 points) On the last page of the exam is a single-cycle datapath for a machine

very different than the one we saw in lecture. It supports the following (complex) instructions: lw_add addi_st sll_add rd, (rs), rt (rs), rs, imm rd, rs, rt, imm # rd = Memory[R[rs]] + R[rt]; # Memory[R[rs]] = R[rs] + imm; # rd = (R[rs] << imm) + R[rt];

All instructions use the same format (shown below), but not all instructions use all of the fields. Field Bits op 31-26 rs 25-21 rt 20-16 rd 15-11 imm 10-0

Part (a) For each of the above instructions, specify how the control signals should be set for correct operation. Use X for dont care. ALUOp can be ADD, SUB, SLL, PASS_A, or PASS_B (e.g., PASS_A means pass through the top operand without change). Full points will only be awarded for the fastest implementation. (20 points)

inst lw_add addi_st sll_add ALUsrc1 X 1 1 ALUsrc2 1 0 1 ALUsrc3 0 X 1 ALUop1 X ADD SLL ALUop2 ADD X ADD MemRead 1 0 0/X MemWrite 0 1 0 RegWrite 1 0 1

Part (b) Given the functional unit latencies as shown to the right, compute the minimum time to perform each type of instruction. Explain. (15 points)

Func. Unit Memory ALU Register File

Latency 3 ns 4 ns 2 ns

inst lw_add addi_st sll_add

Minimum time 14ns 12ns 15ns

Explain IMEM (3ns) + RF_read (2ns) + DMEM (3ns) + ALU (4ns) + RF_write (2ns) IMEM (3ns) + RF_read (2ns) + ALU (4ns) + DMEM (3ns) IMEM (3ns) + RF_read (2ns) + ALU (4ns) + ALU (4ns) + RF_write (2ns)

Part (c) What is the CPI and cycle time for this processor? (5 points) Since the processor is a single-cycle implementation, the CPI is 1. The cycle time is set by the slowest instruction, which in this case is the sll_add, yielding a clock period of 15ns. 1

Question: Pipelining (45 points) Part (a) Give a non-computing example of pipelining not involving laundry. (5 points) Bucket brigages, Subway sandwich assembly, airport security, fast-food restaurant drive throughs.

Part (b) Assume you have 10 items to process. If you can pipeline the processing into 5 steps (perfectly balancing the pipeline stages), how much faster does pipelining enable you to complete the process? You can leave your answer as an expression. (10 points) In the syncle-cycle datapath, every instruction executes in 1 cycle, and since we have 10 instructions, it takes a total of 10 cycles. In the pipeline machine it takes 4 steps to fill the pipeline and then one item is completed each cycle thereafter. Thus, it takes a total 14 cycles. In addition, the cycle time should be 1/5th as long. Speedup = (old exec time)/(new exec time) =( 10 * 1) / (14 * 1/5) = 3.57 .

Question, continued Consider the following MIPS code: loop: sub add addi lw add sw bgt $t3, $t0, $t1, $t2, $t2, $t2, $t3, $t3, $t0, $t0, 0($t0) $t2, 0($t1) $zero, loop 1 $t0 $t0 5

Part (c) Label all dependences within one iteration of this code (not just the ones that will require forwarding). One iteration is defined as the instructions between the sub and bgt inclusive. (10 points) Part (d) The above code produces the pipeline diagram shown below when run on a 5-stage MIPS pipeline with stages IF (fetch), ID (decode), EX (execute), MEM (memory) and WB (write-back). Note: stalls are indicated by , and registers can be read in the same cycle in which they are written.

Inst

sub

add

addi

lw

add

sw

bgt

sub

iter

N

N

N

N

N

N

N

N+1

1

IF

2

ID

IF

3

EX

ID

IF

4

MEM

EX

ID

IF

5

WB

MEM

-

-

WB

EX

ID

IF

MEM

EX

ID

IF

WB

MEM

-

-

-

WB

EX

ID

IF

MEM

EX

ID

-

WB

MEM

EX

-

WB

MEM

IF

WB

ID

EX

MEM

WB

6

7

8

9

10

11

12

13

14

15

16

17

For each of the following questions, justify your answer or explain why it cannot be answered using the given information. Note: full credit requires explanations. (20 points) Is forwarding from EX/MEM to the EX stage implemented? Explain. No, because the addi instruction is stalled. Is forwarding from MEM/WB to the EX stage implemented? Explain. Yes, because the addi is stalled only one cycle and the add following the lw is stalled only one cycle. Note: The branch target is computed in the ID stage. In which stage are branches resolved? Explain. Branches are resolved in the EX stage, because the second sub is fetched the cycle after the branch is in EX. The branch target is computed in the ID stage. What is the branch prediction scheme? Explain. If the diagram shows all of the instructions fetched, then a no-prediction policy is used. Cant be predict not-taken because those instructions arent shown. Cant be predict taken because the sub would be 3 fetched in cycle 11.

Question 3: Concepts (25 points) Write a short answer to the following questions. sentences. For full credit, answers should not be longer than two

Part a) A program is known to have a serial component that takes S seconds to execute, but the rest of the computation is arbitrarily parallelizable. If the program runs in T seconds using P processors, how long would it take to run using X processors? Assume T > S and P > 1. (10 points) This is just an application of Amdahls law. The parallelizable portion (T-S) of the program was sped up by a factor of P. Thus, the serial time is: S + (T-S)*P When running on X processors, we divide the parallelizable portion by X or: S + (T-S)*P/X

Part b) In what circumstances is throughput the desired performance metric and in what circumstances is latency the desired metric? (5 points) Latency is desired when we are concerned about one thing. Throughput is desired when we care about the rate at which things are processed.

Part c) Which of the three factorsof CPU time can a compiler inuence? Provide examples. (5 points) -The compiler can affect the number of instructions a program executes (e.g., by allocating a variable to a register it can avoid load and store instructions to access that variable). - The compiler can affect the CPI by selecting easier instructions (e.g., implementing a division by 2 as a right shift by 1 instead of using the integer division instruction) - Typically a compiler has no direct influence on a processors clock frequency.

Вам также может понравиться

- Designing An Electrical Installation - Beginner GuideДокумент151 страницаDesigning An Electrical Installation - Beginner GuideFrankie Wildel100% (4)

- Programming with MATLAB: Taken From the Book "MATLAB for Beginners: A Gentle Approach"От EverandProgramming with MATLAB: Taken From the Book "MATLAB for Beginners: A Gentle Approach"Рейтинг: 4.5 из 5 звезд4.5/5 (3)

- WWII Engineer Amphibian TroopsДокумент162 страницыWWII Engineer Amphibian TroopsCAP History Library67% (3)

- ch09 Morris ManoДокумент15 страницch09 Morris ManoYogita Negi RawatОценок пока нет

- Projects With Microcontrollers And PICCОт EverandProjects With Microcontrollers And PICCРейтинг: 5 из 5 звезд5/5 (1)

- Walsh Functions and SequencesДокумент3 страницыWalsh Functions and SequencesbittronicОценок пока нет

- Windows Memory BasicsДокумент5 страницWindows Memory BasicsGrant WillcoxОценок пока нет

- Data Science Machine LearningДокумент15 страницData Science Machine LearningmagrinraphaelОценок пока нет

- Managerial Accounting and Cost ConceptsДокумент67 страницManagerial Accounting and Cost ConceptsTristan AdrianОценок пока нет

- Introduction To MIPS ArchitectureДокумент10 страницIntroduction To MIPS ArchitectureJahanzaib AwanОценок пока нет

- Kinetics of Acetone Hydrogenation For Synthesis of Isopropyl Alcohol Over Cu-Al Mixed Oxide CatalystsДокумент9 страницKinetics of Acetone Hydrogenation For Synthesis of Isopropyl Alcohol Over Cu-Al Mixed Oxide Catalysts李国俊Оценок пока нет

- Unit - 2 Central Processing Unit TOPIC 1: General Register OrganizationДокумент13 страницUnit - 2 Central Processing Unit TOPIC 1: General Register OrganizationRam Prasad GudiwadaОценок пока нет

- Dau Terminal AnalysisДокумент49 страницDau Terminal AnalysisMila Zulueta100% (2)

- CS433 hw1 Fall 07Документ3 страницыCS433 hw1 Fall 0798140207Оценок пока нет

- M116C 1 EE116C-Midterm2-w15 SolutionДокумент8 страницM116C 1 EE116C-Midterm2-w15 Solutiontinhtrilac100% (1)

- Your Name:: Final ExamДокумент9 страницYour Name:: Final ExamDaniel EcheverriaОценок пока нет

- Midtermarch 2Документ9 страницMidtermarch 2Ghina BaassiriОценок пока нет

- Pipelining Instruction Execution and Cache Memory PoliciesДокумент10 страницPipelining Instruction Execution and Cache Memory PoliciesDinesh DevaracondaОценок пока нет

- cs146 Fall2017 Midterm1xxДокумент12 страницcs146 Fall2017 Midterm1xxgrizzyleoОценок пока нет

- HW 05Документ6 страницHW 05samadОценок пока нет

- Instructions: Csce 212: Final Exam Spring 2009Документ5 страницInstructions: Csce 212: Final Exam Spring 2009NapsterОценок пока нет

- Homework 2Документ8 страницHomework 2Deepak BegrajkaОценок пока нет

- Cse3666 MT1S F12Документ5 страницCse3666 MT1S F12dimpal_3221Оценок пока нет

- Zoom/Online Final - question Q1TITLE: Online Final Q1 PipeliningДокумент3 страницыZoom/Online Final - question Q1TITLE: Online Final Q1 PipeliningMuhammad Zahid iqbalОценок пока нет

- CCET ECE CS6303 16 MARKS QUESTION BANKДокумент16 страницCCET ECE CS6303 16 MARKS QUESTION BANKsakthivijayan80Оценок пока нет

- Indian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Документ4 страницыIndian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Utkarsh PatelОценок пока нет

- Assignment 2 SolutionДокумент4 страницыAssignment 2 SolutionAaliya Ali Abdul0% (1)

- Instruction-Level Parallelism and Its Exploitation: Sources: H&P Appendix C H&P Chapter 3 Previous CS 5375 MaterialДокумент104 страницыInstruction-Level Parallelism and Its Exploitation: Sources: H&P Appendix C H&P Chapter 3 Previous CS 5375 Materialharry.cheersОценок пока нет

- Computer Arch TestДокумент8 страницComputer Arch TestCricket Live StreamingОценок пока нет

- ECE 452: Computer Organization and DesignДокумент9 страницECE 452: Computer Organization and Designdermeister1988Оценок пока нет

- Week 2Документ22 страницыWeek 2Shubhadeep GhatakОценок пока нет

- Pipeliningmips PDFДокумент9 страницPipeliningmips PDFdoomachaleyОценок пока нет

- CPU Organization Bindu AgarwallaДокумент22 страницыCPU Organization Bindu AgarwallaNobodyОценок пока нет

- Exp - 08 Flight86Документ6 страницExp - 08 Flight86Muhammad SaqibОценок пока нет

- PracticeAssignment5 Sol 15573 PDFДокумент8 страницPracticeAssignment5 Sol 15573 PDFMohamedОценок пока нет

- Pipelined MIPS: Why pipelining improves performance and the challenges of implementing pipeliningДокумент12 страницPipelined MIPS: Why pipelining improves performance and the challenges of implementing pipeliningasifsultanОценок пока нет

- HW2 2021 CS4215Документ5 страницHW2 2021 CS4215Dan PlămădealăОценок пока нет

- Module 4Документ12 страницModule 4Bijay NagОценок пока нет

- MEC3457 Computer Lab 1 PDFДокумент8 страницMEC3457 Computer Lab 1 PDFMuhammad Abbas RawjaniОценок пока нет

- Files 3 Homework Solutions A5 Solution 081Документ5 страницFiles 3 Homework Solutions A5 Solution 081Ivanildo GomesОценок пока нет

- 05 HWДокумент3 страницы05 HWSandipChowdhuryОценок пока нет

- Computer Architecture hw6Документ3 страницыComputer Architecture hw6Jason WheelerОценок пока нет

- FinalДокумент26 страницFinalHứa Đăng KhoaОценок пока нет

- Numerical: Central Processing UnitДокумент28 страницNumerical: Central Processing UnityounisОценок пока нет

- CSC 424 AssignmentДокумент8 страницCSC 424 AssignmentBalsesbiz Consults100% (1)

- Exam2 Fa2014 SolutionДокумент14 страницExam2 Fa2014 Solutionrafeak rafeakОценок пока нет

- Cs433 Sp12 Midterm SolДокумент9 страницCs433 Sp12 Midterm SolSwatiMeenaОценок пока нет

- Multipath 1 NotesДокумент37 страницMultipath 1 NotesNarender KumarОценок пока нет

- Ia Iii - QPДокумент12 страницIa Iii - QPkeerthi3214Оценок пока нет

- HW 5Документ2 страницыHW 5Siddharth SinghОценок пока нет

- Chap1 ECL301L Lab Manual PascualДокумент15 страницChap1 ECL301L Lab Manual PascualpascionladionОценок пока нет

- Exercise 4Документ4 страницыExercise 4Mashavia AhmadОценок пока нет

- Lecture 02-Amdahl's Law, Modern Hardware: ECE 459: Programming For PerformanceДокумент13 страницLecture 02-Amdahl's Law, Modern Hardware: ECE 459: Programming For PerformancemirionОценок пока нет

- COA Unit 3Документ28 страницCOA Unit 3Shivam KumarОценок пока нет

- HW 5 Solutions Processor Performance and PipeliningДокумент5 страницHW 5 Solutions Processor Performance and Pipeliningshantanu pathakОценок пока нет

- EXAMDec2012 SolutionДокумент8 страницEXAMDec2012 Solutionخالد ناهض نايف نجمОценок пока нет

- Prof. Connors ECEN/CSCI 4593 Computer Organization and Design Practice ExamДокумент15 страницProf. Connors ECEN/CSCI 4593 Computer Organization and Design Practice ExamMuhammad UsmanОценок пока нет

- Computer Architecture Midterm1 CmuДокумент30 страницComputer Architecture Midterm1 CmuÖzgürCemBirlerОценок пока нет

- DC Motor SpeedДокумент11 страницDC Motor SpeedJonathanОценок пока нет

- 6.823 Computer System Architecture Quiz 1Документ15 страниц6.823 Computer System Architecture Quiz 1RichardОценок пока нет

- Lab Guide 1: Instruction Level Parallelism and Matrix MultiplicationДокумент3 страницыLab Guide 1: Instruction Level Parallelism and Matrix MultiplicationJoão LourençoОценок пока нет

- Tutorial Module 4Документ9 страницTutorial Module 4Neupane Er KrishnaОценок пока нет

- Calculating Huge NumbersДокумент8 страницCalculating Huge NumbersSoumyajit PradhanОценок пока нет

- Pipeline HazardsДокумент39 страницPipeline HazardsPranidhi RajvanshiОценок пока нет

- 202003271505203215anshu Singh Instructional FormatsДокумент44 страницы202003271505203215anshu Singh Instructional FormatsBhartiОценок пока нет

- FemtoRV32 Piplined Processor ReportДокумент25 страницFemtoRV32 Piplined Processor ReportRatnakarVarunОценок пока нет

- Mat Lab PresentationДокумент6 страницMat Lab PresentationShivamОценок пока нет

- Web-based HL7 Validation System for EMR Data ExchangeДокумент6 страницWeb-based HL7 Validation System for EMR Data ExchangebittronicОценок пока нет

- Seth 740 Fall13 Module5.1 Simd Vector GpuДокумент16 страницSeth 740 Fall13 Module5.1 Simd Vector GpubittronicОценок пока нет

- InterprocessCommunication HandoutДокумент24 страницыInterprocessCommunication HandoutbittronicОценок пока нет

- Gameon 2008 - MDGD - 2D Platform Game PrototypingДокумент3 страницыGameon 2008 - MDGD - 2D Platform Game PrototypingbittronicОценок пока нет

- Java Generics V C++ Templates 2007Документ28 страницJava Generics V C++ Templates 2007flashitОценок пока нет

- Filtry Rich Android Client PDFДокумент56 страницFiltry Rich Android Client PDFdexxt0rОценок пока нет

- JVM ArchitectureДокумент13 страницJVM ArchitectureKISHOREMUTCHARLAОценок пока нет

- Labs - DSP Lab 1Документ2 страницыLabs - DSP Lab 1bittronicОценок пока нет

- Tables of Common Transform PairsДокумент6 страницTables of Common Transform PairsgalaxystarОценок пока нет

- Garlan, Jha, Notkin and Dingel - Reasoning About Implicit Invocation (ICSE '98)Документ13 страницGarlan, Jha, Notkin and Dingel - Reasoning About Implicit Invocation (ICSE '98)bittronicОценок пока нет

- UmtsДокумент56 страницUmtsapi-3835030Оценок пока нет

- Tabla de Transformadas de FourierДокумент5 страницTabla de Transformadas de FourierIvan MorenoОценок пока нет

- CS 61C - Fall 2011 - Garcia - Midterm 1Документ9 страницCS 61C - Fall 2011 - Garcia - Midterm 1Jason XieОценок пока нет

- MIPS Green CardДокумент2 страницыMIPS Green CardMahmoud HelalОценок пока нет

- Circulation in Vacuum Pans: January 2004Документ18 страницCirculation in Vacuum Pans: January 2004REMINGTON SALAYAОценок пока нет

- Public Relations Proposal Template: Executive SummaryДокумент3 страницыPublic Relations Proposal Template: Executive SummaryErmi SusilowatiОценок пока нет

- 0 - Theories of MotivationДокумент5 страниц0 - Theories of Motivationswathi krishnaОценок пока нет

- Guidelines For Planning Conjunctive Use of SUR Face and Ground Waters in Irrigation ProjectsДокумент34 страницыGuidelines For Planning Conjunctive Use of SUR Face and Ground Waters in Irrigation Projectshram_phdОценок пока нет

- Siemens ProjectДокумент17 страницSiemens ProjectMayisha Alamgir100% (1)

- SESSON 1,2 AND 3 use casesДокумент23 страницыSESSON 1,2 AND 3 use casessunilsionОценок пока нет

- Daa M-4Документ28 страницDaa M-4Vairavel ChenniyappanОценок пока нет

- EG3000 ManualДокумент7 страницEG3000 ManualJose Armando Perez AcostaОценок пока нет

- S-S-, AXXX XXX 008 (BIA Sept. 15, 2017)Документ7 страницS-S-, AXXX XXX 008 (BIA Sept. 15, 2017)Immigrant & Refugee Appellate Center, LLCОценок пока нет

- Wireshark Lab: 802.11: Approach, 6 Ed., J.F. Kurose and K.W. RossДокумент5 страницWireshark Lab: 802.11: Approach, 6 Ed., J.F. Kurose and K.W. RossN Azzati LabibahОценок пока нет

- Lifetime Physical Fitness and Wellness A Personalized Program 14th Edition Hoeger Test BankДокумент34 страницыLifetime Physical Fitness and Wellness A Personalized Program 14th Edition Hoeger Test Bankbefoolabraida9d6xm100% (27)

- Rural Perception of SUV CarsДокумент29 страницRural Perception of SUV CarsritusinОценок пока нет

- Letter Advocating For Hazard PayДокумент2 страницыLetter Advocating For Hazard PayQueens PostОценок пока нет

- Statement of Purpose Lanka Venkata Raghava Ravi TejaДокумент2 страницыStatement of Purpose Lanka Venkata Raghava Ravi TejaRavi Teja LvrОценок пока нет

- Nikita Project 01-06-2016Документ38 страницNikita Project 01-06-2016Shobhit GoswamiОценок пока нет

- Deploy A REST API Using Serverless, Express and Node - JsДокумент13 страницDeploy A REST API Using Serverless, Express and Node - JszaninnОценок пока нет

- Lecture 2 Leader-Centred PerspectivesДокумент24 страницыLecture 2 Leader-Centred PerspectivesLIVINGSTONE CAESARОценок пока нет

- GIS BasedLandSuitabilityAnalysistoSupportTransit OrientedDevelopmentTODMasterPlanACaseStudyoftheCampusStationofThammasatUniversityandItsSurroundingCommunitiesДокумент13 страницGIS BasedLandSuitabilityAnalysistoSupportTransit OrientedDevelopmentTODMasterPlanACaseStudyoftheCampusStationofThammasatUniversityandItsSurroundingCommunitiesAzka RamadhanОценок пока нет

- Impact of COVIDДокумент29 страницImpact of COVIDMalkOo AnjumОценок пока нет

- Framing Business EthicsДокумент18 страницFraming Business EthicsJabirОценок пока нет

- Akriti Shrivastava CMBA2Y3-1906Документ6 страницAkriti Shrivastava CMBA2Y3-1906Siddharth ChoudheryОценок пока нет

- Alvarez vs. COMELECДокумент5 страницAlvarez vs. COMELECvanessa3333333Оценок пока нет

- OspndДокумент97 страницOspndhoangdo11122002Оценок пока нет

- EzraCohen TVMasterclass 2.0Документ10 страницEzraCohen TVMasterclass 2.0Pete PetittiОценок пока нет