Академический Документы

Профессиональный Документы

Культура Документы

MOSFET

Загружено:

Gaurav100%(2)100% нашли этот документ полезным (2 голоса)

317 просмотров10 страницBasic computational elements of a counter are JK flip-flops. Simplest way to construct NAND gates is to use transistors.

Исходное описание:

Авторское право

© Attribution Non-Commercial (BY-NC)

Доступные форматы

PPT, PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документBasic computational elements of a counter are JK flip-flops. Simplest way to construct NAND gates is to use transistors.

Авторское право:

Attribution Non-Commercial (BY-NC)

Доступные форматы

Скачайте в формате PPT, PDF, TXT или читайте онлайн в Scribd

100%(2)100% нашли этот документ полезным (2 голоса)

317 просмотров10 страницMOSFET

Загружено:

GauravBasic computational elements of a counter are JK flip-flops. Simplest way to construct NAND gates is to use transistors.

Авторское право:

Attribution Non-Commercial (BY-NC)

Доступные форматы

Скачайте в формате PPT, PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 10

What is the basic component of a n-bit

counter?

• For example, consider a 4-bit counter (one can apply

similar logic to n-bit counter)

• The basic computational elements are JK flip-flops.

• JK flip-flop is based on RS master slave flip-flop with

clear and set.

Note: This is

What is the basic component of JK

basically made

up of 9 NAND

gates. Now our

search for basic

components of a

master-slave flip-flop?

counter reduces

to find out the

simplest way to

construct NAND

gates.

RS master-slave flip-flop. Connecting to one of the S inputs and Q

to one of the R inputs results in a toggle action. The remaining S

inputs are renamed to J and the remaining R inputs are renamed to K.

The resulting configuration is then called a JK master-slave flip-flop .

How to make a NAND gate?

Transistor-transistor logic implementation of a NAND

gate.

Note: It uses two transistors only.

Problem:

We have shown

that we have to

use transistor to

construct a NAND MOSFET

gate. But what

kind of transistor

we will use to

• A single crystal of

construct the

NAND gate if we

silicon can have

have to use the regions with

NAND gate in a

chip? different

conductivity

• Diffusing or

implanting

Phosphorous in Si

➜n-type region

• P-type bulk is

Boron rich.

Problem: How

can you use this

MOSFET as a

switch?

MOSFET

• To modulate the flow of

electrons from the Source

to Drain by applying a

signal to Gate.

• A negative potential on

Gate ➔ repel electrons

just under the oxide ➔ no

current.

• High Positive potential on

Gate ➔ attract electrons to

the region just under the

oxide

Typical dimensions in a MOSFET

• Question: What do you understand if I say, we have 0.18

micron technology?

Answer: Tiniest details that can be produced on a wafer

(Si) are 0.18µm wide.

• Usually we use 0.28 micron or 0.30 micron technology but

IBM 1 GHz Coppermine chip has featured 0.18 µm

interconnects.

• In 0.18 micron technology length of the channel that links

the source to drain is of the order of 35 µm and the

thickness of SiO2 is .02 µm = 200 Angstrom.

Why can’t we farther decrease the

thickness of the Silicon dioxide layer?

• If the oxide is too thin, electrons may tunnel

through it, thus shortcircuiting the gate.

• The thinner the oxide, the slower the device.

Problem: Explain the above statements and prove the

second statement. Hints: A gate in a MOSFET is

an example of a capacitor and the time taken for

the capacitor to discharge is proportional to the

square root of the capacitance.

From the beginning to the present

An early computing machine built from mechanical

gears(Left),a state-of-the art IBM chip with 0.25 micron

features. The production version will contain 200

million transistors.

Transition from micro technology to

nanotechnology

A single-electron transistor (SET) is carved by the tip of a scanning

tunneling microscope (STM). According to classical physics, there is

no way that electrons can get from the 'source' to the 'drain',

because of the two barrier walls either side of the 'island'. But the

structure is too small and electrons can, under certain

circumstances, tunnel through the barriers (but only one electron at

a time can do this!). Thus the SET wouldn't work without quantum

mechanics.

Recent observations

• In 1999 Bell lab researcher demonestrated a MOSFET

with a 500 Angstrom gate. Ballistic effects were visible

and transistors performance was better than would be the

case of wih diffusive electron transport only.

• If the gate shrinks by yet another order of magnitude (50

Angstrom). The device ends up leaking in every direction

and ceases to operate as a switch.

• The physical limits of MOSFET technology can be

overcome by switching to a different technology (say

carbon nanotube based flip-flop (IBM August 2001).

Вам также может понравиться

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (890)

- Analog Circuit Design 1996Документ408 страницAnalog Circuit Design 1996sureshiitmОценок пока нет

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- NTC Syllabus 1st Paper Level 7Документ4 страницыNTC Syllabus 1st Paper Level 7sanjay sahОценок пока нет

- GISupДокумент15 страницGISupGauravОценок пока нет

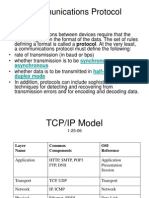

- Communications Protocol: Synchronous or Asynchronous Half-Duplex or Full-Duplex ModeДокумент52 страницыCommunications Protocol: Synchronous or Asynchronous Half-Duplex or Full-Duplex ModeMayur VashistОценок пока нет

- BlackmannДокумент1 страницаBlackmannGauravОценок пока нет

- Submitted By: Gaurav K.Sharma A1607108041 Iv Sem AittmДокумент1 страницаSubmitted By: Gaurav K.Sharma A1607108041 Iv Sem AittmGauravОценок пока нет

- Flip FlopsДокумент35 страницFlip FlopsGaurav0% (1)

- Data StructuresДокумент22 страницыData StructuresGauravОценок пока нет

- The Future of Nanotechnology: Jason Montesanto February 27, 2001Документ31 страницаThe Future of Nanotechnology: Jason Montesanto February 27, 2001GauravОценок пока нет

- Karim Osama - 2018 - FairДокумент2 страницыKarim Osama - 2018 - FairTaher GaMalОценок пока нет

- Voltage References and Biasing: KT/Q, For Example) - Similarly, Any Current We Produce Must Depend On Parameters ThatДокумент15 страницVoltage References and Biasing: KT/Q, For Example) - Similarly, Any Current We Produce Must Depend On Parameters ThatmaheshsamanapallyОценок пока нет

- The Class B Push Pull AmplifierДокумент4 страницыThe Class B Push Pull AmplifierMaryum Ali100% (1)

- CH06 Floorplan, On Chip (2018) SДокумент36 страницCH06 Floorplan, On Chip (2018) S周裕琳Оценок пока нет

- Ec8351 Electronic Circuits I MCQДокумент72 страницыEc8351 Electronic Circuits I MCQShamia SathishОценок пока нет

- MCQ Electronic EngineeringДокумент23 страницыMCQ Electronic EngineeringAbhisek Gautam BTОценок пока нет

- Characteristics of FETДокумент8 страницCharacteristics of FETYogesh KumarОценок пока нет

- Leph 201404 Econtent2019 PDFДокумент27 страницLeph 201404 Econtent2019 PDFPriyanshu VishwakarmaОценок пока нет

- GTU Basic Electronics Course OutlineДокумент3 страницыGTU Basic Electronics Course OutlineHàiđęř KhąñОценок пока нет

- EEE Lab ManualДокумент126 страницEEE Lab ManualSANTHOSHKUMAR G 20BCE1184Оценок пока нет

- EH Liquipoint FTW31 FTW32 DatasheetДокумент24 страницыEH Liquipoint FTW31 FTW32 DatasheetRoomel UrbinaОценок пока нет

- High Speed and Area Efficient Scalable N-Bit DigitДокумент9 страницHigh Speed and Area Efficient Scalable N-Bit DigitN Nagalakshumma GCETОценок пока нет

- Tle5205 2Документ23 страницыTle5205 2Richard MachadoОценок пока нет

- Sony KDL - 32L4000 Chasis MA2Документ84 страницыSony KDL - 32L4000 Chasis MA2GustavoTovarОценок пока нет

- Chapter OneДокумент105 страницChapter Oneadugna abdissaОценок пока нет

- BRY39Документ17 страницBRY39tarpinoОценок пока нет

- Electronics QuestionДокумент18 страницElectronics QuestionJEETENDRAОценок пока нет

- Invivo 3150 MRI Monitor - Service ManualДокумент78 страницInvivo 3150 MRI Monitor - Service ManualKevin StevensОценок пока нет

- Solman HomeworkДокумент7 страницSolman HomeworkFaishal MuhyiddinОценок пока нет

- Stepper Motor Driver Considerations Common ProblemsДокумент12 страницStepper Motor Driver Considerations Common ProblemsErnesto Salomon Jaldín MendezОценок пока нет

- Transistor As A SwitchДокумент2 страницыTransistor As A Switchjojo1216Оценок пока нет

- 50 TOP TRANSISTORS Questions and Answers PDFДокумент8 страниц50 TOP TRANSISTORS Questions and Answers PDFamadullah janОценок пока нет

- 83706Документ3 страницы83706Anonymous t2mTob0% (1)

- Calendario Ano Academico MestradoДокумент3 страницыCalendario Ano Academico MestradoMarques Patricio MambaОценок пока нет

- Gain Consideration in AmplifiersДокумент40 страницGain Consideration in AmplifiersAimanОценок пока нет

- Consonance: 4A, 12V Lead-Acid Battery Charger IC CN3768Документ10 страницConsonance: 4A, 12V Lead-Acid Battery Charger IC CN3768Slaber JuОценок пока нет

- High-Frequency Power Source With Constant Output Power: N. MadzharovДокумент6 страницHigh-Frequency Power Source With Constant Output Power: N. Madzharovvijay patilОценок пока нет