Академический Документы

Профессиональный Документы

Культура Документы

FET

Загружено:

Palak AgrawalИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

FET

Загружено:

Palak AgrawalАвторское право:

Доступные форматы

1

The Field Effect Transistor

The Field Effect Transistor (FET) is a 3-terminal device that has similar applications as

the bipolar junction transistor. The main difference between the FET and the BJT is:

BJ Ts are current-controlled devices

FETs are voltage controlled devices

That is, in BJTs, the output current is dependent on the input base current, I

B

. In FETs,

the output current is dependent of the input gate voltage (V

GS

).

The two major types of FETs are n-channel and p-channel. BJT are bi-polar devices by

nature of its conduction levels being functions of two different charge carriers (electrons

and holes), and FETs are uni-polar devices since they depend solely of only one charge

carrier (electrons for n-channel and holes for p-channel).

FETs have much higher input impedances than BJT. FETs have better temperature

stability and are smaller, making them more useful for IC designs.

we will be looking at 3 main types of FETs namely: Junction FET (JFET),

Metal Oxide Semiconductor FET (MOSFET), and metal semiconductor FET

N-channel

P-channel

JFET

Analogy between BJT & JFET

5

The Field Effect Transistor

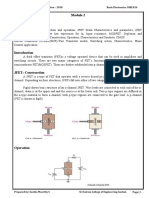

Structure and Characteristics of the JFET

The basic structure of the n-channel JFET consist of a n-channel between embedded layers of p-

type material. The two layers of p-type material are connected together to form the Gate. The

ends of the n-channel forms the Drain and the Source of the JFET. As shown, two pn junctions

are created. In the absence of biasing, depletion regions are formed at both junction.

Whenever bias voltages are applied across the Drain and Source, but not to the Gate, a distinct

flattening of the characteristic curves occurs. As V

DS

increases, the depletion region widens causing

channel width to be reduced. This increase the resistance of the Channel until the condition known as

Pinch-off occurs, labeled Vp on plot. When this happen, the JFET is saturated and Ids remains

constant irrespective of further increase in Vds. In this state, the JFET is an ideal current source.

In FETs: I

D

=I

S

always

working

2

1

|

|

.

|

\

|

=

P

GS

DSS D

V

V

I I

N channel Drain characteristics

Whenever bias voltages are applied across the

Drain and Source, but not to the Gate, a distinct

flattening of the characteristic curves occurs. As

V

DS

increases, the depletion region widens

causing channel width to be reduced. This

increase the resistance of the Channel until the

condition known as Pinch-off occurs, labeled

Vp on plot. When this happen, the JFET is

saturated and Ids remains constant irrespective

of further increase in Vds. In this state, the JFET

is an ideal current source.

In FETs: I

D

= I

S

always

10

The Field Effect Transistor

Applying a Gate Voltage

If V

GS

is varied from 0V to V

P

, the following

characteristic curves are obtained

Note that as V

GS

gets more negative, it takes

a lower V

DS

to reach saturation. When V

GS

= -V

P

, the device will essentially be in

saturation with I

D

= 0 mA. Note that in

the Ohmic region, the JFET is operating as a

voltage controlled resistor.

2

0

1

|

|

.

|

\

|

=

P

GS

d

V

V

r

r

r

0

is resistance when V

GS

=0

Rd is resistance at V

GS

=

negative

For n-channel JFET,

typically

r

0

= 10k (V

GS

= 0, V

P

= -6V)

and

r

d

= 40k at V

GS

= -3V

N channel transfer characteristics

14

The Field Effect Transistor

p-Channel JFET

The p-channel device is constructed in the same exact manner as the n-channel, but

with the n and p-type regions reversed. For this curve, at pinch-off, I

DSS

= 6mA and

when V

GS

= + 6V.

Circuit symbols

16

The Field Effect Transistor

Transfer Characteristics

The relationship between I

D

and V

GS

is defined by Shockleys equation:

The transfer function curve may be plotted from the characteristic curve, as shown. Notice the

parabolic shape due to the square term relationship between I

D

and V

GS

2

1

|

|

.

|

\

|

=

P

GS

DSS D

V

V

I I

Where I

DSS

and V

P

are constants

and V

GS

is variable and controllable

Remember that, when V

GS

=0 , I

D

=I

DSS

and when V

GS

=V

P

, I

D

=0 mA

17

The Field Effect Transistor

Biasing FETs

Recall:

2

1

|

|

.

|

\

|

=

P

GS

DSS D

V

V

I I

IG 0 A and ID =IS for all FETs

For JFETs shockly equation,

18

The Field Effect Transistor

Fixed Bias Configuration for JFET

D D DD DS

P

GS

DSS D

GG GS

G G G R

G

R I V V

V

V

I I

V V

V R R I V

I

G

=

|

|

.

|

\

|

=

=

= = =

~

2

1

0 ) 0 (

0

19

The Field Effect Transistor

Example from text

Determine the following for the circuit

20

The Field Effect Transistor

Self Bias Configuration for JFET

2

1

0

|

|

.

|

\

|

=

=

=

=

=

=

P

S D

DSS D

S D GS

RS GS

RS GS

S D R

S D

V

R I

I I

R I V

V V

V V

R I V

I I

S

21

The Field Effect Transistor

Voltage Divider Biasing for JFET

2

2 1

2

1

0

|

|

.

|

\

|

=

=

=

=

+

=

P

GS

DSS D

S D G GS

R G GS

R GS G

DD

G

V

V

I I

R I V V

V V V

V V V

R R

V R

V

S

S

V

G

V

GS

G

S

D

22

The Field Effect Transistor

Example

Determine

V V

mA I

I

V

V

I I

R I V V

V

k M

k

R R

V R

V

Q

Q

G

D

D

P

GS

DSS D

S D G GS

DD

G

8 . 1

4 . 2

4

) 1500 82 . 1 (

1 008 . 0 1

82 . 1

270 1 . 2

) 16 )( 270 (

2

2

2 1

2

=

=

|

.

|

\

|

=

|

|

.

|

\

|

=

=

=

O + O

O

=

+

=

V V V V

V R I R I V V

V R I V

V R I V V

G D DG

S D D D DD DS

S D S

D D DD D

42 . 8

64 . 6

6 . 3

24 . 10

= =

= =

= =

= =

Department of Physics P24L: Solid State Devices

23

MOSFET (Metal oxide semiconductor FET)

Department of Physics P24L: Solid State Devices

24

Department of Physics P24L: Solid State Devices

25

Difference between the JFET and MOSFET is that the in

MOSFET there is no direct electrical connection between the

gate terminals and the channel of MOSFET.

Due to the fact that MOSFET transistor uses an additional

insulating layer of SIO

2.

which provides good insulation , this is

the region why input impedance of MOSFET is very high as

compare to the JFET.

Depending on the mode of operation, MOSFETs are categorized

as either depletion type or enhancement type. Each further

divided in N-Channel and P-channel MOSFET.

(

The Field Effect Transistor

Department of Physics P24L: Solid State Devices

26

Depletion-type MOSFET: Basic Structure and Circuit Symbols

Circuit symbols

Channel length, L

Circuit symbol

The basic structure of the n-channel Depletion type

MOSFET is shown below. Notice that the Drain,

Source and its connecting n-channel are embedded

into a slab of p-type material. The substrate, SS is

usually connected to the source terminal. The

insulating layer of SiO2 prevents any kind of

electrical contact of gate and channel. This gives the

MOSFET its desirable feature of very high input

impedance. This oxide layer forms a capacitor, C

ox

,

between gate and substrate

Basic Operation and Characteristics of the n-channel

Depletion type MOSFET

The Field Effect Transistor

Department of Physics P24L: Solid State Devices

31

As V

GS

gets more negative, electrons in the channel

or repelled into the p-type substrate where they

will recombine with the holes there. This reduce the

number of free electrons in the channel until I

D

=0.

On the other hand, a +ve charge on the gate will

draw electrons from the substrate into the channel,

effectively increasing the amount of charge carriers,

thus increasing I

D

The Field Effect Transistor

p-Channel Depletion type MOSFET

Its construction is the exact reverse of that of the n-channel

Department of Physics P24L: Solid State Devices

33

Transfer characterstics

Department of Physics P24L: Solid State Devices

35

The Field Effect Transistor

Enhancement-type MOSFET

The structure of the enhancement-type MOSFET has no built-in channel. Its

operation is quite unique and transfer characteristics are not defined by Shockley

equation.

Department of Physics P24L: Solid State Devices

37

The Field Effect Transistor

Operation and Characteristics of Enhancement-type MOSFET

Kirchhoffs voltage law may be applied to get V

DG

= V

DS

- V

GS

When V

GS

= 0, I

D

= 0. However, when V

GS

is positive, the gate

attracts electrons from the substrate

which forms into an n-channel. V

GS

may be increased until a

measurable flow of electrons occurs

between source and drain. The value of V

GS

which causes

measurable current to flow is called the threshold voltage, V

T

.

Further increases in V

GS

will result in pinch-off.

Department of Physics P24L: Solid State Devices

40

The Field Effect Transistor

Notice the increase in separation

T GS DS

V V V

sat

=

The k term is a constant that is a function of the

construction of the device. It may be determined from

( )

( )

2

) (

) (

2

T on GS

on D

T GS D

V V

I

k

V V k I

=

=

I

Don

and V

GSon

may be determined from the curve

Department of Physics P24L: Solid State Devices

42

The Field Effect Transistor

p-Channel Enhancement-type MOSFET

45

The Field Effect Transistor

Example

Determine

V V

mA I

I

V

V

I I

R I V V

V

k M

k

R R

V R

V

Q

Q

G

D

D

P

GS

DSS D

S D G GS

DD

G

8 . 1

4 . 2

4

) 1500 82 . 1 (

1 008 . 0 1

82 . 1

270 1 . 2

) 16 )( 270 (

2

2

2 1

2

=

=

|

.

|

\

|

=

|

|

.

|

\

|

=

=

=

O + O

O

=

+

=

V V V V

V R I R I V V

V R I V

V R I V V

G D DG

S D D D DD DS

S D S

D D DD D

42 . 8

64 . 6

6 . 3

24 . 10

= =

= =

= =

= =

Department of Physics P24L: Solid State Devices

46

The Field Effect Transistor

Complementary MOSFETs (CMOS)

When p-channel and n-channel MOSFETs are constructed on the same substrate, very effective logic circuits may

be created. This configuration consumes very little power, have very fast switching speeds, has very high input

impedance.

Department of Physics P24L: Solid State Devices

47

The Field Effect Transistor

MESFET

The basic structure of a MESFET is shown below

The Gate is connected directly to the metal barrier called Schottky barrier. These type of barriers are

made by depositing a metal such as tungsten directly on an n-type channel. This is unlike the

MOSFETs which are connected to an insulating layer instead.

Department of Physics P24L: Solid State Devices

48

FET Summary Table

Department of Physics P24L: Solid State Devices

49

The Field Effect Transistor

A more Advanced Look at the n-channel MOS (enhancement type): NMOS

These are some of the basis of

IC designs. W/L is important in

Scaling transistor sizes. Latest

Technology has L = 45 nm

Вам также может понравиться

- FETДокумент91 страницаFETpawan_32Оценок пока нет

- Electronics Ch5Документ30 страницElectronics Ch5Santi Navarro MoralОценок пока нет

- ElectronicsДокумент22 страницыElectronicsVARSHITH REDDY JОценок пока нет

- Final MosfetДокумент33 страницыFinal MosfetabdallaОценок пока нет

- L #5: Mosfet C A: Sfsu - E 301 - E L AB Haracteristics and PplicationsДокумент14 страницL #5: Mosfet C A: Sfsu - E 301 - E L AB Haracteristics and PplicationsRudra MishraОценок пока нет

- Mosfet BasicsДокумент51 страницаMosfet BasicsRaghava KatreepalliОценок пока нет

- Unit 5 - Electronic Devices - WWW - Rgpvnotes.inДокумент17 страницUnit 5 - Electronic Devices - WWW - Rgpvnotes.inprakharОценок пока нет

- Lecture 6 2014 02 14 - Electronic System - Outcome2.1 (Analysis of Biasing of The FET)Документ19 страницLecture 6 2014 02 14 - Electronic System - Outcome2.1 (Analysis of Biasing of The FET)koochieeОценок пока нет

- Field Effect TransistorsДокумент40 страницField Effect TransistorsRatanОценок пока нет

- Sedra SmithДокумент52 страницыSedra SmithJiveshОценок пока нет

- Bel 06 Field Effect TransistorДокумент17 страницBel 06 Field Effect TransistorBharavi K SОценок пока нет

- The Basic Structure: Field Effect TransistorДокумент10 страницThe Basic Structure: Field Effect TransistormokhaladОценок пока нет

- Chapter 4:jfet: Junction Field Effect TransistorДокумент68 страницChapter 4:jfet: Junction Field Effect TransistorelectricKKTMОценок пока нет

- Regulation – 2018 Basic Electronics Module 2 FET and SCR CharacteristicsДокумент12 страницRegulation – 2018 Basic Electronics Module 2 FET and SCR CharacteristicsDaisyQueenОценок пока нет

- Lect13 MosfetДокумент8 страницLect13 MosfetAbhay ChaudharyОценок пока нет

- Jfet's & Mosfet'sДокумент62 страницыJfet's & Mosfet'sBabu GundlapallyОценок пока нет

- Introduction To FET's: ELEC 121 Author UnknownДокумент36 страницIntroduction To FET's: ELEC 121 Author UnknownM Junaid Sultan100% (1)

- Unit 2Документ69 страницUnit 2KISHAN SHUKLAОценок пока нет

- Lecture 21: Junction Field Effect Transistors. Source Follower AmplifierДокумент8 страницLecture 21: Junction Field Effect Transistors. Source Follower AmplifiercasprossОценок пока нет

- FET Basics 1Документ63 страницыFET Basics 1Juno Hera Magallanes HuyanОценок пока нет

- Power Mosfets: Introduction To Fet'SДокумент21 страницаPower Mosfets: Introduction To Fet'SSharth KumarОценок пока нет

- Bakir Chapter5Документ91 страницаBakir Chapter5mehtajay1993Оценок пока нет

- FET Basics 1Документ47 страницFET Basics 1padmavathy2kОценок пока нет

- Bipolar Junction Transistor (BJT) Junction Field Effect Transistor (JFET)Документ5 страницBipolar Junction Transistor (BJT) Junction Field Effect Transistor (JFET)sgmdhussainОценок пока нет

- ECE 027 - Module 5 Field Effect TransistorДокумент102 страницыECE 027 - Module 5 Field Effect TransistorMiyuki NakiriОценок пока нет

- MOS Transistor Operation: S/D GateДокумент10 страницMOS Transistor Operation: S/D GateConcetto CantoneОценок пока нет

- Chap3a - FET (v1.2)Документ70 страницChap3a - FET (v1.2)Al AidenОценок пока нет

- Chapter ForДокумент17 страницChapter Forbelacheweshetu222Оценок пока нет

- Mosfet PowerPoint PresentationДокумент71 страницаMosfet PowerPoint PresentationMohammad Rameez100% (7)

- Chapter 10 Field Effect TransistorsДокумент48 страницChapter 10 Field Effect TransistorsanjugaduОценок пока нет

- Center For Advanced Studies in Engineering, Islamabad Electronics LabДокумент9 страницCenter For Advanced Studies in Engineering, Islamabad Electronics LabHussain HadiОценок пока нет

- FET Characteristics BasicsДокумент9 страницFET Characteristics BasicsAbhishek SinghamОценок пока нет

- Chapter 4Документ16 страницChapter 4firomsaguteta12Оценок пока нет

- B.E. FETs and Other Components NotesДокумент12 страницB.E. FETs and Other Components NotesLaxman SalianОценок пока нет

- MOSFETsДокумент26 страницMOSFETsVidit VishnoiОценок пока нет

- DCID Experiment MergedДокумент94 страницыDCID Experiment MergedSumer SainiОценок пока нет

- Electronics Hons C3 FET Field Effect TransistorДокумент21 страницаElectronics Hons C3 FET Field Effect TransistorGawrav BaishyaОценок пока нет

- FET/MOSFET Characteristics: ObjectiveДокумент13 страницFET/MOSFET Characteristics: ObjectiveZeeshan RafiqОценок пока нет

- Controlled Devices FET, BJT, IGBTДокумент51 страницаControlled Devices FET, BJT, IGBTHolloGramОценок пока нет

- 2.5 FET AmplifiersДокумент50 страниц2.5 FET AmplifiersAlfred Anotida MugumwaОценок пока нет

- Field Effect Transistors (Fets) : - Two Types of FetДокумент28 страницField Effect Transistors (Fets) : - Two Types of FetCruise_IceОценок пока нет

- Fet (2014) PDFДокумент87 страницFet (2014) PDFJoanne Mendoza IlaoОценок пока нет

- CH-4 FetДокумент56 страницCH-4 FetNaoda .AОценок пока нет

- Ece-Research Work 1Документ10 страницEce-Research Work 1Peale ObiedoОценок пока нет

- JFET TouhidДокумент32 страницыJFET TouhidA.K.M.TOUHIDUR RAHMANОценок пока нет

- MOSFET DC Analysis Quiz SolutionsДокумент20 страницMOSFET DC Analysis Quiz SolutionsAllen ChandlerОценок пока нет

- EEE 202S Exp4Документ9 страницEEE 202S Exp4Sudipto PramanikОценок пока нет

- Regulation - 2018 Basic Electronics-18ELN14Документ12 страницRegulation - 2018 Basic Electronics-18ELN14Fairoz FairozОценок пока нет

- Unit - Vi Field Effect TransistorДокумент16 страницUnit - Vi Field Effect TransistorBhavaniPrasadОценок пока нет

- Observations: Experimental ValuesДокумент7 страницObservations: Experimental ValuesShibeshwar MandalОценок пока нет

- Chapter 4 - JFET PDFДокумент13 страницChapter 4 - JFET PDFnelsonjnelsonjОценок пока нет

- Microdevices: Mosfets - Metal Oxide Field Effect Transistors N MosfetДокумент11 страницMicrodevices: Mosfets - Metal Oxide Field Effect Transistors N Mosfetblue7nicoОценок пока нет

- Lecture 5 FETДокумент34 страницыLecture 5 FETskh_1987Оценок пока нет

- Electronics Chapter 4Документ16 страницElectronics Chapter 4YidnekachewОценок пока нет

- Eec 234Документ45 страницEec 234Emmanuel100% (1)

- Fundamentals of Electrical Engineering 4 Lab 4 - MOSFET AmplifierДокумент22 страницыFundamentals of Electrical Engineering 4 Lab 4 - MOSFET AmplifierGerson SantosОценок пока нет

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterОт EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterОценок пока нет

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsОт EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsОценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- RF Power Transistor: Hf/Vhf/Uhf N-Channel Power Mosfets: DescriptionДокумент19 страницRF Power Transistor: Hf/Vhf/Uhf N-Channel Power Mosfets: DescriptionGggg ZiizbОценок пока нет

- EC8351-Electronic Circuits-I PDFДокумент21 страницаEC8351-Electronic Circuits-I PDFVish NUОценок пока нет

- Easy LED Color Organ Kit PDFДокумент4 страницыEasy LED Color Organ Kit PDFsiogОценок пока нет

- Physics: Lecture NotesДокумент247 страницPhysics: Lecture Noteswelcome to my worldОценок пока нет

- Micro-Cap 12: Electronic Circuit Analysis Program Reference ManualДокумент142 страницыMicro-Cap 12: Electronic Circuit Analysis Program Reference ManualMartin Estrada SotoОценок пока нет

- Bpe MCQДокумент80 страницBpe MCQSaquibh ShaikhОценок пока нет

- AN-478A TextДокумент12 страницAN-478A TextAl BenОценок пока нет

- Jntuk R07 ECE SyllabusДокумент83 страницыJntuk R07 ECE Syllabussravankumar493100% (1)

- On-Chip Quasi-Static Floating-Gate Capacitance Measurement MethodДокумент5 страницOn-Chip Quasi-Static Floating-Gate Capacitance Measurement MethodAlex WongОценок пока нет

- Csvtu Syllabus Diploma Electrical 3 SemДокумент23 страницыCsvtu Syllabus Diploma Electrical 3 SemVenu Kumar SahuОценок пока нет

- Lect0 IntroДокумент60 страницLect0 IntroRofyda SaadОценок пока нет

- Scaling Effects in MOS DevicesДокумент15 страницScaling Effects in MOS DevicesVikram KumarОценок пока нет

- TEA2018A Power Supply Control CircuitДокумент8 страницTEA2018A Power Supply Control CircuitJean Carlos RamosОценок пока нет

- Use and Misuse of The IR2153 For Feeders Up To 1,5KW - ElettroAmiciДокумент39 страницUse and Misuse of The IR2153 For Feeders Up To 1,5KW - ElettroAmiciimadovОценок пока нет

- Electronic devices: Define hybrid parameters (40Документ4 страницыElectronic devices: Define hybrid parameters (40Mahendra BabuОценок пока нет

- 2010 Foleded Voltage Follower PDFДокумент4 страницы2010 Foleded Voltage Follower PDFrahmanakberОценок пока нет

- RF Power Field - Effect Transistors: MRF6V2150NR1 MRF6V2150NBR1Документ18 страницRF Power Field - Effect Transistors: MRF6V2150NR1 MRF6V2150NBR1edgarlibanioОценок пока нет

- IRF510Документ8 страницIRF510aj_oaomvОценок пока нет

- Current Commutated Chopper Through SimulinkДокумент54 страницыCurrent Commutated Chopper Through SimulinkAbhijeetSinha100% (1)

- Btsym 2020Документ121 страницаBtsym 2020Filipe NunesОценок пока нет

- EEWP ManualДокумент88 страницEEWP Manualsuresh krishnan100% (1)

- Electronics With Discrete ComponentsДокумент354 страницыElectronics With Discrete ComponentsLucas Etienne100% (1)

- Elex 2L Prelim Exam Answer KeyДокумент3 страницыElex 2L Prelim Exam Answer KeyKim VillanuevaОценок пока нет

- Silicon NPN Power Transistors: 2SD669 2SD669AДокумент5 страницSilicon NPN Power Transistors: 2SD669 2SD669AJaPan LifeОценок пока нет

- Multiple transistor amplifier stages benefitsДокумент12 страницMultiple transistor amplifier stages benefitsTristan Paul Guerra OrodioОценок пока нет

- Design Common Source Amplifier for 38.8 dB Gain & 23 MHz BWДокумент7 страницDesign Common Source Amplifier for 38.8 dB Gain & 23 MHz BWAkshay PatharkarОценок пока нет

- 4 2 Paper8Документ57 страниц4 2 Paper8paul catalinОценок пока нет

- Sony NX Series PDFДокумент62 страницыSony NX Series PDFMaya Tes0% (1)

- An induction balance metal detector circuitДокумент7 страницAn induction balance metal detector circuitAlessandro GonzálezОценок пока нет

- S Av17 RepairДокумент2 страницыS Av17 RepairFrancescoPagliano100% (1)