Академический Документы

Профессиональный Документы

Культура Документы

Analog Mosfet - Large Signal and Small Signal Analysis

Загружено:

Anil Kumar YernintiОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Analog Mosfet - Large Signal and Small Signal Analysis

Загружено:

Anil Kumar YernintiАвторское право:

Доступные форматы

By Y. Anil Kumar 13331D5701 M.

TECH (1/1)

Why MOSFET? Large signal analysis

Triode Saturation Cutoff

Small signal analysis

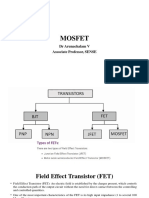

Common Source Common Drain Common Gate

High power JFETs are not common. Enhancement mode is not possible in a JFET, i.e. the gate bias has to be below the source voltage, ( depletion mode) which is awkward for simple power supply arrangements. Hence JFET are not suitable for logic gates. The gate is insulated electrically from the channel, no current flows between the gate and the channel, no matter what the gate voltage is. Thus, the MOSFET has practically infinite impedance . This makes MOSFETs useful for power amplifiers.

MOS metal-oxide-semiconductor structure. MOSFET is a four-terminal device: gate (G), source (S), drain (D) and body (B). The device size (channel region) is specified by channel width (W) and channel length (L). Two kinds of MOSFETs: n-channel (NMOS) and p-channel (PMOS) devices The device structure is basically symmetric in terms of drain and source. Source and drain terminals are specified by the operation voltage.

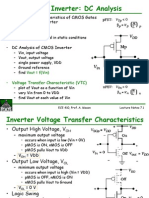

Consider the channel between drain and source as a series of resistors, source is grounded and Vds is connected to drain, so the voltage at each pint along y-axis is given by VGS - VDS(y) At the point VDSsat = VGS - Vt , the channel is pinched off at the drain side. Increasing VDS beyond this value has little effect on the channel shape and iD saturates at this value. Triode region: VDS < VGS - Vt Saturation region: VDS VGS - Vt

Drain current in triode region is

Drain current in saturation region is given by making VDS = VGS - Vth

Transconductance gm is given by

Cutoff : VGS = 0 Sub threshold : 0 < VGS < Vt Sub threshold region is useful in low power, low frequency, and low speed applications Example : Biomedical applications like heart beat measurement, blood pressure measurement

The expression we derived for saturation region assumed that the pinch-off point remains at the drain and thus iD remains constant. In reality, the pinch-off point moves slightly away from the drain: Channel-width Modulation

Recall that Drain-Body and Source-Body diodes should be reversed biased. We assumed that Source is connected to the body (VSB= 0) and VDS = VDB> 0 In a chip (same body for all NMOS), it is impossible to connect all sources to the body (all NMOS sources are connected together. Thus, the body (for NMOS) is connected to the largest negative voltage (negative terminal of the power supply). Doing so, changes the threshold voltage (called Body Effect)

Low frequency model: At low frequencies the capacitors can be neglected

High frequency model: At high frequencies the capacitors need to be taken into account

Common source configuration serves as the gain stage. The disadvantage is high output impedance. BTW, to be a good voltage amplifier, we want Rin large, Ro small and Avo large. Feedback (Rs)lowers the gain of the stage, compared to a pure common-source configuration. However, the benefit is an increased linearity and better high frequency behavior. Common drain (Source Follower) configuration acts as a voltage buffer. It provides no gain, but has low output impedance. It is typically the last stage in a multi-stage amplifier.

This amplifier provides gain and is useful when a specific (low) Rin is required. This is, e.g., the case when the impedance needs to be matched, as with transmission lines (e.g. to 50 ). Another application of the CG configuration is that it acts as a current buffer (current gain close to unity, small Rin, large Rout).

Вам также может понравиться

- MOS Device Physics FinalДокумент15 страницMOS Device Physics FinalnaniОценок пока нет

- Mos Transistor TheoryДокумент144 страницыMos Transistor TheorymailtolokiОценок пока нет

- CMOS Cascode Current MirrorДокумент10 страницCMOS Cascode Current MirrorBinh NguyenОценок пока нет

- Cascode Current MirrorДокумент19 страницCascode Current MirrorReshbha Munjal0% (1)

- To Design An Adaptive Channel Equalizer Using MATLABДокумент43 страницыTo Design An Adaptive Channel Equalizer Using MATLABAngel Pushpa100% (1)

- MOSFETДокумент13 страницMOSFETMarkCabalunaОценок пока нет

- Dynamic Logic Circuits: Kang and Leblebicic, Chapter 9Документ34 страницыDynamic Logic Circuits: Kang and Leblebicic, Chapter 9Lovey SalujaОценок пока нет

- The MOSFET AmplifierДокумент135 страницThe MOSFET AmplifierRodrigo WilliamsОценок пока нет

- MOSFET Current and Voltage CharacteristicsДокумент5 страницMOSFET Current and Voltage Characteristicssri karthik kadapaОценок пока нет

- CMOS CM & Biasing CircuitsДокумент50 страницCMOS CM & Biasing Circuitsabhi_jОценок пока нет

- CMOS Process FlowДокумент35 страницCMOS Process Flowag21937570Оценок пока нет

- VLSI I - V CharacteristicsДокумент46 страницVLSI I - V CharacteristicsMALATHI .LОценок пока нет

- Layout Design RulesДокумент28 страницLayout Design RulesmohanrajОценок пока нет

- Common Source AmplifierДокумент4 страницыCommon Source AmplifierShoumik DeyОценок пока нет

- MosfetДокумент15 страницMosfetAnkita BanerjeeОценок пока нет

- IC Design 3 - Basic MOS Device PhysicsДокумент59 страницIC Design 3 - Basic MOS Device PhysicsNana Sarkodie KwakyeОценок пока нет

- SEL 4283 Analog CMOS IC Design Single Stage Amplifiers: Small Signal Model 1Документ52 страницыSEL 4283 Analog CMOS IC Design Single Stage Amplifiers: Small Signal Model 1jitendraОценок пока нет

- PMOS, NMOS and CMOS Transmission Gate Characteristics.Документ13 страницPMOS, NMOS and CMOS Transmission Gate Characteristics.Prajwal KhairnarОценок пока нет

- Body EffectДокумент2 страницыBody EffectAtharva Lele100% (1)

- 23-3-20 - JFET and MOSFET (B25-27)Документ45 страниц23-3-20 - JFET and MOSFET (B25-27)Shubhankar KunduОценок пока нет

- E3-327 (3) - M SOI MOSFET Oct 2013Документ56 страницE3-327 (3) - M SOI MOSFET Oct 2013Tara VishinОценок пока нет

- Reflection Coefficients For Lattice RealizationДокумент8 страницReflection Coefficients For Lattice RealizationGirija VaniОценок пока нет

- RF Active DevicesДокумент13 страницRF Active DevicesRaj PatelОценок пока нет

- VLSI Questions Answers r3Документ79 страницVLSI Questions Answers r3Gowtham HariОценок пока нет

- EE321L Lab 6 MOSFET Differential AmplifierДокумент3 страницыEE321L Lab 6 MOSFET Differential Amplifierdevpritam100% (1)

- OTA DesignДокумент18 страницOTA DesignAnandОценок пока нет

- 2016 Ch2-MOS TransistorsДокумент47 страниц2016 Ch2-MOS Transistorsជើងកាង ភូមិОценок пока нет

- Delay Time Estimation in Digital DesignДокумент12 страницDelay Time Estimation in Digital DesignSandeep PaulОценок пока нет

- VLSI-5 Short Channel Effects PDFДокумент9 страницVLSI-5 Short Channel Effects PDFPranay KinraОценок пока нет

- Unit 2 - CMOS Logic, Fabrication and LayoutДокумент34 страницыUnit 2 - CMOS Logic, Fabrication and LayoutphillipОценок пока нет

- VLSI DesignДокумент18 страницVLSI Designkishorereddy416Оценок пока нет

- Signals and Systems 1Документ30 страницSignals and Systems 1Rakesh Inani100% (1)

- Lecture18 GRДокумент36 страницLecture18 GRapi-3834272Оценок пока нет

- Lecture 3 Single Stage AmplifiersДокумент76 страницLecture 3 Single Stage Amplifierstranhieu_hcmutОценок пока нет

- 02 Introduction To VLSI and ASIC DesignДокумент23 страницы02 Introduction To VLSI and ASIC DesignSiva Kumar T SОценок пока нет

- Chapter 2 MOS TransistorsДокумент52 страницыChapter 2 MOS TransistorsSesha DreОценок пока нет

- L01 Operational AmplifierДокумент27 страницL01 Operational AmplifierSylvester Delali DordziОценок пока нет

- 6-A Prediction ProblemДокумент31 страница6-A Prediction ProblemPrabhjot KhuranaОценок пока нет

- Ec1354 Vlsi by Suresh.mДокумент75 страницEc1354 Vlsi by Suresh.mSuresh Muthu100% (1)

- Lec3 Single StageДокумент24 страницыLec3 Single Stagerajeevjain09Оценок пока нет

- VLSI Notes 1 PDFДокумент305 страницVLSI Notes 1 PDFKishore KumarОценок пока нет

- Design of Analog FIltersДокумент7 страницDesign of Analog FIltersparshuram kumarОценок пока нет

- CMOS IntroДокумент45 страницCMOS IntroNishanth Nish0% (1)

- Chapter3 Rabaey MOS Capacitances OnlyДокумент19 страницChapter3 Rabaey MOS Capacitances OnlyRaheetha AhmedОценок пока нет

- Two Stage Op-AmpДокумент4 страницыTwo Stage Op-AmpShreerama Samartha G BhattaОценок пока нет

- 111ec0179 - Vishal Mishra - Baseband Transmission TechniquesДокумент8 страниц111ec0179 - Vishal Mishra - Baseband Transmission Techniquesvsmishra1992Оценок пока нет

- ASAP7 TutorialДокумент52 страницыASAP7 TutorialAtmadeep DeyОценок пока нет

- MOSFET OperationДокумент26 страницMOSFET OperationAbhishek Singh100% (1)

- EC8491 Notes PDFДокумент90 страницEC8491 Notes PDFgunasekaran kОценок пока нет

- Combinational Mos Logic Circuits: Basic ConceptsДокумент41 страницаCombinational Mos Logic Circuits: Basic Conceptsflampard24Оценок пока нет

- CMOS Inverter: DC AnalysisДокумент32 страницыCMOS Inverter: DC Analysissreekanthreddy peram50% (2)

- Tutorial On Layout of Mixed-Signal CircuitsДокумент29 страницTutorial On Layout of Mixed-Signal CircuitsPetru NistorОценок пока нет

- Dcs Lab ManualДокумент33 страницыDcs Lab ManualKumaran SgОценок пока нет

- Bi CMOSДокумент6 страницBi CMOSlachuns123Оценок пока нет

- Physics of Power Dissipation in CMOS FET DevicesДокумент70 страницPhysics of Power Dissipation in CMOS FET DevicesPunith Gowda M BОценок пока нет

- Lecture 1Документ39 страницLecture 1Nuniwal JyotiОценок пока нет

- FALLSEM2022-23 BEEE102L TH VL2022230105984 Reference Material I 19-01-2023 003 MOSFETДокумент22 страницыFALLSEM2022-23 BEEE102L TH VL2022230105984 Reference Material I 19-01-2023 003 MOSFETvishwadeepОценок пока нет

- Electronics Hons C3 FET Field Effect TransistorДокумент21 страницаElectronics Hons C3 FET Field Effect TransistorGawrav BaishyaОценок пока нет

- Field Effect Transistors EDITEDДокумент34 страницыField Effect Transistors EDITEDRalph TomarongОценок пока нет

- Block Diagram AnalysisДокумент2 страницыBlock Diagram AnalysisAnil Kumar YernintiОценок пока нет

- Asynchronous Fine Grained Power Gated LogicДокумент35 страницAsynchronous Fine Grained Power Gated LogicAnil Kumar YernintiОценок пока нет

- LPVLSIДокумент25 страницLPVLSIAnil Kumar YernintiОценок пока нет

- Introduction To Linear Integrated CircuitsДокумент12 страницIntroduction To Linear Integrated CircuitsAnil Kumar YernintiОценок пока нет

- XILINX XC SeriesДокумент41 страницаXILINX XC SeriesAnil Kumar YernintiОценок пока нет

- VLSI Design RulesДокумент25 страницVLSI Design RulesAnil Kumar YernintiОценок пока нет

- ASRДокумент13 страницASRAnil Kumar YernintiОценок пока нет

- Y. Anil Kumar V. Sateesh KumarДокумент15 страницY. Anil Kumar V. Sateesh KumarAnil Kumar YernintiОценок пока нет

- Weather Prediction Using Machine Learning TechniquessДокумент53 страницыWeather Prediction Using Machine Learning Techniquessbakiz89Оценок пока нет

- School Form 8 Grade 3Документ20 страницSchool Form 8 Grade 3Mimi Ng PinasОценок пока нет

- Heart Attack Detection ReportДокумент67 страницHeart Attack Detection ReportAkhil TejaОценок пока нет

- Applications PDFДокумент90 страницApplications PDFahmedОценок пока нет

- Course 3 Mathematics Common Core Workbook AnswersДокумент4 страницыCourse 3 Mathematics Common Core Workbook Answerspqdgddifg100% (1)

- Baumer Tdp02 Tdpz02 Ds enДокумент4 страницыBaumer Tdp02 Tdpz02 Ds enQamar ZiaОценок пока нет

- Psyche Finals: Trans 2: Psychotic Disorder: SchizophreniaДокумент4 страницыPsyche Finals: Trans 2: Psychotic Disorder: SchizophreniajisooОценок пока нет

- Character Paragraph Analysis RubricДокумент2 страницыCharacter Paragraph Analysis RubricDiana PerrottaОценок пока нет

- 0801871441Документ398 страниц0801871441xLeelahx50% (2)

- Mat101 w12 Hw6 SolutionsДокумент8 страницMat101 w12 Hw6 SolutionsKonark PatelОценок пока нет

- Revised Exam PEДокумент3 страницыRevised Exam PEJohn Denver De la Cruz0% (1)

- Pathophysiology: DR - Wasfi Dhahir Abid AliДокумент9 страницPathophysiology: DR - Wasfi Dhahir Abid AliSheryl Ann PedinesОценок пока нет

- ICSE Class 10 Chemistry Sample Mock Paper Term 2 Exam 2021 22Документ5 страницICSE Class 10 Chemistry Sample Mock Paper Term 2 Exam 2021 22dhruv sharmaОценок пока нет

- Reaffirmed 1998Документ13 страницReaffirmed 1998builconsОценок пока нет

- What Role Does Imagination Play in Producing Knowledge About The WorldДокумент1 страницаWhat Role Does Imagination Play in Producing Knowledge About The WorldNathanael Samuel KuruvillaОценок пока нет

- 11 - Chapter 3Документ27 страниц11 - Chapter 3sam000678Оценок пока нет

- The Politics of GenreДокумент21 страницаThe Politics of GenreArunabha ChaudhuriОценок пока нет

- On The Margins - A Study of The Experiences of Transgender College StudentsДокумент14 страницOn The Margins - A Study of The Experiences of Transgender College StudentsRory J. BlankОценок пока нет

- TVL-SMAW 12 - Week 4 - Lesson 1 - Concept of Welding Codes and StandardsДокумент9 страницTVL-SMAW 12 - Week 4 - Lesson 1 - Concept of Welding Codes and StandardsNelPalalonОценок пока нет

- Lifecycle of A Frog For Primary StudentsДокумент10 страницLifecycle of A Frog For Primary StudentsMónika KissОценок пока нет

- Introduction To Cobit Framework - Week 3Документ75 страницIntroduction To Cobit Framework - Week 3Teddy HaryadiОценок пока нет

- Encephalopathies: Zerlyn T. Leonardo, M.D., FPCP, FPNAДокумент50 страницEncephalopathies: Zerlyn T. Leonardo, M.D., FPCP, FPNAJanellee DarucaОценок пока нет

- Hydrotest Test FormatДокумент27 страницHydrotest Test FormatRähûl Prätäp SïnghОценок пока нет

- M 995Документ43 страницыM 995Hossam AliОценок пока нет

- Opentext Documentum Archive Services For Sap: Configuration GuideДокумент38 страницOpentext Documentum Archive Services For Sap: Configuration GuideDoond adminОценок пока нет

- IJREAMV06I0969019Документ5 страницIJREAMV06I0969019UNITED CADDОценок пока нет

- The 100 Best Books For 1 Year Olds: Board Book HardcoverДокумент17 страницThe 100 Best Books For 1 Year Olds: Board Book Hardcovernellie_74023951Оценок пока нет

- Zanussi Parts & Accessories - Search Results3 - 91189203300Документ4 страницыZanussi Parts & Accessories - Search Results3 - 91189203300Melissa WilliamsОценок пока нет

- Hamza Akbar: 0308-8616996 House No#531A-5 O/S Dehli Gate MultanДокумент3 страницыHamza Akbar: 0308-8616996 House No#531A-5 O/S Dehli Gate MultanTalalОценок пока нет

- Activity 4 - Energy Flow and Food WebДокумент4 страницыActivity 4 - Energy Flow and Food WebMohamidin MamalapatОценок пока нет