Академический Документы

Профессиональный Документы

Культура Документы

Design Difficult To Route

Загружено:

prakash_shrОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Design Difficult To Route

Загружено:

prakash_shrАвторское право:

Доступные форматы

What Makes a Design Difficult to Route

Charles J. Alpert, Zhuo Li, Michael D. Moffitt, Gi-Joon Nam, Jarrod A. Roy, Gustavo Tellez Presented by Zhicheng Wei

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

KLMH

What Makes a Design Difficult to Route

KLMH

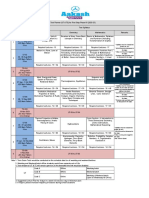

INTRODUCTION AND BACKGROUNDS COMMON CONGESTION METRICS GLOBAL ROUTING CONSTRAINTS DETAILED ROUTING CONSTRAINTS PLACEMENT TECHNIQUES LOGIC SYNTHESIS TECHNIQUES REPEATER INSERTION TECHNIQUES CONCLUSION

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

What Makes a Design Difficult to Route

KLMH

INTRODUCTION Modern technology requires complex wire spacing rules and constraints High performance routing requires multiple wire width (even same layer) Local problems including via spacing rules, switchbox inefficiency, intra-gcell routing

All of these problems make routing hard to model and lead to huge congestion issues!

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

What Makes a Design Difficult to Route

KLMH

BACKGROUNDS Routing problems should be considered in 3D instead of 2D Meet congestion constraints during global routing Try to satisfy capacity in detailed routing with a given global routing solution Over-the-cell routing breaks traditional channel/switchbox model

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

What Makes a Design Difficult to Route

KLMH

COMMON CONGESTION METRICS Total Overflow Average worst X% average worst 20% routing edges below 80% is routable Total routed wirelength (RWL) significantly above Steiner tree may indicate routing difficulties Number of scenic nets wirlelength/minimum Steiner tree length ratio > 1.3 is generally considered scenic Number of nets over X% nets passing through gcells whose congestion is over X% Number of violations Routing runtimes

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

What Makes a Design Difficult to Route

KLMH

COMMON CONGESTION METRICS Total Overflow

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

What Makes a Design Difficult to Route

KLMH

GLOBAL ROUTING CONSTRAINTS Choice of gcell size gcell size too small large global routing space and takes more time to route gcell size too large not able to expose congestion problems and shift burden to detail routing Handling scenic nets go very scenic = bad timing performance impose scenic constrains on the router

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

What Makes a Design Difficult to Route

KLMH

DETAILED ROUTING CONSTRAINTS Prediction failure in global routing hot sports predicted by global routing may not be open and shorts in detailed routing

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

What Makes a Design Difficult to Route

KLMH

DETAILED ROUTING CONSTRAINTS Pin access problem certain configurations make accessing pin from higher metal layer impossible Via modeling challenge Vias do not scale as well as device at each technology node Vias serve as routing blockages which impact local congestion Via modeling becomes non-trivial, esp with different metal pitches

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

What Makes a Design Difficult to Route

KLMH

PLACEMENT TECHNIQUES Congestion caused by time-driven placement

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

10

What Makes a Design Difficult to Route

KLMH

PLACEMENT TECHNIQUES Modern placement focus on minimization of HPWL Uniform placement does not always work! Uniform placement does not mean uniform wire spreading! Consider congestion-driven placement

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

11

What Makes a Design Difficult to Route

KLMH

PLACEMENT TECHNIQUES Congestion Reduction by Iterated Spreading Placement (CRISP) Selectively spreading the placement in regions with high global congestion

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

12

What Makes a Design Difficult to Route

KLMH

LOGIC SYNTHESIS TECHNIQUES Logic synthesis generally ignores placement information Create structures good for timing closure but bad for routing Logic synthesis transforms to alleviate local congestions identify logic fan-in tree which is physically wirelength inefficient rebuild logic tree and place new synthesized gates wirelength is minimized and congestion alleviated

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

13

What Makes a Design Difficult to Route

KLMH

REPEATER INSERTION TECHNIQUES Repeaters are inserted to meet timing constraints Divide long wires into small segments Layer assignment Obtain enormous speed advantage using thick metal for most critical paths Routing congestions caused Corona effect (congestion around corner of blockages) Aggressive layer promotion (fewer resources at higher metal layer)

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

14

What Makes a Design Difficult to Route

KLMH

Aggressive Layer Promotion

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

15

What Makes a Design Difficult to Route

KLMH

Corona Effect

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

16

What Makes a Design Difficult to Route

KLMH

CONCLUSION Physical synthesis issues in placement, global/detail routing, logic synthesis Advanced technologies require more complicated modeling plan Capture more detailed routing effects in global routing stage Estimation techniques need to be fast to optimize routing fast

Lienig

VLSI Physical Design: From Graph Partitioning to Timing Closure

Chapter 6: Detailed Routing

17

Вам также может понравиться

- Slickdeals The Best Deals, Coupons, Promo Codes & DiscountsДокумент75 страницSlickdeals The Best Deals, Coupons, Promo Codes & Discountsprakash_shrОценок пока нет

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5795)

- Upload Me2Документ12 страницUpload Me2prakash_shrОценок пока нет

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- JPT - SearchДокумент3 страницыJPT - Searchprakash_shrОценок пока нет

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- 100 Series Chipset Datasheet Vol 1Документ306 страниц100 Series Chipset Datasheet Vol 1prakash_shrОценок пока нет

- 4 - ADC and DACДокумент6 страниц4 - ADC and DACprakash_shrОценок пока нет

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- LAB 3: PWM and Timer: 2.1 Tool RequirementsДокумент4 страницыLAB 3: PWM and Timer: 2.1 Tool Requirementsprakash_shrОценок пока нет

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- 3 - Interrupts and IOДокумент3 страницы3 - Interrupts and IOprakash_shrОценок пока нет

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Complete NotesДокумент238 страницComplete Notesprakash_shr97% (32)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- Lab2 - PowerModes and ADC MSP430Документ6 страницLab2 - PowerModes and ADC MSP430prakash_shrОценок пока нет

- Lab 1 - OLED, GPIO, InterruptДокумент6 страницLab 1 - OLED, GPIO, Interruptprakash_shrОценок пока нет

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- HW6Документ2 страницыHW6prakash_shrОценок пока нет

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- HW5Документ8 страницHW5prakash_shrОценок пока нет

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- ITProGuru InstallingWindows8 HOL GuideДокумент2 страницыITProGuru InstallingWindows8 HOL Guideprakash_shrОценок пока нет

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- This Presentation Deals With Ten Important Mudras That Can Result in Amazing Health BenefitsДокумент12 страницThis Presentation Deals With Ten Important Mudras That Can Result in Amazing Health Benefitsprakash_shrОценок пока нет

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- VLSI Design of A QDR SRAM Controller: A Project Report OnДокумент53 страницыVLSI Design of A QDR SRAM Controller: A Project Report Onprakash_shrОценок пока нет

- EE4271 VLSI Design: The InverterДокумент32 страницыEE4271 VLSI Design: The Inverterprakash_shrОценок пока нет

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- GRADE 1 To 12 Daily Lesson LOG: TLE6AG-Oc-3-1.3.3Документ7 страницGRADE 1 To 12 Daily Lesson LOG: TLE6AG-Oc-3-1.3.3Roxanne Pia FlorentinoОценок пока нет

- Yukot,+houkelin 2505 11892735 Final+Paper+Group+41Документ17 страницYukot,+houkelin 2505 11892735 Final+Paper+Group+410191720003 ELIAS ANTONIO BELLO LEON ESTUDIANTE ACTIVOОценок пока нет

- Chapter 4 INTRODUCTION TO PRESTRESSED CONCRETEДокумент15 страницChapter 4 INTRODUCTION TO PRESTRESSED CONCRETEyosef gemessaОценок пока нет

- CRM - Final Project GuidelinesДокумент7 страницCRM - Final Project Guidelinesapi-283320904Оценок пока нет

- 1E Star Trek Customizable Card Game - 6 First Contact Rule SupplementДокумент11 страниц1E Star Trek Customizable Card Game - 6 First Contact Rule Supplementmrtibbles100% (1)

- Review Questions Operational Excellence? Software WorksДокумент6 страницReview Questions Operational Excellence? Software WorksDwi RizkyОценок пока нет

- Fire Art Case StudyДокумент15 страницFire Art Case StudyKimberlyHerring100% (1)

- Design Thinking PDFДокумент7 страницDesign Thinking PDFFernan SantosoОценок пока нет

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Changeling by Thomas MiddletonДокумент47 страницThe Changeling by Thomas MiddletonPaulinaOdeth RothОценок пока нет

- Julie Jacko - Professor of Healthcare InformaticsДокумент1 страницаJulie Jacko - Professor of Healthcare InformaticsjuliejackoОценок пока нет

- UT & TE Planner - AY 2023-24 - Phase-01Документ1 страницаUT & TE Planner - AY 2023-24 - Phase-01Atharv KumarОценок пока нет

- Developing Global LeadersДокумент10 страницDeveloping Global LeadersDeepa SharmaОценок пока нет

- Progressivism Sweeps The NationДокумент4 страницыProgressivism Sweeps The NationZach WedelОценок пока нет

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- Zero Power Factor Method or Potier MethodДокумент1 страницаZero Power Factor Method or Potier MethodMarkAlumbroTrangiaОценок пока нет

- WO 2021/158698 Al: (10) International Publication NumberДокумент234 страницыWO 2021/158698 Al: (10) International Publication Numberyoganayagi209Оценок пока нет

- Customizable Feature Based Design Pattern Recognition Integrating Multiple TechniquesДокумент191 страницаCustomizable Feature Based Design Pattern Recognition Integrating Multiple TechniquesCalina Sechel100% (1)

- Focus Charting of FДокумент12 страницFocus Charting of FRobert Rivas0% (2)

- A Terrifying ExperienceДокумент1 страницаA Terrifying ExperienceHamshavathini YohoratnamОценок пока нет

- Analog Electronic CircuitsДокумент2 страницыAnalog Electronic CircuitsFaisal Shahzad KhattakОценок пока нет

- Lead Workplace CommunicationДокумент55 страницLead Workplace CommunicationAbu Huzheyfa Bin100% (1)

- Professional Experience Report - Edu70012Документ11 страницProfessional Experience Report - Edu70012api-466552053Оценок пока нет

- Nahs Syllabus Comparative ReligionsДокумент4 страницыNahs Syllabus Comparative Religionsapi-279748131Оценок пока нет

- ACCA Advanced Corporate Reporting 2005Документ763 страницыACCA Advanced Corporate Reporting 2005Platonic100% (2)

- Becoming FarmersДокумент13 страницBecoming FarmersJimena RoblesОценок пока нет

- Motion To Strike BasedДокумент16 страницMotion To Strike BasedForeclosure Fraud100% (1)

- Conrail Case QuestionsДокумент1 страницаConrail Case QuestionsPiraterija100% (1)

- Kurukku PadaiДокумент4 страницыKurukku PadaisimranОценок пока нет

- Infusion Site Selection and Infusion Set ChangeДокумент8 страницInfusion Site Selection and Infusion Set ChangegaridanОценок пока нет

- The Role of Mahatma Gandhi in The Freedom Movement of IndiaДокумент11 страницThe Role of Mahatma Gandhi in The Freedom Movement of IndiaSwathi Prasad100% (6)

- A Quality Improvement Initiative To Engage Older Adults in The DiДокумент128 страницA Quality Improvement Initiative To Engage Older Adults in The Disara mohamedОценок пока нет