Академический Документы

Профессиональный Документы

Культура Документы

Selected Design Topics: Logic and Computer Design Fundamentals

Загружено:

Yawar Abbas Khan0 оценок0% нашли этот документ полезным (0 голосов)

53 просмотров20 страницdld

Оригинальное название

LCDF4_Chap_06_P

Авторское право

© © All Rights Reserved

Доступные форматы

PPT, PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документdld

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PPT, PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

53 просмотров20 страницSelected Design Topics: Logic and Computer Design Fundamentals

Загружено:

Yawar Abbas Khandld

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PPT, PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 20

Charles Kime & Thomas Kaminski

2008 Pearson Education, Inc.

(Hyperlinks are active in View Show mode)

Chapter 6 Selected Design

Topics

Part 2 Propagation Delay and Timing

Logic and Computer Design Fundamentals

Chapter 6 Part 2 2

Overview

Part 1 The Design Space

Part 2 Propagation Delay and Timing

Propagation Delay

Delay Models

Cost/Performance Tradeoffs

Flip-Flop Timing

Circuit & System Level Timing

Part 3 Asynchronous Interactions

Part 4 - Programmable Implementation

Technologies

Chapter 6 Part 2 3

Propagation Delay

Propagation delay is the time for a change on an input

of a gate to propagate to the output.

Delay is usually measured at the 50% point with

respect to the H and L output voltage levels.

High-to-low (t

PHL

) and low-to-high (t

PLH

) output signal

changes may have different propagation delays.

High-to-low (HL) and low-to-high (LH) transitions are

defined with respect to the output, not the input.

An HL input transition causes:

an LH output transition if the gate inverts and

an HL output transition if the gate does not invert.

Chapter 6 Part 2 4

Propagation Delay (continued)

Propagation delays measured at the midpoint

between the L and H values

What is the expression for the t

PHL

delay for:

a string of n identical buffers?

a string of n identical inverters?

Chapter 6 Part 2 5

Propagation Delay Example

Find t

PHL

, t

PLH

and t

pd

for the signals given

I

N

(

v

o

l

t

s

)

O

U

T

(

v

o

l

t

s

)

t (ns)

1.0 ns per division

Chapter 6 Part 2 6

Delay Models

Transport delay - a change in the output in

response to a change on the inputs occurs after

a fixed specified delay

I nertial delay - similar to transport delay,

except that if the input changes such that the

output is to change twice in a time interval less

than the rejection time, the output changes do

not occur. Models typical electronic circuit

behavior, namely, rejects narrow pulses on

the outputs

Chapter 6 Part 2 7

Delay Model Example

A

A B:

Transport

Delay (TD)

Inertial

Delay (ID)

B

Time (ns) 0 4 2 6 8 10 12 14 16

No Delay

(ND)

a b c d e

Propagation Delay = 2.0 ns Rejection Time = 1 .0 ns

Chapter 6 Part 2 8

Circuit Delay

Suppose gates with delay n ns are

represented for n = 0.2 ns, n = 0.4 ns,

n = 0.5 ns, respectively:

0.2 0.5 0.4

Chapter 6 Part 2 9

Consider a simple

2-input multiplexer:

With function:

Y = A for S = 1

Y = B for S = 0

Glitch is due to delay of inverter

A

0.4

0.5

0.4

S

B

Y

0.2

Circuit Delay

A

S

B

Y

S

Chapter 6 Part 2 10

Fan-out and Delay

The fan-out loading a gates output affects the

gates propagation delay

Example:

One realistic equation for t

pd

for a NAND gate with

4 inputs is:

t

pd

= 0.07 + 0.021 SL ns

SL is the number of standard loads the gate is

driving, i. e., its fan-out in standard loads

For SL = 4.5, t

pd

= 0.165 ns

If this effect is considered, the delay of a gate

in a circuit takes on different values depending

on the circuit load on its output.

Chapter 6 Part 2 11

Cost/Performance Tradeoffs

Gate-Level Example:

NAND gate G with 20 standard loads on its output has a delay

of 0.45 ns and has a normalized cost of 2.0

A buffer H has a normalized cost of 1.5. The NAND gate driving

the buffer with 20 standard loads gives a total delay of 0.33 ns

In which if the following cases should the buffer be added?

1. The cost of this portion of the circuit cannot be more than 2.5

2. The delay of this portion of the circuit cannot be more than 0.40 ns

3. The delay of this portion of the circuit must be less than 0.30 ns

and the cost less than 3.0

Tradeoffs can also be accomplished much higher in the

design hierarchy

Constraints on cost and performance have a major role

in making tradeoffs

Chapter 6 Part 2 12

t

s

- setup time

t

h

- hold time

t

w

- clock

pulse width

t

px

- propa-

gation delay

t

PHL

- High-to-

Low

t

PLH

- Low-to-

High

t

pd

- max (t

PHL

,

t

PLH

)

t

s

t

h

t

p-,min

t

p-,max

t

wH

$

t

wH,min

t

wL

$

t

wL,min

C

D

Q

(b) Edge-triggered (negative edge)

t

h

t

s

t

p-,min

t

p-,max

t

wH

$

t

wH,min

t

wL

$

t

wL,min

C

S

/

R

Q

(a) Pulse-triggered (positive pulse)

Flip-Flop Timing Parameters

Chapter 6 Part 2 13

Flip-Flop Timing Parameters

t

s

- setup time

Master-slave - Equal to the width of the triggering

pulse

Edge-triggered - Equal to a time interval that is

generally much less than the width of the the

triggering pulse

t

h

- hold time - Often equal to zero

t

px

- propagation delay

Same parameters as for gates except

Measured from clock edge that triggers the output

change to the output change

Chapter 6 Part 2 14

Consider a system

comprised of ranks

of flip-flops

connected by logic:

If the clock period is

too short, some

data changes will not

propagate through the

circuit to flip-flop

inputs before the setup

time interval begins

Circuit and System Level Timing

C

D

Q

Q'

C

D

Q

Q'

C

D

Q

Q'

C

D

Q

Q'

C

D

Q

Q'

C

D

Q

Q'

C

D

Q

Q'

C

D

Q

Q'

C

D

Q

Q'

C

D

Q

Q'

CLOCK

CLOCK

Chapter 6 Part 2 15

New Timing Components

t

p

- clock period - The interval between occurrences

of a specific clock edge in a periodic clock

t

pd,COMB

- total delay of combinational logic along

the path from flip-flop output to flip-flop input

t

slack

- extra time in the clock period in addition to

the sum of the delays and setup time on a path

Can be either positive or negative

Must be greater than or equal to zero on all paths for

correct operation

Circuit and System Level Timing

Chapter 6 Part 2 16

Timing components along a path from flip-flop

to flip-flop

Circuit and System Level Timing

(a) Edge-triggered (positive edge)

t

p

t

pd,FF

t

pd,COMB

t

slack

t

s

C

(b) Pulse-triggered (negative pulse)

t

p

t

pd,FF

t

pd,COMB

t

slack

t

s

C

Chapter 6 Part 2 17

Timing Equations

t

p

= t

slack

+ (t

pd,FF

+ t

pd,COMB

+ t

s

)

For t

slack

greater than or equal to zero,

t

p

max (t

pd,FF

+ t

pd,COMB

+ t

s

)

for all paths from flip-flop output to flip-flop input

Can be calculated more precisely by using t

PHL

and t

PLH

values instead of t

pd

values, but

requires consideration of inversions on paths

Circuit and System Level Timing

Chapter 6 Part 2 18

Calculation of Allowable t

pd,COMB

Compare the allowable combinational delay for a

specific circuit:

a) Using edge-triggered flip-flops

b) Using master-slave flip-flops

Parameters

t

pd,FF

(max) = 1.0 ns

t

s

(max) = 0.3 ns for edge-triggered flip-flops

t

s

= t

wH

= 1.0 ns for master-slave flip-flops

Clock frequency = 250 MHz

Chapter 6 Part 2 19

Calculation of Allowable t

pd,COMB

Calculations: t

p

= 1/clock frequency = 4.0 ns

Edge-triggered: 4.0 1.0 + t

pd,COMB

+ 0.3, t

pd,COMB

2.7 ns

Master-slave: 4.0 1.0 + t

pd,COMB

+ 1.0, t

pd,COMB

2.0 ns

Comparison: Suppose that for a gate, average t

pd

=

0.3 ns

Edge-triggered: Approximately 9 gates allowed on a path

Master-slave: Approximately 6 to 7 gates allowed on a path

Chapter 6 Part 2 20

Terms of Use

All (or portions) of this material 2008 by Pearson

Education, Inc.

Permission is given to incorporate this material or

adaptations thereof into classroom presentations and

handouts to instructors in courses adopting the latest

edition of Logic and Computer Design Fundamentals

as the course textbook.

These materials or adaptations thereof are not to be

sold or otherwise offered for consideration.

This Terms of Use slide or page is to be included within

the original materials or any adaptations thereof.

Вам также может понравиться

- Timing Issues in Digital ASIC DesignДокумент101 страницаTiming Issues in Digital ASIC Designnsai_vs1513Оценок пока нет

- 04 Design in Hazard States PDFДокумент43 страницы04 Design in Hazard States PDFJignesh GunasegerenОценок пока нет

- InverterДокумент231 страницаInverterMaitrik Shah100% (1)

- DVD2 JNTU Set1 SolutionsДокумент12 страницDVD2 JNTU Set1 Solutionsకిరణ్ కుమార్ పగడాలОценок пока нет

- Class07 Using Transmission LinesДокумент24 страницыClass07 Using Transmission LinesVikram Raj SinghОценок пока нет

- Understanding Sequential Circuit TimingДокумент8 страницUnderstanding Sequential Circuit Timingchuku7Оценок пока нет

- Selected Design Topics: Logic and Computer Design FundamentalsДокумент15 страницSelected Design Topics: Logic and Computer Design FundamentalsYawar Abbas KhanОценок пока нет

- Sequential & Combinational Timing AnalysisДокумент8 страницSequential & Combinational Timing AnalysisSahil SharmaОценок пока нет

- Directivity: Unidirectional Unchanging InputДокумент11 страницDirectivity: Unidirectional Unchanging InputChinОценок пока нет

- Circuit ElementsДокумент20 страницCircuit Elementsaleph13experienceОценок пока нет

- CEN212 Unit 2 DR KhursheedДокумент123 страницыCEN212 Unit 2 DR Khursheedمنصور الهماميОценок пока нет

- PAGE10Документ4 страницыPAGE10praveenmorampudi42Оценок пока нет

- 74LS193Документ8 страниц74LS193Luis Alberto Villa ChávezОценок пока нет

- Lecture6 Ee689 RX CircuitsДокумент47 страницLecture6 Ee689 RX CircuitsdogudoguОценок пока нет

- Zipper Cmos Logic CircuitДокумент15 страницZipper Cmos Logic CircuitShreerama Samartha G BhattaОценок пока нет

- Chapter4 FA16Документ65 страницChapter4 FA16Haseeb Chughtai100% (1)

- Chapter 6 BДокумент22 страницыChapter 6 BSuraj KumarОценок пока нет

- PLL Charge PumpДокумент33 страницыPLL Charge Pumprah0987Оценок пока нет

- VLSI & ASIC Digital Design Interview QuestionsДокумент6 страницVLSI & ASIC Digital Design Interview QuestionsRupesh Kumar DuttaОценок пока нет

- CO221 KBS7 Timing HazardsДокумент17 страницCO221 KBS7 Timing Hazardsravindulakshan.rl2002Оценок пока нет

- CMOS Sequential Circuit Design Lec.-1Документ22 страницыCMOS Sequential Circuit Design Lec.-1Parag ParandkarОценок пока нет

- What Are The Different Clocking Strategies Employed in VLSI System ? Discuss H-Tree' Clock Distribution in High Density CMOS Circuits ? AnsДокумент6 страницWhat Are The Different Clocking Strategies Employed in VLSI System ? Discuss H-Tree' Clock Distribution in High Density CMOS Circuits ? AnsTozammel Hossain TusharОценок пока нет

- EE241 - Spring 2005: ISSCC 2005Документ28 страницEE241 - Spring 2005: ISSCC 2005milmalОценок пока нет

- DFTДокумент14 страницDFTRahulОценок пока нет

- Experiment No. 3.1Документ5 страницExperiment No. 3.1Harshal AmbatkarОценок пока нет

- Lect17 SeqДокумент18 страницLect17 SeqorengeneralОценок пока нет

- Ofc Lab Manual 2Документ21 страницаOfc Lab Manual 2Shobhit JainОценок пока нет

- 5.2 CMOS Logic Gate Design: Serial or Parallel in Rs Transisto of NoДокумент15 страниц5.2 CMOS Logic Gate Design: Serial or Parallel in Rs Transisto of NoRaj AryanОценок пока нет

- Vlsi Final Notes Unit4Документ21 страницаVlsi Final Notes Unit4RohitParjapatОценок пока нет

- Delay Optimization & Logical EffortsДокумент38 страницDelay Optimization & Logical EffortsiknowiamanidiotОценок пока нет

- Clock and Data Recovery For Serial Digital CommunicationДокумент60 страницClock and Data Recovery For Serial Digital CommunicationJeffrey LiuОценок пока нет

- Thyristor Controlled Reactor: Little Impact On Digital SimulationДокумент12 страницThyristor Controlled Reactor: Little Impact On Digital SimulationNkosinathi MkhizeОценок пока нет

- Flip Flop MultivibratorДокумент161 страницаFlip Flop MultivibratorMuhammad Rizani RusliОценок пока нет

- Timing Analysis: Elec 326 Sequential Circuit TimingДокумент43 страницыTiming Analysis: Elec 326 Sequential Circuit TimingArpit KapoorОценок пока нет

- Timing Parameters of A Digital CircuitДокумент7 страницTiming Parameters of A Digital CircuitShwetabhAsthanaОценок пока нет

- CMOS Design With Delay ConstraintsДокумент22 страницыCMOS Design With Delay ConstraintsKumar Amit VermaОценок пока нет

- Interview QuestionsДокумент27 страницInterview QuestionsRui ChenОценок пока нет

- A Phase-Locked Loop With Embedded Analog-to-Digital Converter For Digital ControlДокумент7 страницA Phase-Locked Loop With Embedded Analog-to-Digital Converter For Digital ControlAbhi BhatОценок пока нет

- dpsd-2 Mark QBДокумент14 страницdpsd-2 Mark QBpriya100% (2)

- Sequential LogicДокумент68 страницSequential LogicbabahussainОценок пока нет

- SOC Unit 1 Part2Документ24 страницыSOC Unit 1 Part2Karthick NpОценок пока нет

- STA FinalДокумент66 страницSTA FinalgauravkshriОценок пока нет

- PLL 2002jun12 Amd CT Ntek An01Документ20 страницPLL 2002jun12 Amd CT Ntek An01hirohirofОценок пока нет

- Low Dynamic Power High Performance Adder: Department of Electronics & Communication Engineering M.Tech Vlsi DesignДокумент11 страницLow Dynamic Power High Performance Adder: Department of Electronics & Communication Engineering M.Tech Vlsi DesignSaranya ChakrabortyОценок пока нет

- Ch02P6 Gate DelaysДокумент10 страницCh02P6 Gate Delaysخالد الروميОценок пока нет

- 74 HC 193Документ14 страниц74 HC 193Rafael GutierrezОценок пока нет

- BPSK Supressed Carrier NRZ Data Demodulation Using Costas Loop On Actel Microsemi FPGAДокумент33 страницыBPSK Supressed Carrier NRZ Data Demodulation Using Costas Loop On Actel Microsemi FPGAPrabhpreet Singh DuaОценок пока нет

- 74HC162 PDFДокумент11 страниц74HC162 PDFIrvson SilveiraОценок пока нет

- Lecture 10 - CpE 690 Introduction To VLSI DesignДокумент54 страницыLecture 10 - CpE 690 Introduction To VLSI Designjvandome100% (1)

- 74LS175Документ3 страницы74LS175Yesenia RojoОценок пока нет

- QA - Copy - Copy2Документ12 страницQA - Copy - Copy2Physical DesignОценок пока нет

- Static Timing Analysis - MaharshiДокумент29 страницStatic Timing Analysis - MaharshiSatish Yada100% (1)

- DelayДокумент31 страницаDelayvarun186Оценок пока нет

- STAДокумент123 страницыSTAMoon Sadia DiptheeОценок пока нет

- Logic Gates: Power and Other Logic FamilyДокумент36 страницLogic Gates: Power and Other Logic FamilybhawnaОценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsОт EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsРейтинг: 1 из 5 звезд1/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Рейтинг: 2.5 из 5 звезд2.5/5 (3)

- Surah Aalaq and QadarДокумент2 страницыSurah Aalaq and QadarYawar Abbas KhanОценок пока нет

- Farman Imam AliДокумент1 страницаFarman Imam AliYawar Abbas KhanОценок пока нет

- Behtareen IshqДокумент100 страницBehtareen IshqYawar Abbas Khan0% (1)

- AarzooДокумент1 страницаAarzooYawar Abbas KhanОценок пока нет

- Hikmat e AliДокумент1 страницаHikmat e AliYawar Abbas KhanОценок пока нет

- Surah Qaria Takasur AsarДокумент2 страницыSurah Qaria Takasur AsarYawar Abbas KhanОценок пока нет

- Chapter 02:vectors and Equilibrium Punjab Text Book Board, LahoreДокумент16 страницChapter 02:vectors and Equilibrium Punjab Text Book Board, Lahoreusamalatif8941Оценок пока нет

- Taharat ChartДокумент1 страницаTaharat ChartYawar Abbas KhanОценок пока нет

- ResignationДокумент1 страницаResignationYawar Abbas KhanОценок пока нет

- Sample LmatДокумент20 страницSample LmatShummaila AfzalОценок пока нет

- Thermodynamics: An Engineering ApproachДокумент21 страницаThermodynamics: An Engineering ApproachYawar Abbas KhanОценок пока нет

- Iqbal Ka KalamДокумент2 страницыIqbal Ka KalamYawar Abbas KhanОценок пока нет

- STEP 7 - System and Standard Functions For TI-S7-ConverterДокумент106 страницSTEP 7 - System and Standard Functions For TI-S7-Convertertricky777Оценок пока нет

- Risalae HuqooqДокумент0 страницRisalae HuqooqHaider E KarrarОценок пока нет

- Combinational Logic DesignДокумент32 страницыCombinational Logic DesignYawar Abbas KhanОценок пока нет

- NTS Book For GAT General Free Download PDFДокумент142 страницыNTS Book For GAT General Free Download PDFMuhammad Ramzan100% (3)

- Majalis Mafhoome NamazДокумент34 страницыMajalis Mafhoome NamazYawar Abbas KhanОценок пока нет

- Selected Design Topics: Logic and Computer Design FundamentalsДокумент15 страницSelected Design Topics: Logic and Computer Design FundamentalsYawar Abbas KhanОценок пока нет

- Combinational Logic Circuits: Logic and Computer Design FundamentalsДокумент57 страницCombinational Logic Circuits: Logic and Computer Design FundamentalsYawar Abbas KhanОценок пока нет

- Ali Garh College Ke NaamДокумент2 страницыAli Garh College Ke NaamYawar Abbas KhanОценок пока нет

- Sequential Circuits: Logic and Computer Design FundamentalsДокумент30 страницSequential Circuits: Logic and Computer Design FundamentalsYawar Abbas KhanОценок пока нет

- Combinational Logic Circuits: Logic and Computer Design FundamentalsДокумент28 страницCombinational Logic Circuits: Logic and Computer Design FundamentalsYawar Abbas KhanОценок пока нет

- Sequential Circuits: Logic and Computer Design FundamentalsДокумент50 страницSequential Circuits: Logic and Computer Design FundamentalsYawar Abbas KhanОценок пока нет

- Combinational Logic Circuits: Logic and Computer Design FundamentalsДокумент59 страницCombinational Logic Circuits: Logic and Computer Design FundamentalsYawar Abbas Khan100% (1)

- ShiaДокумент28 страницShiaYawar Abbas KhanОценок пока нет

- Document 1Документ6 страницDocument 1Yawar Abbas KhanОценок пока нет

- Haram NigahДокумент78 страницHaram NigahMadrasa-Tul-Qaaim [a.s]Оценок пока нет

- Digital Systems and Information: Logic and Computer Design FundamentalsДокумент55 страницDigital Systems and Information: Logic and Computer Design FundamentalsYawar Abbas KhanОценок пока нет

- Document 1Документ6 страницDocument 1Yawar Abbas KhanОценок пока нет

- Touch Voltages Above Ground Gri D: Multiground+Документ104 страницыTouch Voltages Above Ground Gri D: Multiground+Mori PourОценок пока нет

- Catl 3.2v 280ah Lifepo4 BatteryДокумент1 страницаCatl 3.2v 280ah Lifepo4 BatteryYarob ZeebОценок пока нет

- Magnetic Effects of Electric Current QuestionsДокумент2 страницыMagnetic Effects of Electric Current QuestionsVinod KumarОценок пока нет

- 4.1 EHW24 Rules&RegulationsДокумент58 страниц4.1 EHW24 Rules&Regulationsmm22b002Оценок пока нет

- Project Report On Signalling in Indian RailwaysДокумент62 страницыProject Report On Signalling in Indian Railwaysejazmobashir67% (3)

- (FREE) Primary Science Answering TechniquesДокумент70 страниц(FREE) Primary Science Answering TechniquesSyed ZaheedОценок пока нет

- Elysia Mpressor ManualДокумент29 страницElysia Mpressor ManualdavedavedaveОценок пока нет

- 16 Scope of Work Electrician-2Документ3 страницы16 Scope of Work Electrician-2scyper89100% (1)

- SPC 6601Документ11 страницSPC 6601ciro_svОценок пока нет

- Mood CueДокумент5 страницMood CueDave RobisoОценок пока нет

- Seminar On Basic Electrical Engineering (TEE-201) : Topic: Parallel ResonanceДокумент20 страницSeminar On Basic Electrical Engineering (TEE-201) : Topic: Parallel Resonanceiril liquezОценок пока нет

- Operation and Supply ChainДокумент34 страницыOperation and Supply ChainAqib LatifОценок пока нет

- ESD Circuit Synthesis and Analysis Using TCAD and SPICEДокумент4 страницыESD Circuit Synthesis and Analysis Using TCAD and SPICETanuj KumarОценок пока нет

- Instructions: Infiniti Gas Transmitter Model U9500Документ50 страницInstructions: Infiniti Gas Transmitter Model U9500CheloX LОценок пока нет

- Vedantu Chapter 1 Physics Class 12 PDFДокумент48 страницVedantu Chapter 1 Physics Class 12 PDFJISHNU DUHANОценок пока нет

- Irf 3205 SДокумент10 страницIrf 3205 SfingersoundОценок пока нет

- NFS-DHA-E-TC-05 - Testing of Earthing and LPSДокумент25 страницNFS-DHA-E-TC-05 - Testing of Earthing and LPSirshadОценок пока нет

- 2 SC 2078Документ3 страницы2 SC 2078gerler jhony hernandez rodriguezОценок пока нет

- Sharp - CDBA3000 PDFДокумент60 страницSharp - CDBA3000 PDFSergioОценок пока нет

- Cathodic Protection Decoupling Devices: Page NoДокумент9 страницCathodic Protection Decoupling Devices: Page NoreninbabaskiОценок пока нет

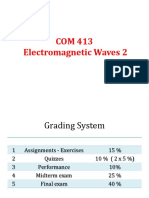

- Lecture - 0 - Course DescriptionДокумент5 страницLecture - 0 - Course DescriptionNour YehiaОценок пока нет

- Product Cs Pg34 PDFДокумент1 страницаProduct Cs Pg34 PDFMunir KadernaniОценок пока нет

- Mooer Red Truck Manual 480465Документ12 страницMooer Red Truck Manual 480465Bruno FreitasОценок пока нет

- Reference Probes - Semi Standards: ThermocouplesДокумент3 страницыReference Probes - Semi Standards: ThermocouplesRudolfОценок пока нет

- Sitras CSG - Pi - 112 - 76Документ4 страницыSitras CSG - Pi - 112 - 76Luteca TecaОценок пока нет

- Copy of Copy of Copy of ORF 2008Документ1 447 страницCopy of Copy of Copy of ORF 2008Mary Jane Katipunan CalumbaОценок пока нет

- Power System Objective Type-RbcДокумент19 страницPower System Objective Type-Rbcmarlon mamacОценок пока нет

- บทที่ 4 - - Induction - Machine - new - 2019 - wt - handoutДокумент49 страницบทที่ 4 - - Induction - Machine - new - 2019 - wt - handoutPanuwat NiyomkitjakankulОценок пока нет

- UniGear 500R - IEC Product Presentation 09-12 (En)Документ20 страницUniGear 500R - IEC Product Presentation 09-12 (En)Abid Sufian HusinОценок пока нет

- MV Switchgear Inspection and Test Procedure: October 2019Документ21 страницаMV Switchgear Inspection and Test Procedure: October 2019sabamalarОценок пока нет