Академический Документы

Профессиональный Документы

Культура Документы

SMT and CMP Architectures

Загружено:

ChippyVijayanАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

SMT and CMP Architectures

Загружено:

ChippyVijayanАвторское право:

Доступные форматы

SMT and CMP Architectures

DINESH

INTRODUCTION

Contemporary forms of parallelism

Instruction-level parallelism(ILP)

Wide-issue Superscalar processors (SS)

4 or more instruction per cycle

Executing a single program or thread

Attempts to find multiple instructions to issue each cycle.

Out-of-order execution => instructions are sent to execution

units based on instruction dependencies rather than program

order

Thread-level parallelism(TLP)

Fine-grained multithreaded superscalars(FGMS)

Contain hardware state for several threads

Executing multiple threads

On any given cycle a processor executes instructions from one

of the threads

Multiprocessor(MP)

Performance improved by adding more CPUs

Simultaneous Multithreading

Key idea

Issue multiple instructions from multiple threads each

cycle

Features

Fully exploit thread-level parallelism and instruction-

level parallelism.

Multiple functional units

Modern processors have more functional units available then a

single thread can utilize.

Register renaming and dynamic scheduling

Multiple instructions from independent threads can co-exist

and co-execute.

Summary: Multithreaded Categories

4

T

i

m

e

(

p

r

o

c

e

s

s

o

r

c

y

c

l

e

)

Superscalar Fine-Grained Coarse-Grained

Simultaneous

Multithreading

Thread 1

Thread 2

Thread 3

Thread 4

Thread 5

Idle slot

Horizontal dimension represents the instruction issue

capabilty in each clock cycles.

Vertical dimension represents a sequence of clock cycles.

Empty slots indicates that the corresponding issue slots

are unused in that clock cycles.

Superscalar processor with no multithreading:

only one thread is processed in one clock cycle

Use of issue slots is limited by a lack of ILP.

Stalls such as an instruction cache miss leaves the entire processor

idle.

Fine-grained multithreading:

switches threads on every clock cycle

Pro: hide latency of from both short and long stalls

Con: Slows down execution of the individual threads ready to go.

Only one thread issues inst. In a given clock cycle.

Course-grained multithreading:

switches threads only on costly stalls

(e.g., L2 stalls)

Pros: no switching each clock cycle, no slow down for ready-to-go

threads. Reduces no of completely idle clock cycles.

Con: limitations in hiding shorter stalls

Simultaneous Multithreading:

exploits TLP at the same time it exploits ILP with multiple

threads using the issue slots in a single-clock cycle.

issue slots is limited by the following factors:

Imbalances in the resource needs.

Resource availability over multiple threads.

Number of active threads considered.

Finite limitations of buffer.

Ability to fetch enough instructions from

multiple threads.

Practical limitations of what instructions

combinations can issue from one thread and

multiple threads.

Performance Implications of SMT

Single thread performance is likely to go down (caches,

branch predictors, registers, etc. are shared) this effect

can be mitigated by trying to prioritize one thread

While fetching instructions, thread priority can

dramatically influence total throughput a widely

accepted heuristic (ICOUNT): fetch such that each thread

has an equal share of processor resources

With eight threads in a processor with many resources,

SMT yields throughput improvements of roughly 2-4

Alpha 21464 and Intel Pentium 4 are examples of SMT

Effectively Using Parallelism on a SMT Processor

Parallel workload

threads SS MP2 MP4 FGMT SMT

1 3.3 2.4 1.5 3.3 3.3

2 -- 4.3 2.6 4.1 4.7

4 -- -- 4.2 4.2 5.6

8 -- -- -- 3.5 6.1

Instruction Throughput executing a parallel workload

Comparison of SMT vs

Superscalar

SMT processors are compared to base superscalar

processors in several key measures :

Utilization of functional units.

Utilization of fetch units.

Accuracy of branch predictor.

Hit rates of primary caches.

Hit rates of secondary caches.

Performance improvement:

Issue slots.

Funtional units.

Renaming registers.

CMP Architecture

Chip-level multiprocessing(CMP or multicore):

integrates two or more independent cores(normally a

CPU) into a single package composed of a single

integrated circuit(IC), called a die, or more dies

packaged, each executing threads independently.

Every funtional units of a processor is duplicated.

Multiple processors, each with a full set of

architectural resources, reside on the same die

Processors may share an on-chip cache

or each can have its own cache

Examples: HP Mako, IBM Power4

Challenges: Power, Die area (cost)

Single core computer

Single core

Single core CPU chip

Multi-core CPU chip

Core 1 Core 2

Core 3

Core 4

Chip Multithreading = Chip Multiprocessing + Hardware

Multithreading.

Chip Multithreading is the capability of a processor to process

multiple s/w threads simulataneous h/w threads of execution.

CMP is achieved by multiple cores on a single chip or multiple

threads on a single core.

CMP processors are especially suited to server workloads, which

generally have high levels of Thread-Level Parallelism(TLP).

Chip Multithreading

CMPs Performance

CMPs are now the only way to build high performance

microprocessors , for a variety of reasons:

o Large uniprocessors are no longer scaling in performance,

because it is only possible to extract a limited amount of

parallelism from a typical instruction stream.

o Cannot simply ratchet up the clock speed on todays

processors,or the power dissipation will become prohibitive.

o CMT processors support many h/w strands through efficient

sharing of on-chip resources such as pipelines, caches and

predictors.

o CMT processors are a good match for server workloads,which

have high levels of TLP and relatively low levels of ILP.

SMT and CMP

The performance race between SMT and CMP is not yet decided.

CMP is easier to implement, but only SMT has the ability to hide

latencies.

A functional partitioning is not exactly reached within a SMT

processor due to the centralized instruction issue.

o A separation of the thread queues is a possible solution,

although it does not remove the central instruction issue.

o A combination of simultaneous multithreading with the CMP

may be superior.

Research : combine SMT or CMP organization with the ability to

create threads with compiler support of fully dynamically out of a

single thread.

o Thread-level speculation

o Close to multiscalar

T

i

m

e

(

P

r

o

c

e

s

s

o

r

c

y

c

l

e

)

Multiprocessor vs. SMT

Multiprocessor(MP2) SMT

Unutilized

Thread 1

Thread 2

THANK U GUYS

Вам также может понравиться

- Mechatronics Test Questions Set - 1Документ13 страницMechatronics Test Questions Set - 1ChippyVijayanОценок пока нет

- Hotel Pre Opening ChecklistДокумент16 страницHotel Pre Opening ChecklistDavid Frost87% (15)

- Chapter 3 (Part I) - CPU OrganizationДокумент40 страницChapter 3 (Part I) - CPU OrganizationKirubel EsayasОценок пока нет

- O - L English - Test 10 ActivitiesДокумент12 страницO - L English - Test 10 ActivitiesNoël Perera100% (5)

- Advanced Operating SystemsДокумент51 страницаAdvanced Operating SystemsaidaraОценок пока нет

- PLC, PLC Ladder, PLC Ebook, PLC Programming, - PLC Scada Dcs Interview Questions and Answers 2Документ5 страницPLC, PLC Ladder, PLC Ebook, PLC Programming, - PLC Scada Dcs Interview Questions and Answers 2ChippyVijayanОценок пока нет

- CH 9 Telephone and Cable Networks For Data Transmission Multiple Choice Questions and Answers MCQ PDFДокумент10 страницCH 9 Telephone and Cable Networks For Data Transmission Multiple Choice Questions and Answers MCQ PDFChippyVijayanОценок пока нет

- 2.operating System 2.introduction To LinuxДокумент23 страницы2.operating System 2.introduction To LinuxSri VardhanОценок пока нет

- Embd Course Pamplet - 3 - 4monthsДокумент2 страницыEmbd Course Pamplet - 3 - 4monthsThanigai Arasu RuthirakottiОценок пока нет

- Unit - 2 Central Processing Unit TOPIC 1: General Register OrganizationДокумент13 страницUnit - 2 Central Processing Unit TOPIC 1: General Register OrganizationRam Prasad GudiwadaОценок пока нет

- ICS 2305 Systems ProgrammingДокумент20 страницICS 2305 Systems ProgrammingMartin AkulaОценок пока нет

- Unit-I - IntroductionДокумент75 страницUnit-I - Introductionking mass100% (1)

- CN Lab ManualДокумент51 страницаCN Lab ManualA Sai NikhithОценок пока нет

- Module 5 RTOS and IDE For Embedded System DesignДокумент229 страницModule 5 RTOS and IDE For Embedded System DesignRuthvik Thumuluri0% (1)

- Lab Assignment 2: MIPS Single-Cycle Implementation: Electrical and Computer Engineering University of CyprusДокумент23 страницыLab Assignment 2: MIPS Single-Cycle Implementation: Electrical and Computer Engineering University of CyprusNguyễn Trường Giang100% (1)

- Computer Organization & ArchitectureДокумент55 страницComputer Organization & ArchitectureSanam KhanОценок пока нет

- 09 - Thread Level ParallelismДокумент34 страницы09 - Thread Level ParallelismSuganya Periasamy50% (2)

- Unit I Fundamentals of Computer Design and Ilp-1-14Документ14 страницUnit I Fundamentals of Computer Design and Ilp-1-14vamsidhar2008Оценок пока нет

- FinalДокумент178 страницFinalBiki JhaОценок пока нет

- 21CS43 Module 5 Microcontroller and Embedded Systems Prof VANARASANДокумент41 страница21CS43 Module 5 Microcontroller and Embedded Systems Prof VANARASANNikhil chandОценок пока нет

- CS8074 Cyber Forensics: Anna University Exams April May 2022 - Regulation 2017Документ2 страницыCS8074 Cyber Forensics: Anna University Exams April May 2022 - Regulation 2017TeCh 5Оценок пока нет

- Module 1 PDFДокумент33 страницыModule 1 PDFKetan Janai100% (1)

- DR Raj Kamal RTOSMobSystemДокумент66 страницDR Raj Kamal RTOSMobSystemShreelakshmi YRОценок пока нет

- COA Lecture NotesДокумент83 страницыCOA Lecture Notessoloamigos23Оценок пока нет

- Osi Model NotesДокумент7 страницOsi Model NotesSuman KumarОценок пока нет

- Unit Iv Rtos Based Embedded System DesignДокумент11 страницUnit Iv Rtos Based Embedded System DesignKartheeswari Saravanan100% (1)

- Computer Organization and ArchitectureДокумент21 страницаComputer Organization and ArchitectureHebziba Jeba Rani S100% (1)

- CS 510-Design and Analysis of Algorithms-Imdad Ullah KhanДокумент3 страницыCS 510-Design and Analysis of Algorithms-Imdad Ullah KhanASIMОценок пока нет

- Linux Programming Lab Manual-New SyllabusДокумент31 страницаLinux Programming Lab Manual-New SyllabusKurumeti Naga Surya Lakshmana KumarОценок пока нет

- Algorithm Analysis and Design - LectureДокумент94 страницыAlgorithm Analysis and Design - LectureSuleiman GargaareОценок пока нет

- CH 5 Basic Computer Organization and DesignДокумент50 страницCH 5 Basic Computer Organization and DesignRohan100% (1)

- CCS341-Data Warehousing Notes-Unit IДокумент30 страницCCS341-Data Warehousing Notes-Unit INISHANTH MОценок пока нет

- Chapter 8: Main Memory: Silberschatz, Galvin and Gagne ©2013 Operating System Concepts - 9 EditionДокумент49 страницChapter 8: Main Memory: Silberschatz, Galvin and Gagne ©2013 Operating System Concepts - 9 EditionSheza NaveedОценок пока нет

- Pipelining: by Based On The Text Book "Computer Organization" by Carl Hamacher Et Al., Fifth EditionДокумент23 страницыPipelining: by Based On The Text Book "Computer Organization" by Carl Hamacher Et Al., Fifth EditionBhavani BsОценок пока нет

- High Performance Computing L T P J C Pre-Requisite Nil Syllabus Version Course ObjectivesДокумент2 страницыHigh Performance Computing L T P J C Pre-Requisite Nil Syllabus Version Course ObjectivesHarish MuthyalaОценок пока нет

- Ec8552 CaoДокумент9 страницEc8552 CaoDr. R. Selvakumar Associate ProfessorОценок пока нет

- Realtime Operating SystemsДокумент1 страницаRealtime Operating Systemssarala20021990100% (1)

- pdc1: MODULE 1: PARALLELISM FUNDAMENTALSДокумент42 страницыpdc1: MODULE 1: PARALLELISM FUNDAMENTALSVandana M 19BCE1763Оценок пока нет

- Bird Species Identification Using Deep LearningДокумент74 страницыBird Species Identification Using Deep LearningaslanОценок пока нет

- Course Plan EsdДокумент3 страницыCourse Plan Esdsaravanaeee2004Оценок пока нет

- RTOS Based Embedded System DesignДокумент16 страницRTOS Based Embedded System DesignSagar DhapkeОценок пока нет

- Aitstpt ssr2015 PDFДокумент328 страницAitstpt ssr2015 PDFTayyabunnissa Begum100% (1)

- SIMD ArchitectureДокумент16 страницSIMD Architecturebinzidd007100% (1)

- Embedded System: Real-Time Operating SystemsДокумент44 страницыEmbedded System: Real-Time Operating SystemsSamuel Adamu100% (1)

- Embedded System-Assignment SolutionДокумент2 страницыEmbedded System-Assignment SolutionManjot KaurОценок пока нет

- Topic - 1 - Characterization of Distributed SystemsДокумент53 страницыTopic - 1 - Characterization of Distributed SystemsAhmad Nazri IbrahimОценок пока нет

- Cs2253 - Computer Architecture 16 Marks Question Bank With Hints Unit - I 1. Explain Basic Functional Units of Computer. Input UnitДокумент18 страницCs2253 - Computer Architecture 16 Marks Question Bank With Hints Unit - I 1. Explain Basic Functional Units of Computer. Input UnitArun VijayОценок пока нет

- Computer ArchitectureДокумент4 страницыComputer Architectureawais nadeemОценок пока нет

- Unit 1: Fundamentals of Programmable DSPS: Bhooshan HumaneДокумент60 страницUnit 1: Fundamentals of Programmable DSPS: Bhooshan HumaneFirozОценок пока нет

- Unix OsДокумент23 страницыUnix OsParvathi Goud100% (1)

- R05 411104ertsДокумент8 страницR05 411104ertsravitejakotiОценок пока нет

- Data Structure Using C Lab (KCS351) : Programming Language/Tool Used: C and MappleДокумент1 страницаData Structure Using C Lab (KCS351) : Programming Language/Tool Used: C and MappleSanjay GuptaОценок пока нет

- Course+Assessment+Rubrics+Microprocessor+Interfacing+ +programmingДокумент3 страницыCourse+Assessment+Rubrics+Microprocessor+Interfacing+ +programmingHassan AliОценок пока нет

- COSC 3100 Brute Force and Exhaustive Search: Instructor: TanvirДокумент44 страницыCOSC 3100 Brute Force and Exhaustive Search: Instructor: TanvirPuneet MehtaОценок пока нет

- Interprocess CommunicationДокумент16 страницInterprocess CommunicationVinuthna ReddyОценок пока нет

- 2mark and 16 OperatingSystemsДокумент24 страницы2mark and 16 OperatingSystemsDhanusha Chandrasegar SabarinathОценок пока нет

- 01.introducing To Routing and Packet ForwardingДокумент4 страницы01.introducing To Routing and Packet ForwardingjentriОценок пока нет

- Unit 2Документ44 страницыUnit 2nagpal3Оценок пока нет

- Vtu Computer Network Lab ManualДокумент61 страницаVtu Computer Network Lab ManualMayank Kushal100% (1)

- Assignment 1Документ4 страницыAssignment 1ashar565Оценок пока нет

- CS3451 Course PlanДокумент10 страницCS3451 Course PlansrinivasaragavanОценок пока нет

- COE4DS4 Lab #2 Introduction To Embedded Software For The NIOS II ProcessorДокумент7 страницCOE4DS4 Lab #2 Introduction To Embedded Software For The NIOS II Processormacmaster69Оценок пока нет

- UNIT 2 Virtualization CCДокумент73 страницыUNIT 2 Virtualization CCjetowi8867Оценок пока нет

- SMT and CMP ArchitecturesДокумент19 страницSMT and CMP Architecturesi_2loveu3235100% (3)

- Kelappan K.Copatan Thirunat S Tutootamthirunat 1945 1945 Satyagraha Kesavan Kelappan Vaikunc, Aswamikat AyyankaliДокумент12 страницKelappan K.Copatan Thirunat S Tutootamthirunat 1945 1945 Satyagraha Kesavan Kelappan Vaikunc, Aswamikat AyyankaliChippyVijayanОценок пока нет

- Syllabus Lecturer in Information Technology GovtДокумент3 страницыSyllabus Lecturer in Information Technology GovtChippyVijayanОценок пока нет

- Engineering Assistant - Electronics-PWDДокумент5 страницEngineering Assistant - Electronics-PWDChippyVijayanОценок пока нет

- Question Bank Unit-I Mechatronics, Sensor and Transducers (2 Mark Questions)Документ11 страницQuestion Bank Unit-I Mechatronics, Sensor and Transducers (2 Mark Questions)ChippyVijayanОценок пока нет

- Cs553a Project TsaiДокумент34 страницыCs553a Project TsaiChippyVijayanОценок пока нет

- AVL TreeДокумент5 страницAVL TreeChippyVijayanОценок пока нет

- 2012lecture1 Optical CommunicationsДокумент22 страницы2012lecture1 Optical CommunicationsChippyVijayanОценок пока нет

- CS1203 System Software UNIT I Question AnsДокумент10 страницCS1203 System Software UNIT I Question AnsChippyVijayanОценок пока нет

- Article FernandesДокумент6 страницArticle FernandesHamilton Pereira da SilvaОценок пока нет

- Operator Manual: WarningДокумент12 страницOperator Manual: WarningMohamed FazilОценок пока нет

- Empowerment Technology (Lesson 2)Документ9 страницEmpowerment Technology (Lesson 2)Zahjid CallangОценок пока нет

- Social Issues and Professional Practice: M1LE2AДокумент2 страницыSocial Issues and Professional Practice: M1LE2AJd AnadonОценок пока нет

- Informative EssayДокумент5 страницInformative EssayTrishia May ReyesОценок пока нет

- Karnataka 04092012Документ62 страницыKarnataka 04092012Chandra ShekarОценок пока нет

- Napa 1069 Oil FilterДокумент1 страницаNapa 1069 Oil Filterkman548Оценок пока нет

- Section 1Документ23 страницыSection 1Ting Wee KietОценок пока нет

- Curriculum SAP GRC Risk Management - Consultant TrainingДокумент2 страницыCurriculum SAP GRC Risk Management - Consultant TraininglawalОценок пока нет

- VRR InfoДокумент3 страницыVRR InfoAngela CardenasОценок пока нет

- 18me710 - Industrial Engineering: Hybrid LayoutДокумент21 страница18me710 - Industrial Engineering: Hybrid LayoutHALO MC NOBLE ACTUALОценок пока нет

- Jpmorgan Chase Final Presentation 1Документ13 страницJpmorgan Chase Final Presentation 1api-545857087Оценок пока нет

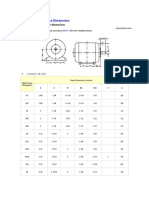

- Nema Electrical Motors FrameДокумент11 страницNema Electrical Motors FrameLuckie IbrahimОценок пока нет

- AAU On Tele BirrДокумент72 страницыAAU On Tele BirrNatinael AbebeОценок пока нет

- Electrical Bushing Adapter - Product Picture From Yueqing Yingdete Electric Co., LTDДокумент2 страницыElectrical Bushing Adapter - Product Picture From Yueqing Yingdete Electric Co., LTDĐoàn Ngọc ĐạiОценок пока нет

- 612f7302a3a18 Colgate Transcend 2021 Case BriefДокумент17 страниц612f7302a3a18 Colgate Transcend 2021 Case BriefQuo EtaОценок пока нет

- Assignment No: 5 Intellectual Property Rights and Their Usefulness For EngineersДокумент2 страницыAssignment No: 5 Intellectual Property Rights and Their Usefulness For EngineersNikhil WaghalkarОценок пока нет

- Remote Control System RC 400: Instruction ManualДокумент40 страницRemote Control System RC 400: Instruction ManualГеннадий Дармоедов0% (1)

- Building Information Modeling (BIM) For Construction and Architecture IndustryДокумент25 страницBuilding Information Modeling (BIM) For Construction and Architecture IndustrySandip PalОценок пока нет

- DELLMUPДокумент3 страницыDELLMUPDino ReinadiОценок пока нет

- Kmbn207 Dmec Unit IIIДокумент17 страницKmbn207 Dmec Unit IIIArchi VarshneyОценок пока нет

- G.12 Mon ExamДокумент8 страницG.12 Mon ExamEmmanuel Maria0% (1)

- Debre Markos Institute of Technology (DMIT) School of Computing Software Engineering Academic Program Final Year Project TitleДокумент5 страницDebre Markos Institute of Technology (DMIT) School of Computing Software Engineering Academic Program Final Year Project TitleAwoke AdaneОценок пока нет

- Top Business Directories in Lajpat Nagar - Best Directory Business Delhi Near Me - JustdialДокумент7 страницTop Business Directories in Lajpat Nagar - Best Directory Business Delhi Near Me - Justdialblr.visheshОценок пока нет

- Basic ElectronicsДокумент1 страницаBasic ElectronicsBibin K VijayanОценок пока нет

- Lynx Door Operator TechService2Документ30 страницLynx Door Operator TechService2Mike SharpeОценок пока нет

- ASB 2011 12 09 TCR Containment-1Документ3 страницыASB 2011 12 09 TCR Containment-1K MОценок пока нет

- Stiff OdeДокумент25 страницStiff OdeBereket HidoОценок пока нет

- Greater Rotor For Greater Benefit: The New SG 8.0-167 DDДокумент2 страницыGreater Rotor For Greater Benefit: The New SG 8.0-167 DDRABIH EL MEDAWARОценок пока нет