Академический Документы

Профессиональный Документы

Культура Документы

Ch1 Background

Загружено:

invincible_shalin6954Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Ch1 Background

Загружено:

invincible_shalin6954Авторское право:

Доступные форматы

1: Background 1

System Programming ()

Main goal:

What is a system

software?

Compiler

Assembler

Loader and Linker

Debugger

To design and

implementation of

system software.

Book content:

Background (SIC & SIC/XE)

Assemblers

Loaders and Linkers

Macro Processors

Compilers

Operating Systems

Other system software

Software Engineering Issues

1: Background 2

Chapter I: Background

Chapter goal:

To familiar with a pseudo

machines: SIC (SIC/XE)

SIC

(Simplified Instructional

Computer)

SIC/XE

(XE stands for extra

equipment)

Overview:

The SIC

SIC machine architecture

SIC programming examples

SIC/XE machine architecture

SIC/XE programming

examples

Machine dependency

1: Background 3

Why using SIC machine?

Most system software differs from application

software is machine dependency.

System software are usually related to the architecture

of the machine on which they are to run.

SIC is a hypothetical computer that has been carefully

designed to include the hardware features most often

found on real machine.

The SIC machine

1: Background 4

Memory

8-bit bytes

Word: 24 bits (three consecutive bytes)

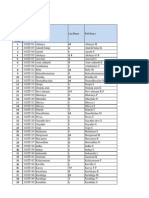

Registers

Each register is 24 bits in length.

The SIC machine architecture

1: Background 5

Data formats

Addressing modes.

The SIC machine architecture (cont.)

1: Background 6

Instruction set

Load and store registers (LDA, LDX, STA, STX, etc.)

Integer arithmetic operations (ADD, SUB, MUL, DIV)

Compare the value in register A with a word

in memory (COMP)

Conditional jump instructions (JLT, JEQ, JGT)

For detailed see Appendix A

Input and Output

Test device (TD), Read data (RD), Write data (WD)

The SIC machine architecture (cont.)

1: Background 7

Data movement

The SIC programming examples

1: Background 8

Arithmetic operations

The SIC programming examples (cont.)

1: Background 9

Looping and indexing operations

The SIC programming examples (cont.)

MOVECH

STR1

STR2

ZERO

ELEVEN

1: Background 10

Indexing and looping operations

The SIC programming examples (cont.)

1: Background 11

Input and output operations

The SIC programming examples (cont.)

1: Background 12

Subroutine call and record input operations

The SIC programming examples (cont.)

1: Background 13

Memory

The same as that previously described for SIC.

Maximum memory available on a SIC/XE system is

1MB.

Registers

The SIC/XE machine architecture

1: Background 14

Data formats (48-bit floating point)

f*2^(e-1024)

Instruction formats and addressing modes

e=0 means Format 3 ; e=1 means Format 4

i=0, n=0 means SIC machine (for upward compatible)

i=1, n=0 means immediate addressing

i=0, n=1 means indirect addressing

i=1, n=1 means simple addressing

The SIC/XE machine architecture (cont.)

1: Background 15

1: Background 16

1: Background 17

Instruction set

SIC/XE provides all of the instructions that are available on

the standard versions.

It also provides instructions to perform floating-point

arithmetic operations (ADDF, SUBF, MULF, DIVF..)

Register-to-register arithmetic operations (ADDR,

SUBR,)

Input and Output

SIO (start I/O channel), TIO (test I/O channel) and HIO (halt

I/O channel)

The SIC/XE machine architecture (cont.)

1: Background 18

Data movement

The SIC/XE programming examples

1: Background 19

Data movement

Compared the SIC with SIC/XE

1: Background 20

Arithmetic operations

The SIC/XE programming examples (cont.)

1: Background 21

Looping and indexing operations

The SIC/XE programming examples (cont.)

MOVECH

STR1

STR2

1: Background 22

Indexing and looping operations

The SIC/XE programming examples (cont.)

1: Background 23

Subroutine call and record input operations

The SIC/XE programming examples (cont.)

1: Background 24

CISC: Complex Instruction Set Computers machine.

relatively large and complicated instruction set.

several different instruction formats and length

many different addressing modes.

E.g., VAX, Pentium

The implementation of such an architecture in

hardware tends to be complex.

CISC vs. RISC

1: Background 25

Introduced by Digital Equipment Corporation

(DEC) in 1978.

Memory

All addresses used are byte addresses.

2 bytes forms a word, 4 bytes forms a longword

8 bytes forms a quadword, 16 bytes forms a octaword

Registers

16 general-purpose register. (R15: program counter,

R14: stack pointer, R13: frame pointer, R12: argument

pointer)

The VAX architecture (CISC)

1: Background 26

RISC: Reduced Instruction Set Computers machine

Standard, fixed instruction length

Single-cycle execution of most instructions

Relatively large number of general-purpose registers

Relatively small number of machine instructions

Relatively small number of instruction formats and

addressing modes.

E.g., UltraSPARC, PowerPC, Cray T3E

The implementation of such an architecture in

hardware tends to be simple.

CISC vs. RISC

1: Background 27

Introduced by Sun Microsystem in 1995.

Memory

All addresses used are byte addresses.

2 bytes forms a halfword, 4 bytes forms a word

Registers

A large register file (more than 100 general-purpose

register)

Fixed instruction length

The UltraSPARC architecture (RISC)

Вам также может понравиться

- 4.1 - Introduction To GAДокумент3 страницы4.1 - Introduction To GAinvincible_shalin6954Оценок пока нет

- 4.4 - Computer Implementation - Data Structures, Reproduction, Crossover and MutationДокумент4 страницы4.4 - Computer Implementation - Data Structures, Reproduction, Crossover and Mutationinvincible_shalin6954Оценок пока нет

- 4.3 - The Goals of OptimizationДокумент4 страницы4.3 - The Goals of Optimizationinvincible_shalin6954Оценок пока нет

- 4.5 - Mapping Objective Functions To Fitness FormДокумент4 страницы4.5 - Mapping Objective Functions To Fitness Forminvincible_shalin6954Оценок пока нет

- 4.2 - Robustness of Traditional Optimization and Search TechniquesДокумент4 страницы4.2 - Robustness of Traditional Optimization and Search Techniquesinvincible_shalin6954Оценок пока нет

- Last Date For Submission: 15.03.2017: Assignment-2: Soft Computing (11I006)Документ1 страницаLast Date For Submission: 15.03.2017: Assignment-2: Soft Computing (11I006)invincible_shalin6954Оценок пока нет

- Last Date For Submission: 28.01.2017: Assignment-1: Soft Computing (11I006)Документ1 страницаLast Date For Submission: 28.01.2017: Assignment-1: Soft Computing (11I006)invincible_shalin6954Оценок пока нет

- AndroidДокумент53 страницыAndroidinvincible_shalin6954Оценок пока нет

- Library Based AssignmentДокумент1 страницаLibrary Based Assignmentinvincible_shalin6954Оценок пока нет

- S7, S5, S3 - Optional Test Registration Form - PT IДокумент1 страницаS7, S5, S3 - Optional Test Registration Form - PT Iinvincible_shalin6954Оценок пока нет

- PING@emergency: K.Padma Sri Lakshmi (152IT165) S.Sindhuja (152IT189)Документ3 страницыPING@emergency: K.Padma Sri Lakshmi (152IT165) S.Sindhuja (152IT189)invincible_shalin6954Оценок пока нет

- Futura Presentation ABSTRACT PDFДокумент3 страницыFutura Presentation ABSTRACT PDFinvincible_shalin6954Оценок пока нет

- Operating System MCQДокумент18 страницOperating System MCQinvincible_shalin6954Оценок пока нет

- PDF DSP - Real Time Digital Signal ProcessingДокумент503 страницыPDF DSP - Real Time Digital Signal Processingapi-3721347100% (4)

- PDF DSP - Real Time Digital Signal ProcessingДокумент503 страницыPDF DSP - Real Time Digital Signal Processingapi-3721347100% (4)

- Sathyamangalam: (Repeat The Three Steps For 8 Times)Документ8 страницSathyamangalam: (Repeat The Three Steps For 8 Times)invincible_shalin6954Оценок пока нет

- Base Paper1 PDFДокумент16 страницBase Paper1 PDFinvincible_shalin6954Оценок пока нет

- Bannari Amman Institute of Technology Department of Information TechnologyДокумент7 страницBannari Amman Institute of Technology Department of Information Technologyinvincible_shalin6954Оценок пока нет

- Bse Paper 3 PDFДокумент14 страницBse Paper 3 PDFinvincible_shalin6954Оценок пока нет

- Bannari Amman Institute of Technology Department of Information TechnologyДокумент7 страницBannari Amman Institute of Technology Department of Information Technologyinvincible_shalin6954Оценок пока нет

- Base Paper PDFДокумент14 страницBase Paper PDFinvincible_shalin6954Оценок пока нет

- 4 2Документ6 страниц4 2invincible_shalin6954Оценок пока нет

- Direct HR Cts B.tech ItДокумент6 страницDirect HR Cts B.tech Itinvincible_shalin6954Оценок пока нет

- Bannari Amman Institute of TechnologyДокумент2 страницыBannari Amman Institute of Technologyinvincible_shalin6954Оценок пока нет

- Sic XEДокумент17 страницSic XEinvincible_shalin6954Оценок пока нет

- Poly SyllДокумент45 страницPoly SyllArun RajОценок пока нет

- Ei73 2 MarksДокумент26 страницEi73 2 MarksSandeep Reddy KankanalaОценок пока нет

- S7 IT CTS Eligible ListДокумент22 страницыS7 IT CTS Eligible Listinvincible_shalin6954Оценок пока нет

- Hard Is CD RivesДокумент21 страницаHard Is CD RivesMark DiazОценок пока нет

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (120)

- Addressingmodes 160718095143 PDFДокумент27 страницAddressingmodes 160718095143 PDFmunkhuuОценок пока нет

- Windows Assembly Language and System Programming (2nd Edition) - Barry KaulerДокумент421 страницаWindows Assembly Language and System Programming (2nd Edition) - Barry KaulerFlash WingОценок пока нет

- Jump, Loop and Call Instructions, I002fO Port Programming and 8051 Addressing Modes Assignment.06 - ModifyДокумент3 страницыJump, Loop and Call Instructions, I002fO Port Programming and 8051 Addressing Modes Assignment.06 - ModifyRyan AbsarОценок пока нет

- Lecture NotesДокумент122 страницыLecture NotesTikuk LeeОценок пока нет

- DSP Architecture - Part 1Документ36 страницDSP Architecture - Part 1Sarabjeet SinghОценок пока нет

- Midterms in Computer ArchitectureДокумент23 страницыMidterms in Computer ArchitectureRealyn SolimanОценок пока нет

- Co Unit 1 NotesДокумент51 страницаCo Unit 1 NotesKishan Bhat K100% (1)

- PIC18F Architecture & Addressing ModesДокумент17 страницPIC18F Architecture & Addressing ModesElan JohnsonОценок пока нет

- Unit - 2 ARM Instruction Set-NotesДокумент18 страницUnit - 2 ARM Instruction Set-NotesRAMACHANDRA KHOTОценок пока нет

- Computer Systems 5Th Edition PDF Full ChapterДокумент41 страницаComputer Systems 5Th Edition PDF Full Chapterlawrence.graves202100% (20)

- Unit I-Basic Structure of A Computer: SystemДокумент64 страницыUnit I-Basic Structure of A Computer: SystemPavithra JanarthananОценок пока нет

- Unit 2-MPMCДокумент3 страницыUnit 2-MPMCselva_raj215414Оценок пока нет

- The MMX Instruction Set (ch11 - MMX)Документ38 страницThe MMX Instruction Set (ch11 - MMX)José Alberto Rivera GómezОценок пока нет

- 68 HC 11 UrДокумент50 страниц68 HC 11 UrUthpala PahalavithaƞaОценок пока нет

- Unit Ii PDFДокумент90 страницUnit Ii PDFSelva BabuОценок пока нет

- CS 2252 - Microprocessors and Microcontrollers PDFДокумент3 страницыCS 2252 - Microprocessors and Microcontrollers PDFvelkarthi92Оценок пока нет

- CR8F6122 STMicroelectronicsДокумент89 страницCR8F6122 STMicroelectronicsspotОценок пока нет

- MP Lab ManualДокумент103 страницыMP Lab Manualashish chavanОценок пока нет

- ARM Assembly Language Guide: Common ARM Instructions (And Psuedo-Instructions)Документ7 страницARM Assembly Language Guide: Common ARM Instructions (And Psuedo-Instructions)M. Luthfi Alhadi ZОценок пока нет

- Hw2 SolutionДокумент8 страницHw2 SolutionTun LeОценок пока нет

- 8086 Addressing Modes - Microprocessors Questions and Answers - SanfoundryДокумент6 страниц8086 Addressing Modes - Microprocessors Questions and Answers - SanfoundryAbhay maneОценок пока нет

- MSC IT QuestionsДокумент7 страницMSC IT QuestionsthangaprakashОценок пока нет

- MSP Design WorkshopДокумент646 страницMSP Design WorkshopBouhafs AbdelkaderОценок пока нет

- Blackfin Processor Programming ReferenceДокумент1 042 страницыBlackfin Processor Programming Referencesweet7kyttyОценок пока нет

- UComputer & Interfacing Chapter ThreeДокумент162 страницыUComputer & Interfacing Chapter ThreetesfuОценок пока нет

- Unit3 CPUДокумент40 страницUnit3 CPUKrishna VamsiОценок пока нет

- What Is 8085 Microprocessors: Special Purpose RegisterДокумент14 страницWhat Is 8085 Microprocessors: Special Purpose RegisterSucheta KarОценок пока нет

- Co 18cs34 Notes FinalДокумент141 страницаCo 18cs34 Notes FinalAshishОценок пока нет

- MPMC Assignment-1Документ7 страницMPMC Assignment-113Panya CSE2Оценок пока нет

- Thumb Instruction SetДокумент31 страницаThumb Instruction Setprabhabathi deviОценок пока нет