Академический Документы

Профессиональный Документы

Культура Документы

8088

Загружено:

chandrasekar0 оценок0% нашли этот документ полезным (0 голосов)

201 просмотров34 страницы8088

Авторское право

© © All Rights Reserved

Доступные форматы

PPT, PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документ8088

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PPT, PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

201 просмотров34 страницы8088

Загружено:

chandrasekar8088

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PPT, PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 34

4-1

4446 Design of Microprocessor-Based Systems

Hardware Detail of Intel 8088

Dr. Esam Al_Qaralleh

CE Department

Princess Sumaya University for Technology

4-2

8088 Pin Configuration

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

GND

A14

A13

A12

A11

A10

A9

A8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

NMI

INTR

CLK

GND

VCC

A15

A16 / S3

A17 / S4

A18 / S5

A19 / S6

SS

0

(High)

MN / MX

RD

HOLD (RQ / GT

0

)

HLDA (RQ / GT

1

)

WR (LOCK)

IO / M

(S

2

)

DT / R (S

1

)

DEN

(S

0

)

ALE

(QS

0

)

INTA (QS

1

)

TEST

READY

RESET

10.3 CPU pin descriptions

GND

A14

A13

A12

A11

A10

A9

A8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

NMI

INTR

CLK

GND

Vcc

A15

A16/S3

A17/S4

A18/S5

A19/S6

___

SS0 (HIGH)

___

MN/MX

___

RD

___ ____

HOLD (RQ/GT0)

___ ____

HLDA (RQ/GT1)

___ ______

WR (LOCK)

__ __

IO/M (S2)

__ __

DT/R (S1)

____ __

DEN (S0)

ALE (QS0)

_____

INTA (QS1)

_____

TEST

READY

RESET

1 40

8088

20 21

Minmode operation

signals (MN/MX=1)

Maxmode operation

signals (MN/MX=0)

Address Bus

(outputs)

Time-multiplexed

Address (outputs)/

Data Bus

(bidirectional)

Hardware

interrupt requests

(inputs)

2...5MHz,

1/3 duty cycle

(input)

0V=0,

reference

for all

voltages

5V10%

Time-

multiplexed

Address Bus

/Status signals

(outputs)

Status

signals

(outputs)

Operation Mode,

(input):

1 = minmode

(8088 generates all

the needed control

signals for a small

system),

0 = maxmode

(8288 Bus

Controller expands

the status signals to

generate more

control signals)

Interrupt

acknowledge

(output)

Control

Bus

(in,out)

4-4

8088 Pin Description

GND: 1 & 20 Both need to be connected to ground

VCC: 21 VCC = 5V

CLK: 19 Input 33% duty cycle

1/3*T 2/3*T

MN/MX: 33 Input High Minimum mode

Low Maximum mode

RESET: 21 Input Reset 8088

Duration of logic high must be greater

than 4*T

After reset, 8088 fetches instructions

starting from memory address FFFF0H

Pin Name Pin Number Direction Description

4-5

8088 Pin Description

Pin Name Pin Number Direction Description

READY 22 Input Informs the processor that the selected memory

or I/O device is ready for a data transfer

8088 Selected memory

or I/O device

Data bus

READY READY

wait for

memory

or I/O ready

Start data transfer

4-6

8088 Pin Description

Pin Name Pin Number Direction Description

HOLD 31 Input The execution of the processor is suspended

as long as HOLD is high

HLDA 30 Output Acknowledges that the processor is suspended

8088

Memory

HOLD

HLDA

Device 2

Bus

Procedure for Device 2 to use bus

Drive the HOLD signal of 8088 high

Wait for the HLDA signal of 8088

becoming high

Now, Device2 can send data to bus

4-7

8088 Pin Description

Pin Name Pin Number Direction Description

NMI 17 Input Causes a non-maskable type-2 interrupt

INTR 18 Input Indicates a maskable interrupt request

INTA 24 Output

Indicates that the processor has received an

INTR request and is beginning interrupt

processing

NMI (non-maskable interrupt): a rising edge on NMI causes a type-2 interrupt

INTR: logic high on INTR poses an interrupt request. However, this request can

be masked by IF (Interrupt enable Flag). The type of interrupt caused by

INTR is read from data bus

8088

External

device

Data bus

INTR

INTA

INTR

INTA

Data Bus Int. type

INTA: control when the interrupt type should be loaded onto the data bus

4-8

8088 Pin Description

Pin Name Pin Number Direction Description

ALE 25 Output Indicates the current data on 8088 address/data

bus are address

D Q

G

8088

A[19:8]

ALE

AD[7:0]

D[7:0]

A[7:0]

A[19:8]

D latches

Buffer

4-9

8088 Pin Description

Pin Name Pin Number Direction Description

DEN 26 Output

Disconnects data bus connection

DT / R 27 Output

Indicates the direction of data transfer

8088

AD[7:0]

Data

bus

D[7:0]

DEN

DT/R

DEN DT/ R

DEN DT/R

1 X Disconnected

0 0 To 8088

0 1 From 8088

4-10

8088 Pin Description

Pin Name Pin Number Direction Description

WR 29 Output

Indicates that the processor is writing to memory

or I/O devices

RD 32 Output

IO/ M 28 Output

Indicates that the processor is reading from

memory or I/O devices

Indicates that the processor is accessing whether

memory (IO/M=0) or I/O devices (IO/M=1)

WR

RD

IO/M

8088

Memory

WE

OE

CS

Addr.

Dec.

Addr.

Dec.

IO/M

WR or

RD

I/O

4-11

8088 Pin Description

Pin Name Pin Number Direction Description

AD[7:0] 9-16 I/O

Address / Data bus

A[19:8] 2-8, 35-39 Input

Address bus

SS

0

34 Output

TEST 23 Input

Status Output

It is examined by processor testing instructions

LOCK 29 Input

Lock output is used to lock peripherals off

the system. Activated by using the LOCK:

prefix on any instruction.

QS1 and QS0 24, 25 Input The queue status bits show status of

internal instruction queue. Provided for

access by the numeric coprocessor (8087).

10.3 CPU pin descriptions

S2 S1 S0 Indicated Operation

0 0 0 Interrupt acknowledge

0 0 1 I/O read

0 1 0 I/O write

0 1 1 Halt

1 0 0 Code access

1 0 1 Memory read

1 1 0 Memory write

1 1 1 Passive

8088 Status Signals

Interrupt Triggered on:

Disabled

via

Software Priority

NMI Rising edge No High

INT High level Yes Low

Comparison of NMI and INTR

Signal Input Output Tri-State Minmode Maxmode

CLK * * *

MN/MX * * *

S0,S1,S2 * * *

RESET * * *

READY * * *

HOLD * *

HLDA * *

NMI * * *

INTR * * *

INTA * *

RQ/GT0 * * *

RQ/GT1 * * *

LOCK * * *

ALE * *

DEN * * *

DT/R * * *

WR * * *

RD * * * *

IO/M * * *

AD0-AD7 * * * * *

A8-A19 * * * *

8088 Signal Summary

IOWR

IORD

MEMWR

MEMRD

RD

WR

IO/M

Decoding 8088 memory and I/O read/write signals

4-14

8284 Clock Generator

510

510

100K

10uF

+5V

Ready1

Ready2

RES

RDY1

RDY2

X1

X2

Ready

CLK

RESET

RESET

CLK

Ready

8284

8088

Generates 33% duty cycle clock signal

Generates RESET signal

Synchronizes ready signals from memory

and I/O devices

Basic functions:

Clock generation.

RESET synchronization.

READY synchronization.

Peripheral clock signal.

10.4 The 8284 Clock Generator

RDY1

RDY2

EFI CLK

F/C

CSYNC

AEN1

AEN2 8284

ASYNC

X1 READY

X2 RES RESET

5V

READY1

READY2

5V

10MHz

4K7

2X510

5V

10F

100K

1N4148

CLK

8088

READY

RESET

t

RES

[V]

t

RESET

1L

0L

0 = crystal oscillator

1 = TTL clock on EFI,

synchronized on CSYNC

t

X1,2

[V]

qualifiers for

READY1,-2

1 = one WAIT state

forced by READY 0 = forces the P

to froze the

current bus cycle

inserting WAIT

STATES (all

signals keep their

values), allowing

slower devices

time to properly

answer.

CLK

1/3 f

osc

1/3 duty cycle

4-16

8288 Bus Controller

Separate signals are used for I/O ( IORC and IOWC ) and memory ( MRDC and MWTC ).

Also provided are advanced memory ( AIOWC ) and I/O ( AIOWC ) write strobes plus INTA .

DEN DT/R MRDC

ALE MWTC

S0 IORC

S1 8288 IOWC

S2 INTA

AMWC

AIOWC

IOB AEN CEN

10.5 The 8288 Bus Controller

8286

OE T

8282

STB OE

D Q

LE

CPU Address Bus

(A16-A19,

if needed,

should be

latched the

same way like

AD0-AD7)

CPU Data Bus

A8-A15

AD0-AD7

8088

S0

S1

S2

Memory ReaD Command

Memory WriTe Command

Input/Output Read Command

Input/Output Write Command

INTerrupt Acknowledge

Advanced Memory Write Command

Advanced Input/Output Write Command

Status Signals

(codify the bus

cycle type)

Control

Bus

Max one active at a time,

identifying Memory vs. I/O

and Read vs. Write

Identify the Memory Byte

(one of 2

20

(2

16

in example))

OR the I/O port (one of 2

16

)

to be read OR write

in the current bus cycle

Advanced Write Commands,

providing additional access time

for the selected circuit

Data to be transferred

in the current bus cycle

Data Transmit/Receive

5V

CLK

Address

Latch

Enable

Data Enable

Command Enable

Address Enable I/O Bus only

74LS244

G1 G2

4-18

System Timing Diagrams

T-State:

One clock period is referred to as a T-State

T-State

An operation takes an integer number of T-States

CPU Bus Cycle:

A bus cycle consists of 4 or more T-States

T1 T2 T3 T4

4-19

Dump address on address bus.

Issue a read ( RD ) and set M/ IO to 1.

Wait for memory access cycle.

Memory Read Timing Diagrams

4-20

Memory Read Timing Diagrams

T1 T2

T3 T4

CLK

ALE

A[19:16] A[19:16] S3-S6

A[15:8] A[15:8]

AD[7:0] A[7:0] D[7:0]

IO/M

DT/R

DEN

RD

WR

A[15:8]

AD[7:0]

A[15:0]

Buffer

D latch

Trans

-ceiver

D[7:0]

DT/R

DEN

IO/M

WR

RD

8088

Memory

4-21

Dump address on address bus.

Dump data on data bus.

Issue a write ( WR ) and set M/ IO to 1.

Memory Write Timing Diagrams

4-22

Memory Write Timing Diagrams

T1 T2

T3 T4

CLK

ALE

A[19:16] A[19:16] S3-S6

A[15:8] A[15:8]

AD[7:0] A[7:0] D[7:0]

IO/M

DT/R

DEN

RD

WR

A[15:8]

AD[7:0]

A[15:0]

Buffer

D latch

Trans

-ceiver

D[7:0]

DT/R

DEN

IO/M

WR

RD

8088

Memory

4-23

Bus Timing

During T 1 :

The address is placed on the Address/Data bus.

Control signals M/ IO , ALE and DT/ R specify memory or I/O, latch the

address onto the address bus and set the direction of data transfer on data bus.

During T 2 :

8086 issues the RD or WR signal, DEN , and, for a write, the data.

DEN enables the memory or I/O device to receive the data for writes and the 8086 to

receive the data for reads.

During T 3 :

This cycle is provided to allow memory to access data.

READY is sampled at the end of T 2 .

If low, T 3 becomes a wait state.

Otherwise, the data bus is sampled at the end of T 3 .

During T 4 :

All bus signals are deactivated, in preparation for next bus cycle.

Data is sampled for reads, writes occur for writes.

4-24

Setup & Hold Time

Setup time The time before the rising edge of the clock, while the data must

be valid and constant

Hold time The time after the rising edge of the clock during which the data

must remain valid and constant

4-25

Bus Timing Diagram

4-26

Bus Timing

Timing:

Each BUS CYCLE on the 8086 equals four system clocking periods (T states).

The clock rate is 5MHz , therefore one Bus Cycle is 800ns .

The transfer rate is 1.25MHz .

Memory specs (memory access time) must match constraints of system timing.

For example, bus timing for a read operation shows almost 600ns are needed to

read data.

However, memory must access faster due to setup times, e.g. Address setup and data

setup.

This subtracts off about 150ns .

Therefore, memory must access in at least 450ns minus another 30-40ns guard band for

buffers and decoders.

420ns DRAM required for the 8086.

4-27

10.6 System Time Diagrams - CPU Bus Cycle

T

2

T

3

T

W

T

4

Read Cycle

(instruction fetch and memory operand read)

A

8

- A

15

Address latches store the actual values

Memory Cycle (I/O cycle is similar but IO/M = 1)

S

3

- S

6

Tri-state

A

16

-A

19

A

0

- A

7

T

1

CLK

ALE

IO/M

A

16

- A

19

A

8

- A

15

RD

AD

0

- AD

7

DT/R

READY

DEN

Direction READ for the Data Buffer

Enables Data Buffer

WR

AD

0

- AD

7

DT/R

Write Cycle (memory operand write)

A

0

- A

7

D

0

- D

7

(Data out)

DEN

Direction READ for the Data Buffer

Enables Data Buffer

Memory reads Data Bus

The slow device drives READY= 0

the P samples READY

(if 0 a WAIT state follows)

D

0

- D

7

(Data in)

P reads Data Bus

4-29

Interrupt Acknowledge Timing Diagrams

T1 T2

T3 T4

CLK

INTR

INTA

D[7:0]

8088

External

device

Data bus

INTR

INTA

It takes one bus cycle to perform an interrupt acknowledge

During T1, the process tri-states the address bus

During T2, INTA is pulled low and remains low until it becomes inactive in T4

The interrupting devices places an 8-bit interrupt type during INTA is active

Int. Type

4-30

HOLD/HLDA Timing Diagrams

T2 T3 T4

CLK

HOLD

8088

Memory

HOLD

HLDA

Device 2

Bus

HLDA

Hold State

The processor will examine HOLD signal at every rising clock edge

If HOLD=1, the processor will pull HLDA high at the end of T4 state (end of

the execution of the current instruction) and suspend its normal operation

If HOLD=0, the processor will pull down HLDA at the falling clock edge

and resume its normal operation

10.6 System Time Diagrams - INT and HOLD

T

4

T

1

HOLD/HLDA Timing

CLK

HOLD

HLDA

HOLD state: the P releases the Address,

Data, Control and Status buses (these pins

are tri-sated (high impedance)

only after ending the current bus cycle

CLK

INTA

AD

0

- AD

7

T

2

T

3

T

4

T

1

INT type

Tri-state

Minmode Interrupt acknowledge timing

a single INTA cycle in minmode.

CLK

LOCK

INTA

AD

0

- AD

7

T

2

T

3

T

4

T

1

T

2

T

3

T

4

T

1

INT type

First INTA cycle Second INTA cycle

Tri-state

Maxmode Interrupt acknowledge timing

two INTA cycles in maxmode, the device

requesting INT has to drive the INT type

on the Data Bus, during the second cycle.

Prevents P to enter a HOLD state

10.7 Personal Computer Bus Standards

CPU

Memory Bus

Cash

Memory

Memory

Controller

P Bus

Main

Memory

I/O Bus

Controller

Plug-in I/O

Boards

I/O Bus

Motherboard

I/O Circuits

CPU

Memory

I/O

P Bus

CPU

Cash

Memory

P Bus

Memory Bus

Memory

Controller

Main

Memory

Bridge

Controller

Motherboard- and Fast

Plug-in I/O Circuits

PCI Bus

I/O Bus

Controller

I/O Bus

Slow Plug-in

I/O Boards

Simple P System

Architecture

PCI (Peripheral Component Interconnect bus)

based Architecture

Medium Complexity PC Architecture

- ISA = Industry Standard

Architecture (8 data bits =

PC-XT bus, or 16 data bits

= PC-AT bus)

- EISA = Extended ISA

- MCA = Micro Channel

Architecture (only IBM)

4-33

Dual Independent Bus (DIB)

Backside Bus

Frontside Bus

4-34

Different level of Busses

Вам также может понравиться

- Hardware Detail of Intel 8088: Dr. Esam Al - Qaralleh CE Department Princess Sumaya University For TechnologyДокумент34 страницыHardware Detail of Intel 8088: Dr. Esam Al - Qaralleh CE Department Princess Sumaya University For TechnologykundanambreОценок пока нет

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142От EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142Оценок пока нет

- Microprocessor 8086 ArchitectureДокумент36 страницMicroprocessor 8086 ArchitectureBalakrishnan RamaswamyОценок пока нет

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationОт EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationОценок пока нет

- 8086/88 Device SpecificationsДокумент22 страницы8086/88 Device SpecificationsAyush PurohitОценок пока нет

- Intel 8086/8088 Microprocessor Minimum and Maximum Mode OperationДокумент61 страницаIntel 8086/8088 Microprocessor Minimum and Maximum Mode Operationkshtgarg21Оценок пока нет

- Microprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureОт EverandMicroprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureРейтинг: 1 из 5 звезд1/5 (1)

- 8XC52/54/58/80C32 8xc51fa/fb/fc/80c51fa 8xc51ra+/rb+/rc+/rd+/80c51ra +Документ56 страниц8XC52/54/58/80C32 8xc51fa/fb/fc/80c51fa 8xc51ra+/rb+/rc+/rd+/80c51ra +lukeskyОценок пока нет

- Part 1Документ30 страницPart 1ady63100% (1)

- 8051 Microcontroller With RF ModuleДокумент56 страниц8051 Microcontroller With RF Moduleashrafuli_44Оценок пока нет

- Exploring Arduino: Tools and Techniques for Engineering WizardryОт EverandExploring Arduino: Tools and Techniques for Engineering WizardryРейтинг: 4.5 из 5 звезд4.5/5 (5)

- 8086/8088 Hardware Specifications: CEN433 King Saud University Dr. Mohammed Amer ArafahДокумент69 страниц8086/8088 Hardware Specifications: CEN433 King Saud University Dr. Mohammed Amer ArafahHarold Carlos Ureña HerreraОценок пока нет

- Multicore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCОт EverandMulticore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCОценок пока нет

- Min Max ModeДокумент37 страницMin Max ModerajОценок пока нет

- Department of Technical Education Andhra Pradesh: 9CM405.7TO8 1 1Документ19 страницDepartment of Technical Education Andhra Pradesh: 9CM405.7TO8 1 1Y. S.V.Ramana raoОценок пока нет

- 8085 MicroprocessorДокумент16 страниц8085 MicroprocessorVinay FelixОценок пока нет

- Enhanced 8-Bit Microcontroller With 32 KB Flash Memory: AT89C51AC2 T89C51AC2Документ121 страницаEnhanced 8-Bit Microcontroller With 32 KB Flash Memory: AT89C51AC2 T89C51AC2mukhi2006Оценок пока нет

- Keyboad Controller para PC IBMДокумент15 страницKeyboad Controller para PC IBMMICROMATICA1Оценок пока нет

- PIC - New - Part 1 PIC Microcontroller Systems PDFДокумент5 страницPIC - New - Part 1 PIC Microcontroller Systems PDFLam Nguyen100% (1)

- 8086/88 Hardware and Bus StructureДокумент27 страниц8086/88 Hardware and Bus StructuredilipsugadevОценок пока нет

- COE305 Chapter 9Документ55 страницCOE305 Chapter 9Rajesh TiwaryОценок пока нет

- 10CS45 MP Unit6 ImpДокумент60 страниц10CS45 MP Unit6 ImpsupriyaОценок пока нет

- RTL 8186Документ50 страницRTL 8186Maria Alejandra DalcolmoОценок пока нет

- At89s8253 24jiДокумент56 страницAt89s8253 24jiAnghelescu CristinaОценок пока нет

- 20 سؤال معماريةДокумент23 страницы20 سؤال معماريةمصطفى شاكر محمودОценок пока нет

- Hardware Architecture of 8086 and 8088 MicroprocessorsДокумент9 страницHardware Architecture of 8086 and 8088 MicroprocessorsGizmoSX100% (1)

- ALDEC 16450 IP Core Data Sheet: Table 1: Core Signal PinoutДокумент4 страницыALDEC 16450 IP Core Data Sheet: Table 1: Core Signal PinoutDeepa DevarajОценок пока нет

- Two-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64AДокумент22 страницыTwo-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ASergioОценок пока нет

- At91sam7s64 DsДокумент491 страницаAt91sam7s64 DsLord_JoelОценок пока нет

- 2 Advanced+MicroprocesorДокумент66 страниц2 Advanced+MicroprocesorMilind KhanderaoОценок пока нет

- 8284 Clock Generator: Asawari Dudwadkar Dept. of Electronics VESIT, MumbaiДокумент14 страниц8284 Clock Generator: Asawari Dudwadkar Dept. of Electronics VESIT, MumbaiAsawari Dudwadkar100% (1)

- D D D D D: DescriptionДокумент39 страницD D D D D: DescriptionAnonymous o4taPXTPLОценок пока нет

- Part1 8088 PDFДокумент69 страницPart1 8088 PDFkingkonghuОценок пока нет

- EE6502 MPMC Two Marks With AnswerДокумент10 страницEE6502 MPMC Two Marks With Answervlsimani9110100% (1)

- 80C88Документ32 страницы80C88Alan AlvarezОценок пока нет

- Seminar PresentationДокумент24 страницыSeminar Presentationankyt807Оценок пока нет

- The 8051 Microcontroller: Lets EXPLORE Inside 8051 !!Документ45 страницThe 8051 Microcontroller: Lets EXPLORE Inside 8051 !!ZuricHuntОценок пока нет

- ET4508 p2Документ60 страницET4508 p2Jitha Kt0% (1)

- Berry B Brey Part IДокумент49 страницBerry B Brey Part Ikalpesh_chandakОценок пока нет

- 8282,8286,8284Документ23 страницы8282,8286,8284Relan Soniia100% (1)

- Sigals 8086Документ31 страницаSigals 8086RajaRaman.GОценок пока нет

- 8086 8088 MicroprocessorДокумент60 страниц8086 8088 MicroprocessorZain ChaudhryОценок пока нет

- TD - Datasheet TK400 NDДокумент4 страницыTD - Datasheet TK400 NDSocaciu VioricaОценок пока нет

- MSP430C11x1, MSP430F11x1A Mixed Signal Microcontroller: DescriptionДокумент43 страницыMSP430C11x1, MSP430F11x1A Mixed Signal Microcontroller: DescriptionHaks HaxОценок пока нет

- DLA001Документ36 страницDLA001Rogerio GuimarãesОценок пока нет

- Microcontroller 8051Документ42 страницыMicrocontroller 8051om18sahuОценок пока нет

- Microprocessor and Its ApplicationsДокумент25 страницMicroprocessor and Its ApplicationsAbhishek SinghОценок пока нет

- 80C51 8-Bit Microcontroller Family: 4K/128 Otp/Rom/Romless, 8 Channel 8 Bit A/D, Watchdog TimerДокумент28 страниц80C51 8-Bit Microcontroller Family: 4K/128 Otp/Rom/Romless, 8 Channel 8 Bit A/D, Watchdog Timerchecker0815Оценок пока нет

- 2-Wire Serial EEPROM: FeaturesДокумент23 страницы2-Wire Serial EEPROM: FeaturesgillupilluОценок пока нет

- Microprocessor and Its ApplicationsДокумент24 страницыMicroprocessor and Its Applicationssuperkan619Оценок пока нет

- 24 LC 16Документ12 страниц24 LC 16Sebastian QuaroneОценок пока нет

- 8051 Microcontroller RAM I/O Port Timer Serial FeaturesДокумент41 страница8051 Microcontroller RAM I/O Port Timer Serial FeaturesSringaSyamОценок пока нет

- 24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsДокумент12 страниц24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsBoris PopovОценок пока нет

- An Efficient Monitering of Substation Using RF: Voltage Current TemperatureДокумент38 страницAn Efficient Monitering of Substation Using RF: Voltage Current TemperatureVamshi Kumar Reddy MОценок пока нет

- AT89LP6440Документ200 страницAT89LP6440cmbataginiОценок пока нет

- Tsa5512 CNV 3Документ21 страницаTsa5512 CNV 3soft4gsmОценок пока нет

- Setting A Good Question PaperДокумент5 страницSetting A Good Question PaperchandrasekarОценок пока нет

- Multiple CamScanner ScansДокумент17 страницMultiple CamScanner ScanschandrasekarОценок пока нет

- Microwave Engineering Using Microstrip Circuits (Fooks)Документ175 страницMicrowave Engineering Using Microstrip Circuits (Fooks)Ali O Reza100% (1)

- CH 04Документ28 страницCH 04HassanОценок пока нет

- Gems of North East Darjeeling GangtokДокумент8 страницGems of North East Darjeeling GangtokchandrasekarОценок пока нет

- History of The Internet: Weesan LeeДокумент38 страницHistory of The Internet: Weesan LeeSimeony SimeОценок пока нет

- NIT AP Non Teaching Application Form-250917Документ5 страницNIT AP Non Teaching Application Form-250917vractivaОценок пока нет

- ExДокумент1 страницаExchandrasekarОценок пока нет

- ADC ProgДокумент2 страницыADC ProgchandrasekarОценок пока нет

- Oscillators For Microcontrollers: June 1983Документ40 страницOscillators For Microcontrollers: June 1983Pavankumar KalliОценок пока нет

- Case EVMДокумент2 страницыCase EVMchandrasekarОценок пока нет

- It 8051Документ3 страницыIt 8051appalaraju2010Оценок пока нет

- R305 User ManualДокумент26 страницR305 User ManualchandrasekarОценок пока нет

- Highway Alert Lamp - ProjectДокумент2 страницыHighway Alert Lamp - Projectchandrasekar75% (4)

- Stepper Motor Wire Color Codes by Manufacturer Anaheim AutomationДокумент2 страницыStepper Motor Wire Color Codes by Manufacturer Anaheim AutomationchandrasekarОценок пока нет

- MAX232Документ36 страницMAX232David Shure XivОценок пока нет

- Question Bank-Microprocessor and ApplicaionДокумент38 страницQuestion Bank-Microprocessor and Applicaionchandrasekar100% (5)

- MPДокумент1 страницаMPchandrasekarОценок пока нет

- Question Bank - Embedded SystemsДокумент24 страницыQuestion Bank - Embedded Systemschandrasekar100% (2)

- Microprocessor Answer KeyДокумент36 страницMicroprocessor Answer KeychandrasekarОценок пока нет

- 8 DtekДокумент5 страниц8 DtekAlexander WieseОценок пока нет

- Literature Review of Electric Arc Welding MachineДокумент4 страницыLiterature Review of Electric Arc Welding MachineafmzxutkxdkdamОценок пока нет

- C&MI - Lecture 1Документ12 страницC&MI - Lecture 1Mourougapragash Subramanian0% (1)

- Benefits of Preventive Maintenance PDFДокумент19 страницBenefits of Preventive Maintenance PDFGlendonОценок пока нет

- Basic Radio HandlingДокумент26 страницBasic Radio HandlingVlademir Geb Dubouzet100% (1)

- E&I InterfaceДокумент21 страницаE&I Interfacechandakbera100% (2)

- Trane Condensing UnitДокумент16 страницTrane Condensing Unitahmed abdelghanyОценок пока нет

- NEMA23 Closed Loop Stepper MotorДокумент3 страницыNEMA23 Closed Loop Stepper MotorGaurav MahajanОценок пока нет

- Introduction to PLC Programming LanguagesДокумент17 страницIntroduction to PLC Programming LanguagesBandi vennelaОценок пока нет

- Guideline For Typical Appliance Ratings To Assist in Sizing of PV Solar SystemsДокумент8 страницGuideline For Typical Appliance Ratings To Assist in Sizing of PV Solar SystemspriteshjОценок пока нет

- S6 Sub Maths SBДокумент186 страницS6 Sub Maths SBFlorence UfituweОценок пока нет

- Technical service manual EM 9980 Code 4-117248AДокумент48 страницTechnical service manual EM 9980 Code 4-117248AIrimia MarianОценок пока нет

- Calibration of Thrmocouples: Assignment # 01Документ3 страницыCalibration of Thrmocouples: Assignment # 01ahmadОценок пока нет

- Pid Controller Tuning in SimulinkДокумент7 страницPid Controller Tuning in SimulinkRicael SpirandeliОценок пока нет

- Description and Classification of Electromagnetic Environments - Revision of IEC 61000-2-5Документ5 страницDescription and Classification of Electromagnetic Environments - Revision of IEC 61000-2-5AAAAAОценок пока нет

- Nature of Electrical Supply CharacteristicsДокумент27 страницNature of Electrical Supply CharacteristicsDrPrashant M. MenghalОценок пока нет

- Marsh Brown Clr-BrochureДокумент4 страницыMarsh Brown Clr-BrochureأبوإسلامОценок пока нет

- Bfou1kv (3) Nek606 CablesДокумент14 страницBfou1kv (3) Nek606 Cables54045114Оценок пока нет

- Installation, Operation & Maintenance Instructions For Abtech S' Range Enclosures Cml15Atex3078U and Iecex CML 15.0039UДокумент2 страницыInstallation, Operation & Maintenance Instructions For Abtech S' Range Enclosures Cml15Atex3078U and Iecex CML 15.0039USantoshkumar GurmeОценок пока нет

- Casio CTK-2000 Service Manual and Parts ListДокумент27 страницCasio CTK-2000 Service Manual and Parts ListEngkiong Go100% (3)

- An3095 Stevalisv002v1 Stevalisv002v2 3 KW Gridconnected PV System Based On The Stm32f103xx StmicroelectronicsДокумент55 страницAn3095 Stevalisv002v1 Stevalisv002v2 3 KW Gridconnected PV System Based On The Stm32f103xx StmicroelectronicsAhmar Hayat KhanОценок пока нет

- Atomic Structure - DPP-02 II NEET Ultimate CC 2023Документ4 страницыAtomic Structure - DPP-02 II NEET Ultimate CC 2023vijaylakshmi0727Оценок пока нет

- Fundamentals of Electrical Drives SystemsДокумент14 страницFundamentals of Electrical Drives SystemsyaredОценок пока нет

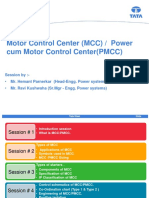

- 1 - PPT For MCC For Aets 2017Документ50 страниц1 - PPT For MCC For Aets 2017Harleen KaurОценок пока нет

- Schematic Circuits: Section C - ElectricsДокумент1 страницаSchematic Circuits: Section C - ElectricsIonut GrozaОценок пока нет

- VLSI Quiz QuestionsДокумент17 страницVLSI Quiz Questionsjitu_40% (1)

- RADWIN System DescriptionДокумент28 страницRADWIN System Descriptiontho2007100% (1)

- Philips LED 12836redb1 21 Watts 5 Watts 21w/5w Dois PolosДокумент2 страницыPhilips LED 12836redb1 21 Watts 5 Watts 21w/5w Dois PolosExclusivo1Оценок пока нет

- Chapter 10 - MLSДокумент8 страницChapter 10 - MLSEl Shazly SaidОценок пока нет

- Service Manual TV Lg42px4rvh EnglishДокумент37 страницService Manual TV Lg42px4rvh EnglishRc Uno UnoОценок пока нет