Академический Документы

Профессиональный Документы

Культура Документы

Interface

Загружено:

biotech_vidhya0 оценок0% нашли этот документ полезным (0 голосов)

56 просмотров41 страницаscience

Авторское право

© © All Rights Reserved

Доступные форматы

PPT, PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документscience

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PPT, PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

56 просмотров41 страницаInterface

Загружено:

biotech_vidhyascience

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PPT, PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 41

Real-Time Embedded Systems

Khalid Abu Muhaimeed

Nouh Kh.Toolitch

Supervisor: Dr.Lo`ai Tawalbeh

Real-time Embedded Systems/Interfacing 2

Outline

Interfacing basics.

Microprocessor interfacing

I/O addressing.

Interrupts.

Direct Memory Access (DMA).

Real-time Embedded Systems/Interfacing 3

Introduction

Processor process data.

memory storage

buses communication

Communication: transfer of data among

processors and memories.

This communication is known as interfacing.

Real-time Embedded Systems/Interfacing 4

Basic Terminology

unidirectional (rd/wr , enable)

Wires

bidirectional (data)

A set of wires with the same function :

a set of wires with a single function (data bus).

Bus

entire wires collection along with their communication protocol.

Protocol: rules for communicating over the wires. (low level HW protocols)

bus structure

Processor Memory

rd'/wr

enable

addr[0-11]

data[0-7]

bus

Real-time Embedded Systems/Interfacing 5

Basic Terminology

Port: the actual conducting device (metal) on the processor (or

memory) through which the signal is input to, or output from.

We could use the term pin to refer to a port on a processor.

Pin is also a term referring to the extending pins from the processor (

as own IC package). They are designed to be plugged into a socket on a

printed-circuit board.

Small metallic balls could be used rather than pins( if the processor

is packaged in its own IC ).

If the processor coexists on a single IC with other processors and

memories, pads of metal are used in the IC.

Real-time Embedded Systems/Interfacing 6

Timing diagram

It is the most common method for describing a HW protocol.

Time proceeds to the right along the x-axis.

Control lines high or low.

Data lines (addr, data) invalid (one horizontal line) or valid (two horizontal lines).

The processor must place the address on addr for at least tsetup time before setting

the enable high.

The high enable line triggers the memory to put data on the data wires after tread

time.

When line is active (high, or commonly low) , it triggers the data transfer.

Assert means setting control line to its active value.

Deassert means setting control line to its low value.

A protocol could be consisted of subprotocols (i.e. read, write), known as

transaction or a bus cycle. A bus cycle may consists of several clock cycles.

read protocol

rd'/wr

enable

addr

data

t

setup

t

read

write protocol

rd'/wr

enable

addr

data

t

setup

t

write

Real-time Embedded Systems/Interfacing 7

Basic protocol concepts

Actor: is the processor or memory involved in data transfer.

A protocol involves two actors: a master, and a servant (slave).

A master initiates the data transfer (usually general-purpose

processor), and the servant responds to the initiation request

(usually memories and peripherals).

Data direction: the direction that the transferred data moves btw.

actors( receiving or sending data).

Addresses: a special type of data used to indicate where regular

data should go to or come from (used to address memory locations ,

peripherals and peripheral's registers).

Real-time Embedded Systems/Interfacing 8

Time multiplexing

Share a single set of wires for multiple pieces of data.

Saves wires at expense of time.

data serializing address/data muxing

Master Servant

req

data(8)

data(15:0) data(15:0)

mux demux

Master Servant

req

addr/data

req

addr/data

addr data

mux demux

addr data

req

data 15:8

7:0

addr data

Time-multiplexed data transfer

Real-time Embedded Systems/Interfacing 9

Control methods :strobe and handshake

A handshake protocol can adjust to a servant with varying response times,

but it could be slower, and need extra clock cycles and extra line.

Strobe protocol

Handshake protocol

Master Servant

req

ack

req

data

Master Servant

data

req

data

t

access

req

data

ack

1. Master asserts req to receive data

2. Servant puts data on bus within time t

access

1

2

3

4

3. Master receives data and deasserts req

4. Servant ready for next request

1

2

3

4

1. Master asserts req to receive data

2. Servant puts data on bus and asserts ack

3. Master receives data and deasserts req

4. Servant ready for next request

Real-time Embedded Systems/Interfacing 10

Control methods :strobe / handshake

compromise

It achieves both the speed of strobe protocol, and the varying response time

tolerance of a handshake protocol.

The handshake only occurs if it necessary.

Fast-response case

req

data

wait

1 3

4

1. Master asserts req to receive data

2. Servant puts data on bus within time t

access

3. Master receives data and deasserts req

4. Servant ready for next request

2

Slow-response case

Master Servant

req

wait

data

req

data

wait

1

3

4

1. Master asserts req to receive data

2. Servant can't put data within t

access

, asserts wait ack

3. Servant puts data on bus and deasserts wait

4. Master receives data and deasserts req

2

t

access

t

access

5. Servant ready for next request

5

(wait line is unused)

Real-time Embedded Systems/Interfacing 11

The ISA bus protocol Memory Access

ISA: The Industry Standard

Architecture.

80x86 microprocessor.

20 bit memory address.

ALE: Address Latch Enable.

CHRDY: Channel Ready.

Compromise strobe/handshake

control method is used.

The memory deasserted

CHRDY before the rising clock

edge in C2, causing the

microprocessor to insert wait

cycles (up to 6 cycles) until CHRDY was reasserted.

Microprocessor

Memory I/O Device

ISA bus

ADDRESS

CYCLE

CLOCK

D[7-0]

A[19-0]

ALE

/MEMR

CHRDY

C1 C2 WAIT C3

C4

DATA

CYCLE

CLOCK

D[7-0]

A[19-0]

ALE

/MEMW

CHRDY

C1 C2 WAIT C3

C4

DATA

ADDRESS

Real-time Embedded Systems/Interfacing 12

Microprocessor interfacing: I/O addressing

The microprocessor's pins used to communicate data to

and from it, are called I/O pins.

We normally consider the access to peripherals (not

memory), as I/O.

Two common methods for using pins to support I/O : Port-

based I/O (Parallel I/O), and Bus-based I/O.

In parallel I/O , a port can be directly read and written by

processor instructions, like any register.

Ex.P0=255, g=P2 .

Ports are often bit-addressable.

In bus-based I/O, the microprocessor has a set of address,

data, and control ports corresponding to bus lines, and uses

the bus to access memory and peripherals.

Real-time Embedded Systems/Interfacing 13

Extensions

Parallel I/O peripheral.

When processor only supports bus-based I/O

but parallel I/O needed.

Each port on peripheral connected to a register within

peripheral. The microprocessor can read/write those

registers.

Extended parallel I/O.

When processor supports port-based I/O

but more ports needed.

One or more processor ports interface with

parallel I/O peripheral extending total number

of ports available for I/O.

e.g., extending 4 ports to 6 ports in figure.

Processor Memory

Parallel I/O peripheral

Port A

System bus

Port C Port B

Adding parallel I/O to a bus-

based I/O processor

Processor

Parallel I/O peripheral

Port A Port B Port C

Port 0

Port 1

Port 2

Port 3

Extended parallel I/O

Real-time Embedded Systems/Interfacing 14

Memory-Mapped I/O and Standard I/O

They are two bus-based methods for microprocessor to communicate with

peripherals.

In memory-mapped I/O, peripherals occupy specific addresses in the existing

address space.

e.g., Bus has 16-bit address, lower 32K addresses may correspond to memory,

and upper 32k addresses may correspond to peripherals.

In standard I/O (I/O-mapped I/O), the bus includes an additional pin (M`/IO), to

include whether the access is to memory or peripheral.

e.g., Bus has 16-bit address, all of them for memory addressing if M`/IO=0, and

all of them for I/O addressing if M`/IO=1.

Real-time Embedded Systems/Interfacing 15

Memory-Mapped I/O Vs. Standard I/O

Memory-mapped I/O

Requires no special instructions

Assembly instructions involving memory like MOV and ADD

work with peripherals as well.

Standard I/O requires special instructions (e.g., IN, OUT) to

move data between peripheral registers and memory.

Standard I/O

No loss of memory addresses to peripherals.

Simpler address decoding logic in peripherals possible.

When number of peripherals much smaller than address

space then high-order address bits can be ignored

smaller and/or faster comparators.

Real-time Embedded Systems/Interfacing 16

ISA bus protocol

ISA bus protocol supports standard I/O.

The I/O address space is 16 bits, where it is 20 bits for

memory.

It uses compromise strobe/handshake control method.

similar to memory protocol except address space.

CYCLE

CLOCK

D[7-0]

A[15-0]

ALE

/IOR

CHRDY

C1 C2 WAIT C3 C4

DATA

ADDRESS

ISA I/O bus read protocol

Real-time Embedded Systems/Interfacing 17

A basic memory protocol

Interfacing an 8051 to external memory

Ports P0 and P2 support port-based I/O when 8051 internal

memory being used.

Those ports serve as data/address buses when external memory

is being used.

16-bit address and 8-bit data are time multiplexed; low 8-bits of

address must therefore be latched with aid of ALE signal.

8051

74373

P0

HM6264

D Q

8

P2

ALE

G

A<0...15>

D<0...7>

/OE

/WE

/CS

/WR

/RD

/CS1

/PSEN

CS2

27C256

/CS

A<0...14>

D<0...7>

/OE

P0

P2

Q

ALE

/RD

Adr. 7..0

Adr. 158

Adr. 70

Data

Real-time Embedded Systems/Interfacing 18

A complex memory protocol

Generates control signals to drive the TC55V2325FF memory chip in burst mode.

Addr0 is the starting address input to device.

GO is enable/disable input to device.

ADSP=1,

ADSC=1

ADV=1, OE=1,

Addr = Z

ADSP=1,

ADSC=0

ADV=1, OE=1,

Addr = Z

ADSP=1,

ADSC=1

ADV=0, OE=0,

Addr = Z

GO=1

GO=0

Data is

ready

here!

GO=1

GO=1

GO=0

GO=0

S0 S1

S2 S3

ADSP=0,

ADSC=0

ADV=0, OE=1,

Addr = Addr0

GO=0

GO=1

FSM description

Specification for a single

read operation

CLK

/ADSP

/ADSC

/ADV

addr <150>

/WE

/OE

/CS1 and /CS2

CS3

data<310>

Interrupts (interrupt driven I/O)

Servicing: read & process data from peripheral whenever it

has new data.

Unpredictable

Polling: MP repeatedly check for data

Simple to implement

Waste many clock cycles

External interrupts

Repeatedly MP checks Int pin after executing instruction, if

asserted => jump to ISR

Pin polling?

Into MP, done simultaneously with the exec. of Instr.

Maskable vs Nonmaskable Interrupt

Internal Interrupt (divide by 0,)

Software Interrupt .

Real-time Embedded Systems/Interfacing 19

Interrupt Addressing

Fixed Int.: ISR address built in MP

Vectored Int.:

ISR address requested from peripherals by Inta pin

asserted by MP.

The address stored in peripheral by extra register.

Interrupt Address Table (compromise between

fixed & vectored)

Table holds ISR addresses

Peripherals provide entry number instead.

Real-time Embedded Systems/Interfacing 20

Fixed Int.

1. MP is executing its main program.

2. Peripheral_1 receives input data in a register

and assert Int to request servicing.

3. After completing Instr. Execution, MP detect Int

, saves current PC value and set PC = ISR

fixed address.

4. ISR reads Peripheral_1 data & processed it,

then deasserts Int.

5. ISR return, restoring PC and MP resume

execution.

Real-time Embedded Systems/Interfacing 21

Vectored Int.

Real-time Embedded Systems/Interfacing 22

P

P1

System bus

0x8000

16: MOV R0, 0x8000

17: # modifies R0

18: MOV 0x8001, R0

19:

RETI # ISR return

ISR

100:

101:

instruction

instruction

...

Main program

...

Program memory

PC

DMA

Buffering: temporary storage of data that is

awaiting processing.

Using Interrupt:

Storing & restoring MP states => consuming

many clock cycles (inefficient)

No execution during data moving.

I/O of DMA: separate single-purpose

processor (DMA controller).

Purpose: transfer data between memories and

peripherals

Real-time Embedded Systems/Interfacing 23

DMA flow of actions

1. MP is executing its main program. It has already configured the

DMA ctrl registers.

2. Peripheral_1 receives input data in a register, and asserts req

to request servicing by DMA ctrl.

3. DMA ctrl asserts Dreq to request control of system bus.

4. After executing instruction, MP sees Dreq asserted, releases

the system bus, asserts Dack, and resumes execution. MP

stalls only if it needs the system bus to continue executing.

5. DMA ctrl asserts ack reads data and (b) writes that data to

memory.

6. DMA de-asserts Dreq and ack completing handshake with

Peripheral_1.

7. MP de-asserts Dack and resumes control of the bus.

8. Peripheral_1 de-asserts req.

Real-time Embedded Systems/Interfacing 24

DMA flow of actions (cont.)

Real-time Embedded Systems/Interfacing 25

DMA ctrl P1

0x8000

101

:

instruction

instruction

...

...

Program

memory

PC

100

Dreq

Dack

0x000

0

0x0001

100:

needed!

0x0001

0x8000

ack

req

Arbitration

Multiple peripherals request service

simultaneously from single MP or single

DMA

Arbitration: decide which one get services.

Priority Arbiter.

Daisy-Chain Arbitration.

Network-Oriented Arbitration Methods.

Real-time Embedded Systems/Interfacing 26

Arbitration Priority Arbiter

Is a single-purpose processor

2 schemes to determine priority among peripherals:

Fixed priority: unique rank for each peripheral. Arbiter

choose the higher rank.

Rotating priority (round-robin): based on history of

servicing (e.g. least recently serviced)

More equitable of servicing.

Real-time Embedded Systems/Interfacing

27

MP

Priority

arbiter

Peripheral1

System bus

Int

3

5

7

Inta

Peripheral2

Ireq1

Iack2

Iack1

Ireq2

2

2

6

Vectored Interrupt

Arbitration Daisy-Chain Arbitration

Peripherals connected as a chain

Each peripheral has: req. output, ack. input, req. input, and ack. Output

Add or remove peripherals without redesigning the system

Peripherals at the end of chain could become intolerably slow.

Isnt supporting more advanced priority schemes

If one peripheral stop, the other lose access

Each peripheral must be daisy-chain aware

Otherwise, external logic is used.

Real-time Embedded Systems/Interfacing 28

P

System bus

Int

Inta

Peripheral1

Ack_in Ack_out

Req_out Req_in

Peripheral2

Ack_in Ack_out

Req_out

Req_in 0

Arbitration Network-Oriented

Multiple MP connected by a shared bus

(network).

Arbitration among processors.

Typically built right into the bus protocol

The protocol must ensure that no contending

processors sending at the same time

Examples: I2C, Ethernet, CAN

Real-time Embedded Systems/Interfacing 29

I

Multilevel Bus Architectures

Numerous type of communications:

Most frequent and high speed (between MPs).

Less frequent and low speed (between MP and Peripherals

like UART)

Single high speed bus:

Required each peripheral to have high-speed bus interface

Extra gates ,Power consumption and cost.

May not be very portable.

May result in slower bus.

2 level buses:

Processor local bus: connects MP, cache, memory

controllers

Peripheral bus: ISA, PCI

emphasize portability, low power or low gate count.

Bridge (single-purpose processor) connect two bus levels

Real-time Embedded Systems/Interfacing 30

Multilevel Bus Architectures cont.

2 level buses: VSI Alliance.

Processor local bus

System bus

Peripheral bus

Real-time Embedded Systems/Interfacing 31

Processor-local bus

Micro-

processor

Cache Memory

controller

DMA

controller

Bridge Peripheral Peripheral Peripheral

Peripheral bus

Advanced Communication

Principles

Physical layer: the medium that is used to carry

data from one device to another.

Single wire, a set of wires, radio waves, or infrared

waves.

Parallel communication

Serial Communication

Wireless Communication

Real-time Embedded Systems/Interfacing 32

Parallel communication

Multiple data wires + control and possibly power

wires.

Each wire carries one of the bits.

High data throughput, if the length is short.

Long parallel wires:

High capacitance values => more time to charge or

discharge

Misalignment.

Costly to construct.

May be bulky

In general, used when connect devices reside on the

same IC or circuit board.

Real-time Embedded Systems/Interfacing 33

Parallel Protocols

PCI (Peripheral Component Interconnect)

Originated at Intel 1990 and then administered by PCISIG

First used in 1994

For interconnecting chips, expansion boards, & processor memory

subsystem.

Replaced ISA/EISA bus

Transfer rate: 127.2 508.6 Mbit/s

32-bit addressing later extended to 64-bit

Sync bus architecture

ARM

Designed by ARM Corporation

Designed to interface with ARM line of processors.

32 data/address

Sync data architecture

Transfer rate not specified (function of the clock speed)

Real-time Embedded Systems/Interfacing 34

Serial communication

Single data wire, along with control & possibly power

Higher throughput than parallel when connect distant

devices

Less average capacitance.

Cheaper to build

More complex interfacing logic & communication

protocols (compose & decompose data)

Most protocols use same wire for control

Start bit

Stop bit

May use additional wire for clocking purpose as sync tech.

Real-time Embedded Systems/Interfacing 35

Serial Protocols

I2C (Inter-IC)

Developed by Philips Semiconductors

2 wire bus protocol

Connect peripheral ICs in electronic systems

Transfer rate: up to 100 kbit/s, 7-bit address

Fast mode: 3.4 Mbit/s, 10-bit address

Flash, RAM, EPROM, Microcontrollers

CAN (Controller Area Network)

For real-time application

Developed by Robert Bosch GmbH to connect various components of car

Over twisted pair of wires

High integrated serial data communication

Data rate up to 1 Mbit/s

11-bit addressing

Documented in ISO 11898 & ISO 11519-2

Common applications: Automobiles, elevator controllers, copiers,

telescopes,

Real-time Embedded Systems/Interfacing 36

Serial Protocols

FireWire (I-Link or Lynx)

Developed by Apple Computer Inc.

Specification is given by IEEE 1394

Mass information transfer

Transfer rate: 12.5 400 Mbit/s

64-bit addressing (64b net id, 6b node id, 48b mem addr)

Real-time connection and disconnect and assignment

(Plug and Play)

Designed for interfacing independent electronic devices.

USB (Universal Serial Bus)

Has 2 data rates: 12 Mb/s, 1.5 Mb/s

For PC users to connect monitors, printers, scanners,

Used tiered star topology (USB hubs)

Real-time Embedded Systems/Interfacing 37

Wireless communication

Physical layers:

IR

Relatively cheap

Need line of sight

Diode emits infrared light to generate signal, Infrared

transistor detects signal.

RF

Line of sight not necessary

Longer distance communications

Frequency hopping, to communicate while constantly

changing transmission frequency.

Real-time Embedded Systems/Interfacing 38

Wireless Protocols

IrDA (Infrared Data Association)

IrDA is an international organization

Designed to support transmission between two devices over short-range point-to-point

infrared.

Rate: 9.6 Kb/s 4 Mb/s

Deployed in notebooks, printers, PDAs, cell phones,

MS Windows CE 1.0 the first Windows OS support it

Available on several popular embedded OSs

Bluetooth

Use radio frequency

Within 10 meters

Doesnt require a line-of-sight connection

IEEE 802.11

IEEE proposed standard for WLAN

Ad-hoc vs. infrastructure

PHY and MAC layers

Data rate: 1Mbps, 2Mbps

Calls: 2.4 2.4835 GHz frequency band (unlicensed band).

Use CSMA/CA

Signals for transmission: RTS, CTS, and ACK.

Real-time Embedded Systems/Interfacing 39

Reference

Embedded system Design: A unified

Hardware/Software Introduction, Frank Vahid,

Tony Givarrgis, Wiley, 2002

Real-time Embedded Systems/Interfacing 40

Questions?

Real-time Embedded Systems/Interfacing 41

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Stripping For ReprobingДокумент2 страницыStripping For ReprobingStella SalvatoreОценок пока нет

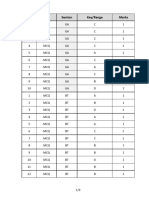

- Q.No. Type Section Key/Range MarksДокумент3 страницыQ.No. Type Section Key/Range Marksbiotech_vidhyaОценок пока нет

- Stripping For ReprobingДокумент2 страницыStripping For ReprobingStella SalvatoreОценок пока нет

- Facs ProtocolДокумент7 страницFacs ProtocolmisterxОценок пока нет

- Troubleshooting SDS-PAGE 1Документ3 страницыTroubleshooting SDS-PAGE 1biotech_vidhyaОценок пока нет

- BT 2019Документ13 страницBT 2019biotech_vidhyaОценок пока нет

- Buffer Preparation PDFДокумент6 страницBuffer Preparation PDFbiotech_vidhyaОценок пока нет

- Components Reaction MixtureДокумент3 страницыComponents Reaction Mixturebiotech_vidhyaОценок пока нет

- SDS PageДокумент2 страницыSDS Pagebiotech_vidhyaОценок пока нет

- Polymerase Chain Reaction (PCR)Документ3 страницыPolymerase Chain Reaction (PCR)biotech_vidhyaОценок пока нет

- Polymerasen GuideДокумент16 страницPolymerasen Guidebiotech_vidhyaОценок пока нет

- A.E. (Mechanical Engineering I) 2007Документ24 страницыA.E. (Mechanical Engineering I) 2007Mukesh KumarОценок пока нет

- Brad FordДокумент12 страницBrad FordQi ChaoОценок пока нет

- Buffer Preparation PDFДокумент6 страницBuffer Preparation PDFbiotech_vidhyaОценок пока нет

- Qpaper PondyДокумент21 страницаQpaper Pondybiotech_vidhyaОценок пока нет

- Whole Cell ExtractДокумент1 страницаWhole Cell Extractbiotech_vidhyaОценок пока нет

- Nuclear ExtractsДокумент2 страницыNuclear Extractsbiotech_vidhyaОценок пока нет

- Ies 17 Set A Me Q AДокумент67 страницIes 17 Set A Me Q Abiotech_vidhyaОценок пока нет

- TNPSC Group 1 Prelim Book List PDFДокумент2 страницыTNPSC Group 1 Prelim Book List PDFbiotech_vidhyaОценок пока нет

- TNPSC Group 1 Prelim Book List PDFДокумент2 страницыTNPSC Group 1 Prelim Book List PDFbiotech_vidhyaОценок пока нет

- Img Word-To PDFДокумент3 страницыImg Word-To PDFbiotech_vidhyaОценок пока нет

- TDC 41597 A (Mechanical Engg.) - 2012Документ20 страницTDC 41597 A (Mechanical Engg.) - 2012biotech_vidhyaОценок пока нет

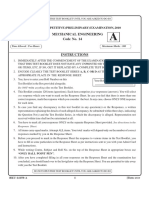

- Mechanical Engineering Code No. 14: Combined Competitive (Preliminary) Examination, 2010Документ20 страницMechanical Engineering Code No. 14: Combined Competitive (Preliminary) Examination, 2010biotech_vidhyaОценок пока нет

- TNPSC Group 1 Prelim Book List PDFДокумент2 страницыTNPSC Group 1 Prelim Book List PDFbiotech_vidhyaОценок пока нет

- Ese 2017 Prelims Mechanical Engineering Paper SolutionДокумент52 страницыEse 2017 Prelims Mechanical Engineering Paper SolutionpataОценок пока нет

- Qpaper PondyДокумент21 страницаQpaper Pondybiotech_vidhyaОценок пока нет

- Befcv List PDFДокумент22 страницыBefcv List PDFbiotech_vidhyaОценок пока нет

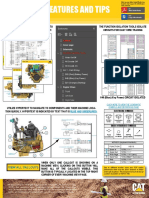

- Part and Mold Design GuideДокумент170 страницPart and Mold Design GuideminhtintinОценок пока нет

- Recruitment RulesДокумент5 страницRecruitment Rulesbiotech_vidhyaОценок пока нет

- 1 TolerancesДокумент1 страница1 Tolerancesbiotech_vidhyaОценок пока нет

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- EcoEnergy Catalogue 081110Документ68 страницEcoEnergy Catalogue 081110Hummingbird HgcОценок пока нет

- DatasheetДокумент4 страницыDatasheetGrupo EpufmОценок пока нет

- Installation Guide TRx4-500Документ71 страницаInstallation Guide TRx4-500Dmitry UОценок пока нет

- Project Report (Vending Machine)Документ9 страницProject Report (Vending Machine)Muhammad HamzaОценок пока нет

- Gate Triggering Ckts Resistance TriggeringДокумент6 страницGate Triggering Ckts Resistance TriggeringAkhilrajscribdОценок пока нет

- KABINBURI (Feed Mil) Floater SLD - Rev 11Документ1 страницаKABINBURI (Feed Mil) Floater SLD - Rev 11Selvam KesavanОценок пока нет

- Wistron GodzillaДокумент61 страницаWistron Godzillarodrigootavio5Оценок пока нет

- Wein Bridge Oscillators PresentationДокумент15 страницWein Bridge Oscillators PresentationHarish KumarОценок пока нет

- KC str25 Paper17Документ2 страницыKC str25 Paper17Hàari CóolОценок пока нет

- Solar Led TVДокумент2 страницыSolar Led TVAnonymous I13s99Оценок пока нет

- Electricity System For HospitalsДокумент14 страницElectricity System For HospitalsTejinderОценок пока нет

- Wireless Technology (Slide)Документ17 страницWireless Technology (Slide)Shafiq Mohd NorОценок пока нет

- Chowdhury 2017Документ11 страницChowdhury 2017bhatttanmayhОценок пока нет

- DigiLink Technical Catalogue 2011Документ44 страницыDigiLink Technical Catalogue 2011Anonymous gMgeQl1SndОценок пока нет

- P 3 U 30Документ120 страницP 3 U 30ArcoolОценок пока нет

- JW 5880200 GДокумент18 страницJW 5880200 GMahmoudYasienMashhourОценок пока нет

- CIPS-14-010 Perforation Safety English VersionДокумент18 страницCIPS-14-010 Perforation Safety English VersionecarcovaОценок пока нет

- Experiment 5 Eng NaderДокумент7 страницExperiment 5 Eng Naderياسر العويطيОценок пока нет

- Laser Light Cable (LLK-B) Spare Parts CatalogДокумент6 страницLaser Light Cable (LLK-B) Spare Parts CatalogBuentello B GonzalezОценок пока нет

- Example Pump Selection: Equipment Data SheetДокумент4 страницыExample Pump Selection: Equipment Data SheetMohamed Yassine LahianiОценок пока нет

- Nishikant Power System Internship Report Docs 1Документ23 страницыNishikant Power System Internship Report Docs 1Darshan PawarОценок пока нет

- September 04 2022 NEET UG Re Exam Combined Solution Code W6 1Документ46 страницSeptember 04 2022 NEET UG Re Exam Combined Solution Code W6 1Bishal ChowdhuryОценок пока нет

- Lecture Notes 17 - Electrical Safety of Medical EquipmentДокумент4 страницыLecture Notes 17 - Electrical Safety of Medical Equipmentnramanathan1Оценок пока нет

- 1 Component Surface Mount Technology (SMT) : Intel® Manufacturing Enabling Guide May 2010Документ23 страницы1 Component Surface Mount Technology (SMT) : Intel® Manufacturing Enabling Guide May 2010Marco TassiОценок пока нет

- 25-Tap Differentiator Using Rectangular, Bartlett and Hamming Window EX - NO: DateДокумент6 страниц25-Tap Differentiator Using Rectangular, Bartlett and Hamming Window EX - NO: DateSaresh KumarОценок пока нет

- DATA LOGGER Trouble ShootingДокумент74 страницыDATA LOGGER Trouble ShootingGhyliving GhyОценок пока нет

- I O Summary For BMSДокумент2 страницыI O Summary For BMSN Faathimaa Shabrina67% (3)

- Huawei GSM Bts3900 Hardware Structure-20080728-Issue4.0Документ64 страницыHuawei GSM Bts3900 Hardware Structure-20080728-Issue4.0Agung WibawaОценок пока нет

- Multi-Parameter Monitoring & Controlling For A Boiler Using PIC ControllerДокумент1 страницаMulti-Parameter Monitoring & Controlling For A Boiler Using PIC ControllerkmkesavanОценок пока нет

- Re NR 67370001Документ7 страницRe NR 67370001Mauro PerezОценок пока нет