Академический Документы

Профессиональный Документы

Культура Документы

Flip-Flops, Registers, Counters, and A Simple Processor

Загружено:

suprianto0 оценок0% нашли этот документ полезным (0 голосов)

62 просмотров33 страницыYyyy

Оригинальное название

Latch

Авторское право

© © All Rights Reserved

Доступные форматы

PPTX, PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документYyyy

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PPTX, PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

62 просмотров33 страницыFlip-Flops, Registers, Counters, and A Simple Processor

Загружено:

supriantoYyyy

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PPTX, PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 33

Chapter 7

Flip-Flops, Registers, Counters, and A Simple Processor

Chapter Objectives

• In this chapter you will learn about:

• Logic circuits that can store information

• Flip-flops, which store a single bit

• Registers, which store multiple bits

• Shift registers, which shift the contents of the register

• Counters of various types

LATCH

Introduction

• In previous chapters we considered combinatorial circuits where the

value of each output depends solely on the values of signal applied to

the inputs.

Combinatorial Circuit Example

Introduction

• There exists another class of logic circuits in which the value of the

outputs depend not only on the input, but also on the past behavior

of the circuit.

• This circuits include storage elements ( the contents of this storage

element are said to represent the state of the circuit)

Introduction…

• When the circuit’s input change values, the new input values either

leave the circuit in the same state or cause it to change into a new

state.

• Overtime the circuit changes through a sequence of states as a result

of changes in the inputs (This is called sequential circuits).

Source : https://www.youtube.com/watch?v=EGnXSzPV_M8

Source : https://www.electronicproducts.com/uploadedImages/Education/Design/fajb_laser_tripwire_01_jun2016.jpg

Control of an Alarm System

Control of an Alarm System

A simple memory element

Made by two inverter

Yet its not useful because it lacks some practical

means for changing it’s state…

BASIC LATCH

LATCH

• The basic element for storing information

• One latch can store 1 bit of information

The same circuit with different

arrangement

Timing diagram for the basic latch with NOR gates

GATED SR LATCH

Introduction

• It will be better if we can control the input of Basic Latch or SR Latch,

either by enabling or disabling the input for any given time.

GATED SR LATCH

GATED SR LATCH

GATED SR LATCH WITH NAND

GATES

GATED D LATCH

Introduction

• Compared to Gated SR Latch, Gated D Latch won’t have an oscillatory

output.

• Gated D Latch function as an input storage when Clk is enabled (we

can think of the sum in half-adder that will be used in subsequent

calculation).

Gated D Latch

Gated D Latch

Effects of Propagation Delay

• In the previous discussion we ignored the effects of propagation

delays.

• In practical circuits it is essential to take these delays into account.

Effects of Propagation Delay…

Ideal Timing Diagram, no propagation delay.

Effects of Propagation Delay…

• At the time clock goes from 1 to 0, the circuit will still function

properly if the signal D remain stable during the transition.

• An unpredictable result may occur if the D signal also changes at the

time where Clk changes from 1 to 0.

• Therefore, the designer of a logic circuit that generates the D signal

must ensure that this signal is stable when the critical change in the

cock signal takes place.

Effects of Propagation Delay…

• The minimum time that the D signal must be stable prior to the

negative edge of the Clk signal is called the setup time, of the latch

• The minimum time that the D signal must remain stable after the

negative edge of the Clk signall is called the hold time, of the latch

Effects of Propagation Delay…

Setup and hold time

Effects of Propagation Delay…

• The values of and depend on the technology used.

• Manufacturers of integrated circuit chips provide this information on

the data sheets that describe their chips.

• Typical values for a modern CMOS technology may be and

Вам также может понравиться

- Ecoders and Decoders ICT ReportДокумент36 страницEcoders and Decoders ICT Reportneygar69Оценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- DSD Module5 Sequential Part1 PDFДокумент94 страницыDSD Module5 Sequential Part1 PDFAvi Aaryan JeetОценок пока нет

- UNIT 1 Lecture 3Документ69 страницUNIT 1 Lecture 3Peaceful SoulОценок пока нет

- Unit 1 3Документ30 страницUnit 1 3Prabhav NandanОценок пока нет

- Power Gating Implementation in SOCДокумент23 страницыPower Gating Implementation in SOCmaxxtorr723Оценок пока нет

- Chapter 5 - Slides - Part - IДокумент23 страницыChapter 5 - Slides - Part - IKarimovaRaikhanovnaОценок пока нет

- Clock GenerationДокумент45 страницClock GenerationMoin PashaОценок пока нет

- DFT Interview Questions & AnswersДокумент22 страницыDFT Interview Questions & Answersdeepa100% (4)

- Difference Between A Latch and A Flip FlopДокумент2 страницыDifference Between A Latch and A Flip Flopsumitzz4737Оценок пока нет

- Difference Between A Latch and A Flip Flop PDFДокумент2 страницыDifference Between A Latch and A Flip Flop PDFVenkatGollaОценок пока нет

- DC Unit 4Документ43 страницыDC Unit 4thiruct77Оценок пока нет

- State Reduction and AssignmentДокумент49 страницState Reduction and AssignmentJames Francis100% (4)

- Week 07 Sequential Circuits Sec AДокумент25 страницWeek 07 Sequential Circuits Sec AMuhammad RafayОценок пока нет

- Comb - and - Seq CircuitДокумент13 страницComb - and - Seq CircuitTibebeselasie MehariОценок пока нет

- Programmable Logic Circuit PLCДокумент79 страницProgrammable Logic Circuit PLCRahul100% (7)

- Digital - Chapter 5.sequentialДокумент24 страницыDigital - Chapter 5.sequentialJenberОценок пока нет

- SynthesisДокумент51 страницаSynthesissudhir100% (1)

- Unit-IV, V VLSI DESIGNДокумент91 страницаUnit-IV, V VLSI DESIGN2k20EC034 ANSHULIYERОценок пока нет

- Ee 587 Soc Design & Test: Partha Pande School of Eecs Washington State University Pande@Eecs - Wsu.EduДокумент41 страницаEe 587 Soc Design & Test: Partha Pande School of Eecs Washington State University Pande@Eecs - Wsu.EduRanganadh MvОценок пока нет

- Digital Electronics Module 05Документ44 страницыDigital Electronics Module 05Yadana1Оценок пока нет

- Chapter4 9Документ124 страницыChapter4 9bernabasОценок пока нет

- PLCДокумент34 страницыPLCmurtadhaОценок пока нет

- Unit-Iii Sequential Logic CircuitsДокумент104 страницыUnit-Iii Sequential Logic CircuitsAswin ThangarajuОценок пока нет

- Lecture06 LatchesДокумент30 страницLecture06 LatchesBala KrishnaОценок пока нет

- Digital Logic NotesДокумент79 страницDigital Logic NotesRohini PendhariОценок пока нет

- 35 DLD Lec 35 Introduction and Design of Sequential Circuits Example Dated 07 Dec 2022 Lecture SlidesДокумент12 страниц35 DLD Lec 35 Introduction and Design of Sequential Circuits Example Dated 07 Dec 2022 Lecture SlidesZuha FatimaОценок пока нет

- CH 4 5 Sequinital NewДокумент65 страницCH 4 5 Sequinital NewjoОценок пока нет

- DLD-Lecture# 7Документ11 страницDLD-Lecture# 7Akash missriОценок пока нет

- Week07SequentialCircuitsSecA Part1Документ16 страницWeek07SequentialCircuitsSecA Part1Muhammad RafayОценок пока нет

- Combinational Logic Circuit DesignДокумент22 страницыCombinational Logic Circuit Designrumbidzai.nyikadzinasheОценок пока нет

- 26 Sequential Logic Circuit Introduction 18-02-2023Документ14 страниц26 Sequential Logic Circuit Introduction 18-02-2023Back upОценок пока нет

- Flip Flops: Digital Logic Design LabДокумент23 страницыFlip Flops: Digital Logic Design LabAstitav chauhanОценок пока нет

- RME 2102 Lec 5Документ37 страницRME 2102 Lec 5asraful islamОценок пока нет

- 4 PLCДокумент43 страницы4 PLCAbdullah Al OmarОценок пока нет

- CO Unit-3: Synchronous Sequential LogicДокумент80 страницCO Unit-3: Synchronous Sequential LogicMuni Koteswara Rao CHОценок пока нет

- Fundamentals of PLCs ReviewДокумент65 страницFundamentals of PLCs ReviewPatrickSchardt100% (2)

- 1 Unit 2 Flip FlopsДокумент23 страницы1 Unit 2 Flip FlopsShivangi SharmaОценок пока нет

- Lecture Flip FlopsДокумент17 страницLecture Flip FlopsKrishna VamsiОценок пока нет

- Week 12Документ25 страницWeek 12rdsrajОценок пока нет

- Synchronous Sequential LogicДокумент97 страницSynchronous Sequential LogicHassnainОценок пока нет

- Unit-4 PLCДокумент100 страницUnit-4 PLCKANISHKAR Hem SankarОценок пока нет

- Sequential Circuit: Click To Edit Master Subtitle Style Benitez, Mark Kenneth Cayas, Bernard Van Mendoza, John MichaelДокумент15 страницSequential Circuit: Click To Edit Master Subtitle Style Benitez, Mark Kenneth Cayas, Bernard Van Mendoza, John MichaelJohn Michael S MendozaОценок пока нет

- Topic 7 - Clocking Strategies (4up)Документ8 страницTopic 7 - Clocking Strategies (4up)vijjuvardhan100% (1)

- R20 Unit-1Документ18 страницR20 Unit-1Dr. M V GANESWARA RAOОценок пока нет

- L1 Sequential Circuits and LatchesДокумент30 страницL1 Sequential Circuits and LatchesKogul ShiyamОценок пока нет

- A) Differentiate Between Fan in and Fan Out: Question Bank For Series Test 2Документ5 страницA) Differentiate Between Fan in and Fan Out: Question Bank For Series Test 2Joseph JohnОценок пока нет

- RealDigital Module 8Документ7 страницRealDigital Module 8Sidney O. EbotОценок пока нет

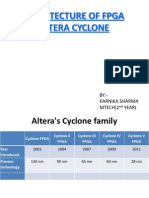

- Architecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)Документ29 страницArchitecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)karnika143100% (1)

- 45 - 70685 - EE541 - 2013 - 1 - 1 - 1 - Part2-Lecture 1Документ59 страниц45 - 70685 - EE541 - 2013 - 1 - 1 - 1 - Part2-Lecture 1Ibrahim Abd elhalimОценок пока нет

- Low Power Design Logic LevelДокумент24 страницыLow Power Design Logic LevelShauryanaditya SinghОценок пока нет

- Flip-Flops and Its Applications: Module - 3Документ41 страницаFlip-Flops and Its Applications: Module - 3Chethan RamachariОценок пока нет

- 1.5-Logic CircuitsДокумент24 страницы1.5-Logic CircuitsBrian Ombura OkalОценок пока нет

- Introduction To Digital DesignДокумент15 страницIntroduction To Digital DesignOzioma Teddy UkwuomaОценок пока нет

- Rev 1 Module2 PLCДокумент293 страницыRev 1 Module2 PLCMuhd IzzatОценок пока нет

- SN1-2223-Lab3 1-2 EngДокумент4 страницыSN1-2223-Lab3 1-2 EngBoualem MestafaОценок пока нет

- 04 Design in Hazard States PDFДокумент43 страницы04 Design in Hazard States PDFJignesh GunasegerenОценок пока нет

- Digital Electronics FLIP FLOPSДокумент11 страницDigital Electronics FLIP FLOPSGautam AggarwalОценок пока нет

- NPTEL: Automation & Controls Module: 4: Programmable Logic ControllersДокумент4 страницыNPTEL: Automation & Controls Module: 4: Programmable Logic ControllersPeersahbОценок пока нет

- Lembar Aktivitas Praktikum: Ringkasan/AbstrakДокумент2 страницыLembar Aktivitas Praktikum: Ringkasan/AbstraksupriantoОценок пока нет

- Lembar Aktivitas Praktikum: Ringkasan/AbstrakДокумент2 страницыLembar Aktivitas Praktikum: Ringkasan/AbstraksupriantoОценок пока нет

- Lembar Aktivitas Praktikum: Ringkasan/AbstrakДокумент2 страницыLembar Aktivitas Praktikum: Ringkasan/AbstraksupriantoОценок пока нет

- Lembar Aktivitas Praktikum: Ringkasan/AbstrakДокумент2 страницыLembar Aktivitas Praktikum: Ringkasan/AbstraksupriantoОценок пока нет

- Lembar Aktivitas Praktikum: Ringkasan/AbstrakДокумент2 страницыLembar Aktivitas Praktikum: Ringkasan/AbstraksupriantoОценок пока нет

- Lembar Aktivitas Praktikum: Ringkasan/AbstrakДокумент2 страницыLembar Aktivitas Praktikum: Ringkasan/AbstraksupriantoОценок пока нет

- Book 1Документ2 страницыBook 1supriantoОценок пока нет

- Lembar Aktivitas Praktikum: Ringkasan/AbstrakДокумент2 страницыLembar Aktivitas Praktikum: Ringkasan/AbstraksupriantoОценок пока нет

- Lembar Aktivitas Praktikum: Ringkasan/AbstrakДокумент2 страницыLembar Aktivitas Praktikum: Ringkasan/AbstraksupriantoОценок пока нет

- Lembar Aktivitas Praktikum: Ringkasan/AbstrakДокумент2 страницыLembar Aktivitas Praktikum: Ringkasan/AbstraksmahsgxОценок пока нет

- Lembar Aktivitas Praktikum: Ringkasan/AbstrakДокумент2 страницыLembar Aktivitas Praktikum: Ringkasan/AbstraksupriantoОценок пока нет

- Lembar Aktivitas Praktikum: Ringkasan/AbstrakДокумент2 страницыLembar Aktivitas Praktikum: Ringkasan/AbstraksupriantoОценок пока нет

- Lembar Aktivitas Praktikum: Ringkasan/AbstrakДокумент2 страницыLembar Aktivitas Praktikum: Ringkasan/AbstraksupriantoОценок пока нет

- Lembar Aktivitas Praktikum: Ringkasan/AbstrakДокумент2 страницыLembar Aktivitas Praktikum: Ringkasan/AbstraksupriantoОценок пока нет

- Few, YgvcjfДокумент1 страницаFew, YgvcjfsupriantoОценок пока нет

- Lembar Aktivitas PraktikumДокумент2 страницыLembar Aktivitas PraktikumsupriantoОценок пока нет

- Week - 5Документ1 страницаWeek - 5supriantoОценок пока нет

- Week 4Документ1 страницаWeek 4supriantoОценок пока нет

- Week 12Документ4 страницыWeek 12supriantoОценок пока нет

- MG 09 1 SortingДокумент13 страницMG 09 1 SortingsupriantoОценок пока нет

- Week 3Документ1 страницаWeek 3supriantoОценок пока нет

- Week 13Документ6 страницWeek 13supriantoОценок пока нет

- Happy SundayДокумент4 страницыHappy SundaysupriantoОценок пока нет

- Week 10Документ3 страницыWeek 10supriantoОценок пока нет

- DS W02S01 Intoduction To Logic Circuits2Документ32 страницыDS W02S01 Intoduction To Logic Circuits2supriantoОценок пока нет

- DS W02S01 Intoduction To Logic Circuits2Документ32 страницыDS W02S01 Intoduction To Logic Circuits2supriantoОценок пока нет

- Partner 1Документ6 страницPartner 1supriantoОценок пока нет

- Lembar Aktivitas PraktikumДокумент2 страницыLembar Aktivitas PraktikumsupriantoОценок пока нет

- Template Laporan PraktikumДокумент5 страницTemplate Laporan PraktikumGottlieb Fyeter SitohangОценок пока нет

- Load Management Part 2Документ8 страницLoad Management Part 2MaxiSanchezОценок пока нет

- MockДокумент19 страницMockSourabh JakharОценок пока нет

- Helix 11.1 Release NotesДокумент18 страницHelix 11.1 Release NotesYasir KhanОценок пока нет

- Service Agreement Between Awfis Space Solutions Private Limited ("Awfis") AND GHV Advanced Care Private Limited ("Company")Документ25 страницService Agreement Between Awfis Space Solutions Private Limited ("Awfis") AND GHV Advanced Care Private Limited ("Company")Abhinav KumarОценок пока нет

- 21 InfotainmentДокумент10 страниц21 InfotainmentIqtidar AОценок пока нет

- FST DFS Gardner DenverДокумент4 страницыFST DFS Gardner DenverEric DunnОценок пока нет

- Project Report NMXXXXДокумент21 страницаProject Report NMXXXXMuhammad MoinОценок пока нет

- Google File System (GFS)Документ18 страницGoogle File System (GFS)Mohit GautamОценок пока нет

- Composite and Inverse FunДокумент14 страницComposite and Inverse FunNiejay Arcullo LlagasОценок пока нет

- Advances in Motor TechnologyДокумент8 страницAdvances in Motor TechnologyWeider SilvaОценок пока нет

- Accounting Volume 1 Canadian 9th Edition Horngren Test Bank 1Документ68 страницAccounting Volume 1 Canadian 9th Edition Horngren Test Bank 1edna100% (33)

- Account Opening and Servicing Part 1.odtДокумент159 страницAccount Opening and Servicing Part 1.odtpriyankaОценок пока нет

- 컴퓨터 키보드의 한글배열 연구Документ86 страниц컴퓨터 키보드의 한글배열 연구Marizouh23Оценок пока нет

- Haryana With CommentsДокумент148 страницHaryana With Commentsmanojkumartomar7513Оценок пока нет

- Name: Marjiesel Pearlbhel N. Cayanan, Zekhyna Nhatallie Reyes, Clarence Fitz Javate Section: 11 STEM 28 WW4.1 - TruthtableДокумент3 страницыName: Marjiesel Pearlbhel N. Cayanan, Zekhyna Nhatallie Reyes, Clarence Fitz Javate Section: 11 STEM 28 WW4.1 - TruthtableClarence JavateОценок пока нет

- Teacher Induction Program Module 6 V1.0Документ41 страницаTeacher Induction Program Module 6 V1.0Jefferson Kevin LerioОценок пока нет

- Digital Banking UpdatesДокумент46 страницDigital Banking Updatesvivek_anandОценок пока нет

- Thar MN04-20CE - ABPR-20 Operator Manual PDFДокумент53 страницыThar MN04-20CE - ABPR-20 Operator Manual PDFSerge LapointeОценок пока нет

- UID SyllabusДокумент2 страницыUID SyllabusSangeetha krОценок пока нет

- IRDH375 Series: Digital Ground Fault Monitor / Ground Detector Ungrounded (Floating) AC/DC SystemsДокумент6 страницIRDH375 Series: Digital Ground Fault Monitor / Ground Detector Ungrounded (Floating) AC/DC SystemsZaw Thet OoОценок пока нет

- Resume 1Документ2 страницыResume 1Quick LearningОценок пока нет

- Generative+Design+Report Final 91818Документ51 страницаGenerative+Design+Report Final 91818Lavinia BucaОценок пока нет

- Engineering Report Writing Using Word 2010: University of WaterlooДокумент75 страницEngineering Report Writing Using Word 2010: University of WaterlooRIANNE JUSTIN POLICARPIOОценок пока нет

- IoT Based Solar Energy Monitoring SystemДокумент5 страницIoT Based Solar Energy Monitoring SystemhatomiОценок пока нет

- 11 Descision TreeДокумент25 страниц11 Descision TreeNikita KhandujaОценок пока нет

- MAPEH 6 - Q1 Exam - 2019 - With Ans Key - BY JULCAIPSДокумент4 страницыMAPEH 6 - Q1 Exam - 2019 - With Ans Key - BY JULCAIPSgay basquinasОценок пока нет

- ResumeДокумент4 страницыResumeSandeep LakkumdasОценок пока нет

- 3AH4 Breaker Cn (油品 P26)Документ29 страниц3AH4 Breaker Cn (油品 P26)kokonut1128Оценок пока нет

- PCG Log BookДокумент22 страницыPCG Log BookPardon Gabriel ChinhamoОценок пока нет

- Introduction ISO 55001Документ66 страницIntroduction ISO 55001Indra GirsangОценок пока нет