Академический Документы

Профессиональный Документы

Культура Документы

Adding and Subtracting BCD Numbers in 8051 Assembly

Загружено:

Faraz Humayun0 оценок0% нашли этот документ полезным (0 голосов)

211 просмотров35 страницОригинальное название

Ch 6 - Arithmetic, Logic Instructions and Programs

Авторское право

© © All Rights Reserved

Доступные форматы

PPTX, PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PPTX, PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

211 просмотров35 страницAdding and Subtracting BCD Numbers in 8051 Assembly

Загружено:

Faraz HumayunАвторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PPTX, PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 35

Unsigned numbers are defined as data in

which all the bits are used to represent data,

and no bits are set aside for the positive or

negative sign. This means that the operand

can be between 00 and FFH (0 to 255

decimal) for 8-bit data.

In the 8051, in order to add numbers together,

the accumulator register (A) must be involved.

The form of the ADD instruction is

ADD A, source ; A = A + source

The instruction ADD is used to add two

operands. The destination operand is always in

register A while the source operand can be a

register, immediate data, or in memory.

Remember that memory-to-memory arithmetic

operations are never allowed in 8051 Assembly

language. The instruction could change any of

the AF, CF, or P bits of the flag register,

depending on the operands involved.

Two numbers are stored in registers R0 and

R1. Verify if their sum is greater than FFH.

MOV A, R0; move first number in A

ADD A, R1; add second number to it

JC MESSAGE; is sum>FFH, CY=1

SJMP NEXT if CY=0, exit

MESSAGE: MOV A,#’Y’;if CY=1 move Y into A

MOV P1,A; send the message ‘Y’ in P1

NEXT: NOP; do nothing

END; end of file

Chapter 2 contained a program that added 5

bytes of data. The sum was purposely kept

less than FFH, the maximum value an 8-bit

register can hold. To calculate the sum of any

number of operands, the carry flag should be

checked after the addition of each operand.

Example 6-2 uses R7 to accumulate carries

as the operands are added to A.

Assume that RAM locations 40 – 44 have the

following values. Write a program to find the

sum of the values. At the end of the program,

register A should contain the low byte and R7

the high byte. All values are in hex.

40=(7D) 41=(EB) 42=(C5) 43=(5B) 44=(30)

When adding two 16-bit data operands, we

need to be concerned with the propagation of

a carry from the lower byte to the higher

byte. The instruction ADDC (add with carry) is

used on such occasions. For example, look at

the addition of 3CE7H + 3B8DH, as shown

below.

Write a program to add two 16-bit numbers.

The numbers are 3CE7H and 3B8DH. Place

the sum in R7 and R6; R6 should have the

lower byte.

Add two 32 bit numbers stored in RAM

locations.

Let the 32 bit numbers be 01453BC0H and

56C705FEH and let them be stored in RAM

locations as shown below:

Address Data Address Data

40H C0H 50H FEH

41H 3BH 51H 05H

42H 45H 52H C7H

43H 01H 53H 56H

The result of addition will be at least 4 bytes

long. If R0 and R1 (of bank 0 by default) are

used as pointers to the addends, there is no

other register available to act as pointer to

the result. Hence it will be necessary to use

R0 of the second register bank. Observe how

the banks are switched

CLR C

MOV R2, #04H

MOV R0, #40H

MOV R1,#50H

SETB PSW.3

MOV R0,#60H

CLR PSW.3

BACK: MOV A, @R0

ADDC A,@R1

INC R0

INC R1

SETB PSW.3

MOV @R0,A

INC R0

CLR PSW.3

DJNZ R2,BACK

The result of addition will be stored in RAM

as:

Address Data

60H BEH

61H 41H

62H OCH

63H 58H

BCD stands for binary coded decimal. BCD is

needed because in everyday life we use the

digits 0 to 9 for numbers, not binary or hex

numbers. Binary representation of 0 to 9 is

called BCD. In computer literature one

encounters two terms for BCD numbers, (1)

unpacked BCD, and (2) packed BCD. We

describe each one next.

BCD code

In unpacked BCD, the lower 4 bits of the

number represent the BCD number, and the

rest of the bits are 0. For example, “0000

1001″ and “0000 0101″ are unpacked BCD

for 9 and 5, respectively. Unpacked BCD

requires 1 byte of memory or an 8-bit

register to contain it.

In packed BCD, a single byte has two BCD

numbers in it, one in the lower 4 bits, and one in

the upper 4 bits. For example, “0101 1001″ is

packed BCD for 59H. It takes only 1 byte of

memory to store the packed BCD operands. And

so one reason to use packed BCD is that it is

twice as efficient in storing data.

There is a problem with adding BCD numbers,

which must be corrected. The problem is that

after adding packed BCD numbers, the result is

no longer BCD. Look at the following.

Adding these two numbers gives 0011 111 IB (3FH), which is

not BCD! A BCD number can only have digits from 0000 to

1001 (or 0 to 9). In other words, adding two BCD numbers

must give a BCD result. The result above should have been 17

+ 28 = 45 (0100 0101). To correct this problem, the

programmer must add 6 (0110) to the low digit: 3F + 06 =

45H. The same problem could have happened in the upper

digit (for example, in 52H + 87H = D9H). Again to solve this

problem, 6 must be added to the upper digit (D9H + 60H =

139H) to ensure that the result is BCD (52 + 87 = 139). This

problem is so pervasive that most microprocessors such as

the 8051 have an instruction to deal with it. In the 8051 the

instruction “DA A” is designed/to correct the BCD addition

problem. This is discussed next.

The DA (decimal adjust for addition)

instruction in the 8051 is provided to correct

the aforementioned problem associated with

BCD addition. The mnemonic “DA” has as its

only operand the accumulator “A”. The DA

instruction will add 6 to the lower nibble or

higher nibble if needed; otherwise, it will

leave the result alone. The following example

will clarify these points.

After the program is executed, register A will contain 72H

(47 + 25 = 72). The “DA” instruction works only on A. In

other words, while the source can be an operand of any

addressing mode, the destination must be in register A in

order for DA to work. It also needs to be emphasized that

DA must be used after the addition of BCD operands and

that BCD operands can never have any digit greater than

9. In other words, A – F digits are not allowed. It is also

important to note that DA works only after an ADD

instruction; it will not work after the INC instruction.

Assume that 5 BCD data items are stored in

RAM locations starting at 40H, as shown

below. Write a program to find the sum of all

the numbers. The result must be in BCD.

40= (71) 41=(11) 42=(65) 43=(59) 44=(37)

SUBB A, source ; A=A-source-CY

In many microprocessors there are two different

instructions for subtraction: SUB and SUBB

(subtract with borrow). In the 8051 we have only

SUBB. To make SUB out of SUBB, we have to make

CY = 0 prior to the execution of the instruction.

Therefore, there are two cases for the SUBB

instruction: (1) with CY = 0, and (2) with CY = 1.

First we examine the case where CY = 0 prior to

the execution of SUBB. Notice that we use the CY

flag for the borrow.

In subtraction, the 8051 microprocessors

(indeed, all modern CPUs) use the 2′s

complement method. Although every CPU

contains adder circuitry, it would be too

cumbersome (and take too many transistors) to

design separate subtracter circuitry. For this

reason, the 8051 uses adder circuitry to perform

the subtraction command. Assuming that the

8051 is executing a simple subtract instruction

and that CY = 0 prior to the execution of the

instruction, one can summarize the steps of the

hardware of the CPU in executing the SUBB

instruction for unsigned numbers, as follows.

Take the 2′s complement of the subtrahend (source

operand).

Add it to the minuend (A).

Invert the carry.

These three steps are performed for every SUBB

instruction by the internal hardware of the 8051 CPU,

regardless of the source of the operands, provided

that the addressing mode is supported. After these

three steps the result is obtained and the flags are

set. Example 6-5 illustrates the three steps.

If CY = 0 after the execution of SUBB, the

result is positive; if CY=1 the result is

negative and the destination has the 2’s

complement of the result. Normally the result

is left in 2’s complement, but the CPL

(complement) and INC (increment)instructions

can be used to change it.

This instruction is used for multibyte

numbers and will take care of the borrow of

the lower operand. If CY = 1 prior to

executing the SUBB instruction, it also

subtracts 1 from the result. See Example 6-7.

Analyze the following program:

After the SUBB, A = 62H – 96H = CCH and the

carry flag is set high indicating there is a

borrow. Since CY = 1, when SUBB is executed

the second time A = 27H – 12H -1 = 14H.

Therefore, we have 2762H – 1296H = 14CCH.

Student Home Work

Вам также может понравиться

- Aritmatika PLCДокумент24 страницыAritmatika PLCIkhtiardwiОценок пока нет

- ROM, RAM, registers and instruction sets of 8051 microcontrollerДокумент13 страницROM, RAM, registers and instruction sets of 8051 microcontrollerpareshrockОценок пока нет

- Instruction Set: DR Narayana Swamy RДокумент48 страницInstruction Set: DR Narayana Swamy RDr Narayana Swamy RamaiahОценок пока нет

- Chap 6Документ35 страницChap 6h.kev07Оценок пока нет

- 8051-CH6-ArithLigic InstructnsДокумент114 страниц8051-CH6-ArithLigic Instructnsshivaspy100% (1)

- 8051 InstructionsДокумент24 страницы8051 Instructionssasitharan33Оценок пока нет

- 6-Branch & Bitwise Instructions-12-01-2023 PDFДокумент43 страницы6-Branch & Bitwise Instructions-12-01-2023 PDFBRO CUBIESОценок пока нет

- Week 3Документ31 страницаWeek 3Ali AhmadОценок пока нет

- 8051 InstructionsДокумент24 страницы8051 InstructionsMurali VannappanОценок пока нет

- The 8051 Microcontroller & Embedded Systems: Muhammad Ali Mazidi, Janice Mazidi & Rolin MckinlayДокумент57 страницThe 8051 Microcontroller & Embedded Systems: Muhammad Ali Mazidi, Janice Mazidi & Rolin MckinlayAkshwin KisoreОценок пока нет

- Microcontroller (1) Lab Manual: Prepared By: Eng: Mohsen Ali AL-awami Supervisered By: DR: Fadel AL-aqawa 2010-2011Документ19 страницMicrocontroller (1) Lab Manual: Prepared By: Eng: Mohsen Ali AL-awami Supervisered By: DR: Fadel AL-aqawa 2010-2011sialibraryОценок пока нет

- 2-Microcontroller 8051, Organization and Architecture-08!01!2024Документ35 страниц2-Microcontroller 8051, Organization and Architecture-08!01!2024rupinsgmОценок пока нет

- Assembly LanguageДокумент22 страницыAssembly LanguageUtpal Kumar Pal100% (1)

- Types of InstructionsДокумент13 страницTypes of InstructionsJoseph JoyОценок пока нет

- 4 ThunitДокумент5 страниц4 ThunitJawaharsantosh GundapaneniОценок пока нет

- Unit 4 Arithmetic-Logic InstructionsДокумент38 страницUnit 4 Arithmetic-Logic Instructionsrtripp5543Оценок пока нет

- Microcontroller 8051Документ27 страницMicrocontroller 8051FatimaRaufОценок пока нет

- Phu Luc 4 Mo Ta Tap Lenh Vi Dieu Khien MCS-51 - Smith.N StudioДокумент40 страницPhu Luc 4 Mo Ta Tap Lenh Vi Dieu Khien MCS-51 - Smith.N StudioSmith Nguyen StudioОценок пока нет

- 8051 Instruction Set GuideДокумент19 страниц8051 Instruction Set Guideharshad lokhandeОценок пока нет

- Chapter 5 - Arithmetic and Logic Instructions and ProgramsДокумент85 страницChapter 5 - Arithmetic and Logic Instructions and ProgramssemibagerОценок пока нет

- Addressing ModesДокумент6 страницAddressing ModesabinayamalathyОценок пока нет

- Embedded Systems With 8051 CДокумент190 страницEmbedded Systems With 8051 CPayal SinghОценок пока нет

- Instruction Set of 8051Документ17 страницInstruction Set of 8051Amarjeet KumarОценок пока нет

- InstructionsДокумент70 страницInstructionsAkshay AjayОценок пока нет

- DTSP Unit 5Документ12 страницDTSP Unit 5GurunathanОценок пока нет

- Unit 2Документ21 страницаUnit 2mrunal1729Оценок пока нет

- Arithmetic & Logic InstructionsДокумент50 страницArithmetic & Logic InstructionsTahir ImtiazОценок пока нет

- ESI Record RemovedДокумент17 страницESI Record Removedsangee20039Оценок пока нет

- Chapter2-Microcontroller Architecture & Assembly Language Pt3Документ36 страницChapter2-Microcontroller Architecture & Assembly Language Pt3adamwaiz100% (2)

- Ec522 8051 04Документ125 страницEc522 8051 04Anurag BansalОценок пока нет

- 8051 Instruction Set and Registers ExplainedДокумент134 страницы8051 Instruction Set and Registers ExplainedAnirudh sai ReddyОценок пока нет

- Lab Practical File: " Embedded System's "Документ17 страницLab Practical File: " Embedded System's "Saba WasimОценок пока нет

- ALU, Logic Instructions & Program FundamentalsДокумент62 страницыALU, Logic Instructions & Program FundamentalsColesha BarukaОценок пока нет

- 2a. CS602 Microprocessor and Microcontroller - SoftwareДокумент44 страницы2a. CS602 Microprocessor and Microcontroller - SoftwareRehan NightОценок пока нет

- Registers 8051Документ6 страницRegisters 8051chanty chantyОценок пока нет

- MM Module2 Cse NotesДокумент54 страницыMM Module2 Cse NotesNaveen NОценок пока нет

- AL41Документ104 страницыAL41adddataОценок пока нет

- 8086 Instruction SetДокумент22 страницы8086 Instruction SetlekaОценок пока нет

- NEC 022 External Paper SolutionДокумент13 страницNEC 022 External Paper SolutionSachin PalОценок пока нет

- 3.1 Addressing Modes: ECP2036 Microprocessors System and Interfacing Chapter 3: The 8051 Instruction SetДокумент6 страниц3.1 Addressing Modes: ECP2036 Microprocessors System and Interfacing Chapter 3: The 8051 Instruction SetSwetha ChinnikannuОценок пока нет

- ECE3003 M A 2018: Icrocontroller and Its Applications SsignmentДокумент43 страницыECE3003 M A 2018: Icrocontroller and Its Applications SsignmentAayoshi DuttaОценок пока нет

- 8085 Paper Presentation 1232646931472979 2Документ112 страниц8085 Paper Presentation 1232646931472979 2Arun DasОценок пока нет

- Module-2 Complete NotesДокумент31 страницаModule-2 Complete NotesManjuanthОценок пока нет

- AE2406 Lab ManualДокумент73 страницыAE2406 Lab ManualSathya NarayananОценок пока нет

- Arithmetic & Logic Instructions and Programs: The 8051 Microcontroller and Embedded Systems: Using Assembly and CДокумент44 страницыArithmetic & Logic Instructions and Programs: The 8051 Microcontroller and Embedded Systems: Using Assembly and CKrishna Prasath GurumoorthyОценок пока нет

- Microcontroller (1) Lab Manual: Prepared By: Eng: Mohsen Ali AL-awami Supervisered By: DR: 2010-2011Документ20 страницMicrocontroller (1) Lab Manual: Prepared By: Eng: Mohsen Ali AL-awami Supervisered By: DR: 2010-2011Nazma BegumОценок пока нет

- Introduction to the 8085 MicroprocessorДокумент112 страницIntroduction to the 8085 MicroprocessorMansi Shah ShroffОценок пока нет

- AE2406 Lab ManualДокумент73 страницыAE2406 Lab ManualPrabha Karan100% (1)

- 8051 Architecture FullДокумент39 страниц8051 Architecture FullRaja RajОценок пока нет

- GANDHINAGAR INSTITUTE OF TECHNOLOGYДокумент114 страницGANDHINAGAR INSTITUTE OF TECHNOLOGYlvsaruОценок пока нет

- Microproccessor NOTESДокумент55 страницMicroproccessor NOTESharshitharaghuramОценок пока нет

- List of Experiments: Group AДокумент78 страницList of Experiments: Group APooja BkОценок пока нет

- Midsem SolnДокумент7 страницMidsem SolnDevang KhandelwalОценок пока нет

- 8086 InstructionsДокумент6 страниц8086 InstructionsMalgireddy RavireddyОценок пока нет

- Projects With Microcontrollers And PICCОт EverandProjects With Microcontrollers And PICCРейтинг: 5 из 5 звезд5/5 (1)

- Conceptual Programming: Conceptual Programming: Learn Programming the old way!От EverandConceptual Programming: Conceptual Programming: Learn Programming the old way!Оценок пока нет

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationОт EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationОценок пока нет

- Distributed Generation Environment for the Smart GridДокумент38 страницDistributed Generation Environment for the Smart GridsreekanthОценок пока нет

- SGДокумент22 страницыSGsue_sukmaОценок пока нет

- DG & Power Quality 2Документ13 страницDG & Power Quality 2Faraz HumayunОценок пока нет

- Impact of Distributed Generation on Electric Power SystemsДокумент23 страницыImpact of Distributed Generation on Electric Power SystemsFaraz HumayunОценок пока нет

- Impact of Distributed Generation on Electric Power SystemsДокумент23 страницыImpact of Distributed Generation on Electric Power SystemsFaraz HumayunОценок пока нет

- Distributed Generation Landscape in PakistanДокумент5 страницDistributed Generation Landscape in PakistanInstitute of Policy StudiesОценок пока нет

- Smart Grid - Integration of Distributed Generation Prof Mohan KolheДокумент20 страницSmart Grid - Integration of Distributed Generation Prof Mohan KolheAdhi Tharsia PutraОценок пока нет

- Complex Engineering Problems (Mapping)Документ1 страницаComplex Engineering Problems (Mapping)Faraz HumayunОценок пока нет

- Communication Systems Week 6: Dr. Haroon RasheedДокумент35 страницCommunication Systems Week 6: Dr. Haroon RasheedFaraz HumayunОценок пока нет

- Network Cabling: Making Connections With Cat5Документ18 страницNetwork Cabling: Making Connections With Cat5Faraz HumayunОценок пока нет

- Instructor: Prof. Ali Keyhani Office: 202 Caldwell E Mail: Webpage: Office Hours: Will Be Announced in Class or by AppointmentДокумент2 страницыInstructor: Prof. Ali Keyhani Office: 202 Caldwell E Mail: Webpage: Office Hours: Will Be Announced in Class or by AppointmentFaraz HumayunОценок пока нет

- What is Network CablingДокумент21 страницаWhat is Network CablingFaraz HumayunОценок пока нет

- Power Distribution and Utilization-EE-315Документ2 страницыPower Distribution and Utilization-EE-315Faraz HumayunОценок пока нет

- Computer Networks (Theory) Cs-422: Recommended BooksДокумент3 страницыComputer Networks (Theory) Cs-422: Recommended BooksFaraz HumayunОценок пока нет

- William Stallings Data and Computer Communications 9 EditionДокумент41 страницаWilliam Stallings Data and Computer Communications 9 EditionFaraz HumayunОценок пока нет

- Major Ethics Case Studies: Focus On The Major Technological Disasters and Catastrophes in EngineeringДокумент7 страницMajor Ethics Case Studies: Focus On The Major Technological Disasters and Catastrophes in EngineeringFaraz HumayunОценок пока нет

- Power Electronics (EL-343)Документ52 страницыPower Electronics (EL-343)Faraz HumayunОценок пока нет

- Unit-Ii Engineering EthicsДокумент33 страницыUnit-Ii Engineering EthicsFaraz HumayunОценок пока нет

- chpt09 1Документ13 страницchpt09 1Krishna ReddyОценок пока нет

- Unit-Ii Engineering EthicsДокумент33 страницыUnit-Ii Engineering EthicsFaraz HumayunОценок пока нет

- Unit-Ii Engineering EthicsДокумент33 страницыUnit-Ii Engineering EthicsFaraz HumayunОценок пока нет

- Lecture 17 PDFДокумент7 страницLecture 17 PDFFaraz HumayunОценок пока нет

- Everyday Engineering Ethics: A Discussion of Common Ethical Issues Facing The Engineering ProfessionalДокумент7 страницEveryday Engineering Ethics: A Discussion of Common Ethical Issues Facing The Engineering ProfessionalFaraz HumayunОценок пока нет

- Unit-Ii Engineering EthicsДокумент33 страницыUnit-Ii Engineering EthicsFaraz HumayunОценок пока нет

- Codes of Ethics: The Value in Developing A Code of Ethics For A Profession or in An OrganizationДокумент18 страницCodes of Ethics: The Value in Developing A Code of Ethics For A Profession or in An OrganizationJoyce Fabros VillaОценок пока нет

- Codes of Ethics: The Value in Developing A Code of Ethics For A Profession or in An OrganizationДокумент18 страницCodes of Ethics: The Value in Developing A Code of Ethics For A Profession or in An OrganizationJoyce Fabros VillaОценок пока нет

- Engineering Ethics: An Introduction To Ethics and Its Relevance To The Profession of EngineeringДокумент25 страницEngineering Ethics: An Introduction To Ethics and Its Relevance To The Profession of EngineeringFaraz HumayunОценок пока нет

- Lecture 17 PDFДокумент7 страницLecture 17 PDFFaraz HumayunОценок пока нет

- RLC Circuit Analysis and Response TypesДокумент10 страницRLC Circuit Analysis and Response TypesFaraz HumayunОценок пока нет

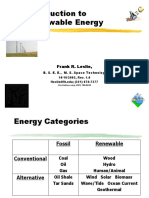

- An Introduction To Renewable Energy: Frank R. LeslieДокумент39 страницAn Introduction To Renewable Energy: Frank R. LeslieFaraz HumayunОценок пока нет

- ViewSonic MY - IFP6550-3 65 - 4K Touch Screen ViewBoardДокумент3 страницыViewSonic MY - IFP6550-3 65 - 4K Touch Screen ViewBoardhahsОценок пока нет

- Operation Management Assignment 1 Provides Overview of Mass Customization and Inventory AccuracyДокумент7 страницOperation Management Assignment 1 Provides Overview of Mass Customization and Inventory AccuracyHarprit SinghОценок пока нет

- Data Privacy Act A Simple Guide For TeachersДокумент23 страницыData Privacy Act A Simple Guide For TeachersJay ZacariasОценок пока нет

- Hydrogen Application Step by Step GuideДокумент13 страницHydrogen Application Step by Step Guidewindreader1Оценок пока нет

- Ezra A. Emmons: 4468 Gilbert Avenue Western Springs, IL 60558 (708) 308-3666Документ3 страницыEzra A. Emmons: 4468 Gilbert Avenue Western Springs, IL 60558 (708) 308-3666Ez RaОценок пока нет

- Kubota M8540 M9540 WSMДокумент662 страницыKubota M8540 M9540 WSMplbeauregardОценок пока нет

- Ingersoll Rand Parts ListДокумент42 страницыIngersoll Rand Parts ListIzabela SantanaОценок пока нет

- Components of A Computer - Information Technology and CommunicationДокумент7 страницComponents of A Computer - Information Technology and CommunicationDarryl John PasambaОценок пока нет

- Linux File System - Ext2 Vs Ext3 Vs Ext4 Vs XFSДокумент2 страницыLinux File System - Ext2 Vs Ext3 Vs Ext4 Vs XFSridteamОценок пока нет

- RMA Case StudyДокумент8 страницRMA Case StudyJohnny NguyenОценок пока нет

- Atif CV (Architect) PKДокумент2 страницыAtif CV (Architect) PKFahad0% (1)

- Print Ict 2 Reviewer Last TopicДокумент3 страницыPrint Ict 2 Reviewer Last Topicinquiries.francisОценок пока нет

- 3D Network Blu-Ray / Disc Player With Media Library: Service ManualДокумент147 страниц3D Network Blu-Ray / Disc Player With Media Library: Service ManualPaul KupasОценок пока нет

- Digital Marketing 1Документ22 страницыDigital Marketing 1vaishnaviОценок пока нет

- AFS SD Process - OverviewДокумент40 страницAFS SD Process - OverviewBiswaranjan Senapati100% (1)

- Evinrude Carburetor Group Parts For 1966 18hp 18602 Outboard MotorДокумент8 страницEvinrude Carburetor Group Parts For 1966 18hp 18602 Outboard MotorWouter GrootОценок пока нет

- 55W Constant Current LED Driver DIP Switch SeriesДокумент5 страниц55W Constant Current LED Driver DIP Switch SeriesE ShОценок пока нет

- Test Logic Insertion For Optimization of Testing Parameters On Lower Technology NodeДокумент6 страницTest Logic Insertion For Optimization of Testing Parameters On Lower Technology NodeshaguftaОценок пока нет

- Nexo WhitepaperДокумент24 страницыNexo WhitepapersachinОценок пока нет

- Capacitor Placement in A Distribution System For Power Factor Correction: An Optimization ApproachДокумент6 страницCapacitor Placement in A Distribution System For Power Factor Correction: An Optimization Approachrizkypratamaputra58Оценок пока нет

- Computer Science (9618) 17.02 PROTOCOLS: Prepared by Rakesh Kumar Chaudhari Rato Bangala SchoolДокумент32 страницыComputer Science (9618) 17.02 PROTOCOLS: Prepared by Rakesh Kumar Chaudhari Rato Bangala SchoolUttam PathakОценок пока нет

- SCM - The HR DisconnectДокумент16 страницSCM - The HR DisconnectsirfanalizaidiОценок пока нет

- PYTHON HACKING GUIDEДокумент34 страницыPYTHON HACKING GUIDEElias JuniorОценок пока нет

- Clement Njoku 469-463-9712: Skills/CompetenciesДокумент3 страницыClement Njoku 469-463-9712: Skills/CompetenciesclemОценок пока нет

- Tally Erp 9.0 Material Control Centre in Tally Erp 9.0Документ27 страницTally Erp 9.0 Material Control Centre in Tally Erp 9.0Raghavendra yadav KMОценок пока нет

- Ez Publish Basics PDFДокумент2 страницыEz Publish Basics PDFKashiaОценок пока нет

- Simple JSON REST Consumption With GSON API - CodeProjectДокумент4 страницыSimple JSON REST Consumption With GSON API - CodeProjectgfgomesОценок пока нет

- P1271 1272 PDFДокумент11 страницP1271 1272 PDFHasnain Diesel100% (2)

- Log Cat 1672840062074Документ28 страницLog Cat 1672840062074Sukir Ngeburna DaraОценок пока нет

- Huawei HCNA-VC Certification TrainingДокумент3 страницыHuawei HCNA-VC Certification TrainingArvind JainОценок пока нет