Академический Документы

Профессиональный Документы

Культура Документы

El Procesador

Загружено:

Francisco Perez Lara0 оценок0% нашли этот документ полезным (0 голосов)

16 просмотров43 страницыОригинальное название

El procesador

Авторское право

© Attribution Non-Commercial (BY-NC)

Доступные форматы

PPTX, PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Attribution Non-Commercial (BY-NC)

Доступные форматы

Скачайте в формате PPTX, PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

16 просмотров43 страницыEl Procesador

Загружено:

Francisco Perez LaraАвторское право:

Attribution Non-Commercial (BY-NC)

Доступные форматы

Скачайте в формате PPTX, PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 43

COLESH

El procesador

CATEDRATICO: Ing. Francisco Pérez Lara

1. Introducción

Todos los CPUs x86 compatibles con la PC

son procesadores CISC (Computadora de

Conjunto de Instrucciones Complejas), pero en

las Mac nuevas o en alguna que se hagan

dibujos de ingeniería complejos,

probablemente tengan un CPU RISC

(Computadora de Conjunto de Instrucciones

Reducido).

La diferencia práctica entre CISC y RISC es que los

procesadores CISCx86 corren a DOS, Windows 3.1

y Windows 95 en el modo nativo; es decir, sin la

traducción de software que disminuya el

desempeño. Pero CISC y RISC también reflejan dos

filosofías de computación rivales. El procesamiento

de RISC requiere breves instrucciones de software

de la misma longitud, que son fáciles de procesar

rápidamente y en tandém por un CPU.

En contraste, un procesador de CISC tiene que

procesar instrucciones más largas de longitud

desigual. Es más difícil procesar múltiples

instrucciones de CISC a la vez.

Los que proponen RISC mantienen que su método de

procesamiento es más eficiente y más escalable, por lo

que los arquitectos pueden añadir unidades de ejecución

más fácilmente a un diseño existente y aumentar el

rendimiento (las unidades de ejecución son los circuitos

dentro del chip que hacen gran parte del trabajo).

Similarmente, RISC facilita el multiprocesamiento

verdadero, donde varios CPUs trabajan simétricamente

mientras dividen, ejecutan y ensamblan una cadena de

instrucción; los chips CISC pueden hacer lo mismo, pero

no son tan efectivos.

.La simplicidad de las instrucciones de RISC

también significa que requieren menos lógica

para ejecutar, reduciendo el costo del chip.

Pocos en el campo del CISC discuten estos

hechos, prefiriendo apuntar a la realidad <<la

gran mayoría del software para la PC está

escrito para procesadores CISC>>.

Todo el debate de CISC/RISC puede ser

irrelevante pronto debido a que nuevas técnicas

están convergiendo. El Pentium Pro, el Nx586

y el K5 son básicamente procesadores RISC en

su núcleo. Toman las instrucciones de CISC y

las traducen a instrucciones estilo RISC.

Para la generación que sigue al Pentium Pro,

Intel y Hewlett-Packard están colaborando en un

CPU híbrido que pueda aceptar instrucciones

RISC y CISC. Si ese chip crea un estándar, puede

acelerar el cambio hacia el software optimizado

para RISC. Un mundo de RISC significaría

CPUs más poderosos, y más baratos. Cuando

quiera mejorar, simplemente puede añadir otro

CPU en lugar de desprenderse de su viejo CPU.

Procesadores: CISC y RISC

Los procesadores se agrupan hoy en dos

familias, la más antigua y común de las cuales

es la "CISC" o "Complex InstructionSet

Computer": computador de set complejo de

instrucciones. Esto corresponde a procesadores

que son capaces de ejecuta run gran número de

instrucciones pre-definidas en lenguaje de

máquina (del orden del centenar).

CISC y RISC

Desde hace unos años se fabrican y utilizan en algunas

máquinas procesadores "RISC" es decir con un número

reducido de instrucciones. Esto permite una ejecución más

rápida de las instrucciones pero requiere compiladores (o

sea traductores automáticos de programas) más complejos

ya que las instrucciones que un "CISC" podría admitir pero

no un "RISC", deben ser escritas como combinaciones de

varias instrucciones admisibles del "RISC". Se obtiene una

ganancia en velocidad por el hecho que el RISC domina

instrucciones muy frecuentes mientras son operaciones

menos frecuentes las que deben descomponerse

CISC y RISC

Hace ya tiempo que se ha empezado a

investigar sobre microprocesadores "hibridos",

es decir, han llevado a cabo el que las nuevas

CPU's no sean en su cien por cien CISC, sino

por el contrario, que estas ya contengan

algunos aspectos de tecnologia RISC.

CISC y RISC

Este propósito se ha realizado con el fin de

obtener ventajas procedentes de ambas

tecnologías (mantener la compatibilidad x86

de los CISC, y a la vez aumentar las

prestaciones hasta aproximarse a un RISC), sin

embargo, este objetivo todavía no se ha

conseguido, de momento se han introducido

algunos puntos del RISC, lo cual no significa

que hayan alcanzado un nivel optimo.

CISC y RISC

Las diferencias son cada vez mas borrosas entre las

arquitecturas CISC y RISC. Las CPU's combinan

elementos de ambas y no son faciles de encasillar. Por

ejemplo, el Pentium Pro traduce las largas

instrucciones CISC de la arquitectura x86 a

microoperaciones sencillas de longitud fija que se

ejecutan en un nucleo de estilo RISC. El UltraSparc-II

de Sun, acelera la decodificacion MPEG con unas

instrucciones especiales para graficos; estas

instrucciones obtienen unos resultados que en otros

procesadores requeririan 48 instrucciones.

CISC y RISC

Por lo tanto a corto plazo, en el mercado

coexistiran las CPU's RISC y los

microprocesadores hibridos RISC - CISC, pero

cada vez con diferencias mas difusas entre

ambas tecnologias. De hecho, los futuros

procesadores lucharan en cuatro frentes :

Los futuros procesadores lucharan en cuatro

frentes

Ejecutar mas instrucciones por ciclo.

Ejecutar las instrucciones en orden distinto del

original para que las interdependencias

Entre operaciones sucesivas no afecten al

rendimiento del procesador.

Renombrar los registros para paliar la escasez

de los mismos.

Contribuir a acelerar el rendimiento global del

sistema, además de la velocidad de la CPU.

algunas de las CPU's, recién salidas o

próximas a salir:

Kripton - 5 O K5 De Amd

Estado Actual : Muestras comerciales.

Velocidad Prevista : 120 Mhz

Rendimiento Estimado : Entre 109 y 115 SPECint92.

Proceso de Fabricacion : CMOS de tres capas de metal.

Tamaño de la Tecnologia de Proceso : 0'35 micras

Ventajas Tecnologicas :

Microarquitectura superescalar de cuatro vias

algunas de las CPU's, recién salidas o

próximas a salir:

Núcleo de tipo RISC desacoplado

Ejecución especulativa con reordenación de instrucciones

Desventajas Tecnológicas :

Velocidades de reloj inferiores a las inicialmente previstas

Las extensas pruebas de compatibilidad han retrasado el

lanzamiento

Pentium pro de intel

Estado Actual : Inicios de producción.

Velocidad Prevista : 150 Mhz

Rendimiento Estimado : Entre 220 SPECint92;

215 SPECfp92

Proceso de Fabricación : BiCMOS.

Tamaño de la Tecnología de Proceso : 0'6

micras

Ventajas Tecnologicas :

Paquete multichip que integra una cache secundaria de 256 KB

que se comunica con la CPU a la misma velocidad del

procesador

Micro arquitectura superescalar con reordenación de

instrucciones

Superpipelines incluidos para permitir altas velocidades de

reloj.

Desventajas Tecnológicas :

Alto precio de fabricación del paquete multichip

Micro arquitectura optimizada para software de 32 bits, que

tienen rendimiento pobre con código de 16 bits

Consumo de energía y disipación de calor totalmente

inapropiadas para ordenadores portátiles.

Mips

Estado Actual : Primeras pruebas de produccion

Velocidad de reloj Prevista : 200 Mhz

Rendimiento Estimado : 300 SPECint92 y 600

SPECfp92

Proceso de Fabricacion : CMOS

Tamaño de la Tecnologia de Proceso : 0'35 micras

Ventajas Tecnologicas

Este chip de 64 bits tiene cinco pipelines

funcionales, por lo que puede llegar a ejecutar

cinco instrucciones por ciclo de reloj. Con dos

unidades de coma flotante de precisión doble,

el R10000 esta optimizado para sostener un

alto rendimiento de coma flotante.

Desventajas Tecnologicas

Para optimizar el rendimiento, la memoria

cache secundaria externa tiene que fabricarse

con costosa tecnología SRAM.

Sun microsystems

Estado Actual : Diseño

Velocidad de Reloj Prevista : de 250 a 300

Mhz

Rendimiento Estimado : De 350 a 420

SPECint92 y de 550 a 660 SPECfp92

Proceso de Fabricación : CMOS de cinco capas

de metal.

Tamaño de la Tecnología de Proceso : 0'3

micras

Ventajas Tecnologicas

El UltraSparc-II es una CPU de 64 bits

superescalar de cuatro vías que no ha sido

optimizada para tener unas altas cifras de

rendimiento puro, sino para aplicaciones

multimedia y de red.

Desventajas Tecnologicas

La falta de asistencia por hardware para

reordenar instrucciones crea una gran

dependencia hacia la calidad de los

compiladores y exige la re compilación del

software anterior para disfrutar de todas las

ventajas del chip UltraSparc-II.

Hewlett - packard

Estado Actual : Muestras de producción

Velocidad de Reloj Prevista : de 200 Mhz

Rendimiento Estimado : Superior a 360 SPECint92

y 550 SPECfp92

Proceso de Fabricación : CMOS

Tamaño de la Tecnología de Proceso : 0'5 micras

Ventajas Tecnologicas

HP es el único fabricante RISC que deja fuera

del chip las memorias cache primarias de

instrucciones y datos, por lo que pueden tener

un tamaño de varios megabytes y tener un

buen rendimiento con los datos de tamaño

excesivo para la cache, que suelen ser

problemáticas para otros núcleos RISC

diseñados solo para la velocidad de proceso.

Desventajas Tecnologicas

Las caches externas funcionan a la misma

velocidad que la CPU y, por tanto, deben estar

fabricadas con la costosísima SRAM

ultrarrápida.

Fundamentos y origen del risc

Los titulares que definen la arquitectura RISC, podría

resumirse, con la suficiente flexibilidad, en varios puntos

:

Reducción del numero de instrucciones ( ensamblador ).

Uso intensivo de registros, disminuyendo los accesos a

memoria.

Simplificación de la CPU en aras de una mayor

velocidad de proceso.

Empleo de memorias cache.

Utilización de "compiladores optimizados", generadores

de código objeto adaptado a los requerimientos de la

CPU.

Corazón del risc

Sera ella quien dicte las acciones a tomar tras leer

la información contenida en memoria. Se alimenta

de instrucciones en lenguaje ensamblador para, a

partir de cada una de estas, generar una pléyade de

ordenes ( micro ordenes ) que, semiocultas al

programador, recorrerán las interioridades del

propio procesador, activando registros, etc.,... de su

complejo hardware, a la vez que escapan hacia el

exterior de la CPU con la misión de gobernar el

comportamiento de la memoria buses de E/S, etc.

Corazón del risc

Las CPU's cuentan con una pequeña memoria de

control de naturaleza ROM en la que se graba el

conjunto de micro ordenes que corresponden a cada

instrucción. Cuando una de estas es introducida en

el procesador, lo que se hace realmente es

utilizarla para direccionar adecuadamente la

memoria de control y obtener así las micro

órdenes correspondientes. ¿Ventajas? Un cambio en

las instrucciones solo exige regrabar esta ROM.

¿ COMO SURGE EL RISC ?

Los ordenadores etiquetados como CISC

gozan de los privilegios y defectos del micro

código. La CPU es considerablemente mas

rápida que la memoria principal. Esto significa

que conviene manejar un amplio abanico de

instrucciones complejas cuyo significado

equivalga al de varias instrucciones simples,

disminuyendo así los accesos a memoria.

Instrucciones mas usadas

Esto significa que se poseían soberbias

memorias de control cuyo contenido era muy

poco utilizado. Se estaba penalizando la

velocidad de respuesta en aras de tener

información poco útil.

Instrucciones mas usadas

La alternativa RISC se basa en esto y propone

procesadores cableados con un repertorio

simple de instrucciones sencillas y

frecuentes; todo código complejo puede

descomponerse en varios congéneres mas

elementales en los que, para evitar los terribles

efectos sobre los retardos de la memoria

principal (MP), se recurre a numerosos

registros y a memorias cache.

Instrucciones mas usadas

Un registro es una unidad de almacenamiento

enclavada en la CPU y, por tanto, tan rápida como

esta. Las memorias cache son pequeñas memorias de

alta velocidad, se alimentan de la MP, de la que

toman la información que esta siendo mas

frecuentemente utilizada. Otro de los objetivos del

RISC fue lograr que a cada instrucción

correspondiera un solo ciclo de reloj, a excepción,

de aquellos casos que hay que mover datos.

objetivos del RISC

Disminuye la probabilidad de fallo.

Reduce el tamaño de la CPU, que puede entonces

albergar mas recursos (registros).

Facilita el diseño.

Permite maquinas mas compactas y con menor

consumo.

A menor complejidad... menor coste.

Aun así con todos los datos obtenidos a favor y en

contra del CISC y del RISC, hay que tener en cuenta

otro factor importante : la eficacia del software.

¿ Risc o cisc ?

El conflicto surge al evaluar las ventajas netas

¿ que es mas apropiado, usar muchas

instrucciones de un solo ciclo aprovechadas al

máximo, o pocas de múltiples pasos de reloj en

las que existe infrautilización ?

¿ Risc o cisc ?

La cuestión, es que hasta el momento, el

estudio de prestaciones de ambas tecnologías,

nos ha llevado a concluir que hoy en día los

RISC obtienen mas prestaciones, es decir, son

mas potentes y rápidos que los CISC. Sin

embargo, el mercado se ha enfocado por la

tecnología CISC en cuanto a volumen de

ventas.

¿ Por que ?

1.- Por experiencia propia, podemos

comprobar que un CISC tiene un coste

"razonable", que es alcanzado a nivel de

usuario. Esto mismo, no ocurre con los RISC,

que por el contrario tienen un coste elevado,

por esto mismo esta tecnología ha sido

enfocada a ventas a nivel de empresa y equipos

de gama alta.

¿ Por que ?

2.- La utilidad que se le de a la maquina es

muy importante, ya que el usuario debe de

encontrar un nivel optimo en cuanto a calidad -

precio. Y por que pagar mas si realmente no se

le va a sacar partido al cien por cien.

¿ Por que ?

3.- El software utilizado es otro de los factores

importantes, dado que un RISC no utiliza el

mismo software que un CISC. Estos últimos,

por lo general tienen un software mas

asequible.

¿ Por que ?

4.- Dada la compatibilidad hacia atrás de la

familia CISC x86, los usuarios han podido

renovar sus equipos sin por ello tener que

abandonar software que ya conocían, y reutilizar

sus datos. Así mismo, los fabricantes han tenido

en cuenta este factor, puesto que seguir con otra

línea de procesadores suponía no solo un

cambio muy radical, sino que además podía

llevar un riesgo en cuanto a ventas.

Gracias por tu atención

Вам также может понравиться

- CachéДокумент4 страницыCachéAlma PartidaОценок пока нет

- Actividad4 - Arquitectura de ComputadorasДокумент8 страницActividad4 - Arquitectura de ComputadorasAreGarciaCayetano20% (5)

- Arquitectura de ComputadorasДокумент21 страницаArquitectura de ComputadorasThenayarb 21Оценок пока нет

- Microsoft Exchange Server 2019Документ9 страницMicrosoft Exchange Server 2019Cristhian HS BeochoОценок пока нет

- PROTOTIPOДокумент13 страницPROTOTIPOFrancisco Perez LaraОценок пока нет

- TecnologiasДокумент39 страницTecnologiasFrancisco Perez LaraОценок пока нет

- TecnologiasДокумент39 страницTecnologiasFrancisco Perez LaraОценок пока нет

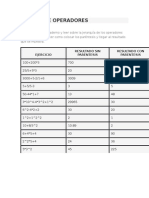

- Ejercicios de OperadoresДокумент1 страницаEjercicios de OperadoresFrancisco Perez LaraОценок пока нет

- InvДокумент3 страницыInvFrancisco Perez LaraОценок пока нет

- Estructura de Datos IIДокумент25 страницEstructura de Datos IIFrancisco Perez LaraОценок пока нет

- Ciber CafeДокумент3 страницыCiber CafeMin Eung-YeongОценок пока нет

- Trabajo Monográfico Sistemas Digitales 1.Документ29 страницTrabajo Monográfico Sistemas Digitales 1.CHRISTIANM GRENOLD MONTENEGRO QUISPEОценок пока нет

- Politicas de BusquedaДокумент8 страницPoliticas de BusquedaBoris AndinoОценок пока нет

- Arquitectura de Los MicroprocesadoresДокумент32 страницыArquitectura de Los MicroprocesadoresEinie VegaОценок пока нет

- Examen - (AAB01) Cuestionario 2 - Conteste Las Preguntas Del Cuestionario en Línea 2, Referente Al Sistema de Memoria y La CPUДокумент5 страницExamen - (AAB01) Cuestionario 2 - Conteste Las Preguntas Del Cuestionario en Línea 2, Referente Al Sistema de Memoria y La CPUFausto MestanzaОценок пока нет

- Cisc y RiscДокумент21 страницаCisc y RiscCosme MagañaОценок пока нет

- Unidad 3 Sistemas Operativos (DJC81)Документ20 страницUnidad 3 Sistemas Operativos (DJC81)jua carlosОценок пока нет

- Andres Castro Fase 2Документ7 страницAndres Castro Fase 2Jesus Antonio Duran AcevedoОценок пока нет

- Evaluacion Arquitectura de ComputadoresДокумент11 страницEvaluacion Arquitectura de ComputadoresRoberto ReinaОценок пока нет

- Finales Resueltos de Sistemas OperativosДокумент288 страницFinales Resueltos de Sistemas OperativosgerОценок пока нет

- Tema 5. Memorias: Estructura de ComputadoresДокумент12 страницTema 5. Memorias: Estructura de ComputadoresALONSO_007Оценок пока нет

- Tipos de Memoria FULLДокумент7 страницTipos de Memoria FULLstvanОценок пока нет

- Tarea de Daniela Alejandra Marin Elias 21-06-22Документ6 страницTarea de Daniela Alejandra Marin Elias 21-06-22Daniela alejandra Elías mayoОценок пока нет

- Glosario de Derecho InformaticoДокумент8 страницGlosario de Derecho InformaticoIsc David MorenoОценок пока нет

- Glosario: IBM DB2 Universal DatabaseДокумент163 страницыGlosario: IBM DB2 Universal DatabaseAlvaro Herrera GonzalezОценок пока нет

- Flujo Falla de Aplicaciones Ilimitadas v4Документ42 страницыFlujo Falla de Aplicaciones Ilimitadas v4margv93.margvОценок пока нет

- Administración Oracle S1 PDFДокумент15 страницAdministración Oracle S1 PDFUber Jesus Teran SosaОценок пока нет

- Clases y Tipos de Memoria CachéДокумент4 страницыClases y Tipos de Memoria CachéJulián NavarroОценок пока нет

- Monografia - MemoriaДокумент14 страницMonografia - MemoriaMatias LupaОценок пока нет

- DmaДокумент10 страницDmaJosemaría VilledaОценок пока нет

- Esquema Tipos de Memoria de La Computadora - MaríaJosé FonsecaДокумент1 страницаEsquema Tipos de Memoria de La Computadora - MaríaJosé FonsecaVioleta FonsecaОценок пока нет

- Componentes de La PCДокумент61 страницаComponentes de La PCLuis Ricardo De la luz VillanuevaОценок пока нет

- Marco Teorico Aquitectura de ComputadorasДокумент47 страницMarco Teorico Aquitectura de ComputadorasDiego AlessandroОценок пока нет

- Pitidos Similares Entre BiosДокумент6 страницPitidos Similares Entre BiosAndrixeros100% (1)

- Ut2 SomДокумент43 страницыUt2 SomLopez luisОценок пока нет

- Como Funcionan Los Sistemas OpeativosДокумент14 страницComo Funcionan Los Sistemas OpeativosguilhangОценок пока нет