Академический Документы

Профессиональный Документы

Культура Документы

Aula Transitor

Загружено:

lucianolnlОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Aula Transitor

Загружено:

lucianolnlАвторское право:

Доступные форматы

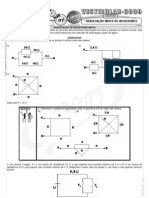

Semicondutores - Transistores

Transistores de Juno Bipolar - TJB

Bipolar Junction Transistor BJT

Transistores MOSFET

Fabricao

V

0

I

D

-V

0

I

R

Fluxo reverso

Fluxo direto

Tenso, V

C

o

r

r

e

n

t

e

,

I

Ruptura

+

+

-

-

Curva corrente-tenso para

uma juno semicondutora

I

D

I

R

Diodo Zener

Diodo

Retificao com uma juno

semicondutora

I

D

I

R

T

e

n

s

o

V

0

-V

0

C

o

r

r

e

n

t

e

I

D

I

R

Tempo Tempo

O transistor

Transistor = amplificador

Transistor = interruptor

Os dois principais tipos de transistores so os

de juno e os MOSFET (metal-oxide-semiconductor

field effect transistor)

O transistor de juno

Duas junes p -n em configuraes p-n-p ou n-p-n.

Base

n

Emissor

p

Coletor

p

Base

p

Emissor

n

Coletor

n

Silcio tipo p

Silcio tipo n

emissor

base

coletor

O transistor pnp

Carga

tenso

de

sada

tenso

de

entrada

T

e

n

s

o

d

i

r

e

t

a

T

e

n

s

o

r

e

v

e

r

s

a

T

e

n

s

o

d

e

e

n

t

r

a

d

a

(

m

V

)

0,1

T

e

n

s

o

d

e

s

a

d

a

(

m

V

)

10

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

-

-

-

-

-

-

buracos buracos

buracos

B V

0 C

E

e I I

/

Base

n

Emissor

p

Coletor

p

O transistor pnp

V

E

I

C

I

0

, B = constantes

O transistor MOSFET

Si tipo P

Fonte

Si tipo n

Dreno

Si tipo n

Isolante, SiO

2

Porta

- - - - - -

- - - - - -

V

entrada

V

sada

- +

+

50 nm

V

entrada

= 0 V

sada

= 0

Transistor = interruptor (sistema binrio)

O transistor MOSFET

Transistor de juno bipolar

Sedra & Smith, 4

a

edio, captulo 4

http://ece-www.colorado.edu/~bart/book/book/toc5.htm

Transistor npn

Figura 4.1 Estrutura simplificada do transistor npn.

Transistor de juno bipolar (2)

Transistor pnp

Figura 4.2 Estrutura simplificada do transistor pnp.

Dependendo da polaridade da tenso aplicada em cada

juno, obtm-se diferentes modos de operao do TJB.

Smbolos de circuito e convenes

i

C

i

E

Indica a direo da

polarizao direta da

juno BE.

Figura 4.10 Polaridade das tenses

e fluxo de corrente nos transistores

polarizados no modo ativo de

operao ( v

BE

(ou v

EB

) >0 e v

CB

(ou

v

BC

) 0 ).

Trs zonas tipicas de operao (modos de

operao)

Zona de corte Ambas as junes de corte

Zona de ativa

Zona de ativa Juno B-E ON Juno B-C

OFF

Zona de saturao Ambas as junes ON

Modos de operao do TJB npn

http://ece-www.colorado.edu/~bart/book/book/chapter5/ch5_3.htm e Sedra.

Modo JEB JCB

Cortado Reverso Reverso

Ativo Direto Reverso

Saturao Direto Direto

Amplificadores com TJB

Ligado baixa impedncia

Saturado

Liga/Desliga: circuitos lgicos

Desligado elevada impedncia

Cortado (v

BC

e v

BE

reversam. pol.)

Pequena corrente reversa.

A funo do emissor e do coletor

so invertidas (TJB no so normalmente

simtricos).

Relaes corrente-tenso do TJB no

modo ativo de operao

T BE

V v

S C

e I i

/

T BE

V v

S C

B

e

I i

i

/

,

_

. por substitua , r transisto o Para : Obs

/

EB BE

T BE

v v pnp

V v

S C

E

e

I i

i

,

_

( )

( )

B E B C

E

E B E C

i i i i

i

i i i i

1

1

1

+

+

1

1 +

ambiente ra temperatu na

trmica tenso

mV 25

q

kT

V

T

Transistor n-p-n

Semelhante a dois dodos costas com costas, mas,

Largura de base, W, muito pequena!

n p n

Base

Emissor Coletor

Juno base-emissor

Juno base-coletor

W

Operao do transistor npn na regio ativa

Figura 4.3 Fluxo de corrente em um transistor npn polarizado de modo a operar na

regio ativa. (Componentes de corrente reversa devido ao movimento de deriva de

portadores minoritrios gerados termicamente no esto mostrados.)

Esto mostrados apenas os componentes da corrente de difuso.

Funcionamento na Zona Ativa

Na zona ativa temos a juno BE polarizada diretamente e a juno

BC polarizada inversamente

Os eltrons responsveis pela conduo de corrente na juno base

emissor atravessam a pequena base e so recolhidos no coletor!

n p n Emissor

Coletor

Base

Juno Polarizada

diretamente

Juno Polarizada

inversamente

I

A Juno BE emite eltrons que

se deslocam para o coletor

Ic

Ie

Ib

Funcionamento na Zona Ativa

Porque que os eltrons no so bloqueados pela juno base

coletor?

Porque como a base muito fina a velocidade dos eltrons suficiente para

que os eltrons cheguem ao lado n antes de colidirem com outras particulas

(nucleos ou lacunas).

Os que ficam pelo caminho vo formar parte da corrente na base.

Assim temos que a corrente no coletor ser aproximadamente igual

corrente no emissor (Ic Ie) e que a corrente a base ser muito pequena

(Ib<<Ic)

De fato temos que Ic proporcional a Ib,

Ic =

Ic =

Ib

Ib, com >>1

n p n

Emissor

Coletor

Base

Juno Polarizada

diretamente

Juno Polarizada

inversamente

I

A Juno BE emite eltrons que se

deslocam para o coletor

Ic

Ie

Ib

Transistor npn na regio ativa

Tenso direta v

BE

: corrente i

C

(dependncia exponencial

com v

BE

) flui no terminal de coletor.

i

C

independe da tenso do coletor contanto que v

CB

0.

Na regio ativa de operao, o terminal de coletor

comporta-se como uma fonte de corrente constante ideal,

em que o valor da corrente determinada por v

BE

.

i

B

= i

C

/ ; i

E

= i

C

+ i

B

i

B

<< i

C

( >>1) i

E

i

C

(i

C

= i

E

, < 1, mas 1)

Perfil da Densidade de Portadores

A densidade de eletrons livres decresce na base. No coletor os eletrons livres so

removidos pelo campo eltrico.

Como a base tem um comprimento bastante inferior ao comprimento de difuso este

decrscimo linear.

A base (tipo-p) bastante menos dopada que o emissor (tipo-n) logo a concentrao

de lacunas bastante inferior concentrao de eletrons livres.

O Campo eltrico

remove os eletrons

livres

W

Largura efetiva de base

Linear j que

W << Ld

Emissor (n)

Base (p)

Coletor (n)

) 0 (

p

n

) (x n

) (x p

Vbe

Vcb

I

Concentrao dos portadores minoritrios

Figura Perfis das concentraes de portadores minoritrios na base e no emissor de

um transistor npn operando no modo ativo: v

BE

> 0 and v

CB

0.

n

coletor

= 0 JBC diretamente

polarizada

T BE

V v

p p

e n n

/

0

) 0 (

Concentrao de Portadores

Minoritrios na Base de um

Transstor Saturado

T BE

V v

p

e n

/

0

T BC

V v

p

e n

/

0

Zona Ativa Zona Ativa

inversa

Zona

Saturao

Grande quantidade de carga

Armazenada na base

Tempos elevados para a

saida da regio de saturao

Corrente majoritria

O emissor (tipo-n) muito mais dopado que a base (tipo-p)

donde resulta que a corrente maioritariamente formada por

eltrons livres, que se deslocam diretamente do emissor para o

coletor!

T

BE

v

v

p p

e n n

0

) 0 (

W

n

D q A

x d

x n d

D q A i i

p

n E

p

n E n C

) 0 (

) (

T BE

v v

A

i n E

C

e

W N

n D q A

i

/

2

A

i

p

N

n

n

2

0

A tenso Vbe aumenta

com a concentrao de

eltrons livres no emissor

Emissor (n)

Base (p)

Coletor (n)

) 0 (

p

n

) (x n

) (x p

Vbe

Vcb

I

Corrente majoritria

O Transstor na zona ativa comporta-se como um dodo

polarizado diretamente com uma corrente de saturao

dada por Is, mas a corrente fli num terceiro terminal

denominado de coletor!

T BE

v v

S C

e I i

/

W N

n D q A

I

A

i n E

S

2

Emissor (n)

Base (p)

Coletor (n)

) 0 (

p

n

) (x n

) (x p

Vbe

Vcb

I

Corrente na base

A corrente da base tem dois

componentes:

i

B1

= Corrente minoritria devido s lacunas

que se deslocam da base para o emissor.

Equao equivalente corrente de lacunas de

uma juno p-n.

T BE

v v

p D

i p E

B

e

L N

n D q A

i

/

2

1

B

n

B

Q

i

1

W n q A Q

p E n

) 0 (

2

1

T BE

V v

A B

i E

B

e

N

n W q A

i

/

2

2

2

1

2 1 B B B

i i i +

i

B2

= Corrente de reposio dos eletrons que se recombinam com as lacunas ao

atravessarem a base.

Carga

armazenada

na base

Tempo mdio que um eletron

demora at se recombinar com

uma lacuna

A corrente de base i

B

Componente i

B1

(lacunas injetadas da base para a regio do

emissor):

Componente i

B2

(lacunas que devem ser fornecidas pelo circuito

externo de modo a repor as lacunas perdidas na base pelo processo

de recombinao):

T BE

V v

P D

i p E

B

e

L N

n D q A

i

/

2

1

D

p

: difusividade das lacunas no emissor;

L

p

: comprimento de difuso de lacunas no emissor;

N

D

: concentrao de dopantes no emissor.

T BE

V v

A b

i E

b

n

B

e

N

n W q A Q

i

/

2

2

2

1

b

: tempo de vida do portador minoritrio

Q

n

: carga do portador minoritrio na base.

A corrente de base i

B

(2)

: ganho de corrente com emissor comum (usualmente,

100 < < 200).

Para obter um elevado valor de (desejvel), a base

deve ser fina (W pequeno) e levemente dopada e o

emissor fortemente dopado (N

A

/ N

D

pequeno).

T BE

V v

S C

B B B

e

I i

i i i

/

2 1

,

_

,

_

+

b n P D

A

n

p

D

W

L

W

N

N

D

D

2

1

1

2

Constante para um transistor

em particular (no caso ideal)

Ganho de corrente do Transstor

Deve-se notar que:

Beta aumenta com a diminuio da largura da base

Beta aumenta com a concentrao de impurezas no emissor e

diminui com a concentrao de impurezas na base.

Beta normalmente considerado aproximadamente constante

para um dado transstor apesar de variar com vrios fatores

B C

i i

B n P D

A

n

p

D

W

L

W

N

N

D

D

2

2

1

1

+

Temos ainda a

relao de Einstein:

2

n B n

L D

Combinando as equaes anteriores

A corrente de coletor i

C

Corrente de difuso de eltrons I

n

:

A corrente de coletor i

C

= I

n

:

Observe que a magnitude de i

C

independe de v

CB

(contanto que seja 0).

,

_

,

_

W

n

D q A

dx

x dn

D q A I

p

n E

p

n E n

) 0 (

) (

T BE

V v

S C

e I i

/

A

i

n E

p

n E S

N W

n

D q A

W

n

D q A I

) 0 (

2

0

I

S

: fator de escala de corrente

A corrente de emissor i

E

: constante para um transistor em particular

(idealmente), < 1 (se, por ex., = 100 0,99).

Pequenas variaes em correspondem a grandes

variaes em .

: ganho de corrente em base comum.

T BE

V v

S C B C E

e I i i i i

/

1

1

,

_

,

_

+

+

+

1

,

1

,

E C

i i

T BE

V v

S

E

e

I

i

/

,

_

Equaes para as correntes (zona

ativa)

C B E

i i i +

T BE

v v

S C

e I i

/

B C

i i

n

p

n

Emissor

Coletor

Base

Ic

Ie

Ib

B B B E

i i i i ) 1 ( + +

E C

i i

1 +

Ib

Ie

Ic

Temos ainda:

C

J

Capacitncia de juno ou depleo

C

d

Capacitncia de difuso

d J

C C C +

'

,

_

m A

m diff

m A

m

diff A

J

m A

m

diff A

J

J

V V

V V

V V

m

V V

C

V V

V V

C

C

, 1

1

,

1

0

0

( )

T

V

T

T S

d

nV e

nV

I

C

A

T

tempo de transio

Modelos de circuitos equivalentes

Diodo D

E

: fator de escala de corrente = I

S

/ fornece a corrente

i

E

relacionada a v

BE

conforme as equaes anteriores.

Fonte de corrente no-linear controlada por tenso (grandes sinais).

Pode-se convert-la em uma fonte de corrente controlada por

corrente expressando-se a corrente da fonte controlada por i

E

.

B: terminal comum (terra) : ganho de corrente de E para C.

Estrutura fsica simplificada

Figura 5.6 Seo transversal de um TJB npn.

Smbolo

O smbolo do transistor npn baseado no

seu modelo equivalente

Ib

Ie

Ic

emissor

coletor

base

B

E

C

Modelos equivalentes (npn)

T BE

V v

S C

e I i

/

T BE

V v

S C

e I i

/

E C

i i

/

C B

i i

T BE

V v

S

E

e

I

i

/

T BE

V v

S

B

e

I

i

/

B C

i i

B

B

B

B

C

C

C

C

E

E

E

E

/

C E

i i

O transistor pnp

Figura 4.7 Fluxo de corrente em um transistor pnp polarizado de modo a operar no

modo ativo.

O transistor pnp circuitos

equivalentes (grandes sinais)

Figura 4.8 Dois modelos de grandes sinais para o transistor pnp operando no modo

ativo.

B C

E

i

B

i

C

i

E

T EB

V v

S

e I

/

( ) /

S

B

I

D

+

v

EB

Transstor pnp

O emissor injeta lacunas na base que passam

diretamente para o coletor.

As equaes so semelhantes s do transstor

npn mas mudam os sentidos das correntes e

troca-se Vbe por Veb.

p n p

Base

Emissor Coletor

W

Ib

Ie

Ic

emissor

coletor

base

T EB

v v

S C

e I i

/

B C

i i

Modelos equivalentes (pnp)

T EB

V v

S C

e I i

/

E C

i i

/

C B

i i

T EB

V v

S

E

e

I

i

/

T EB

V v

S

B

e

I

i

/

B C

i i

/

C E

i i

B

C

E

T EB

V v

S C

e I i

/

B

C

E

B

C

E

B

C

E

Funcionamento na Zona Ativa

VCE

VBE

Ic

Ib

Ie

npn

T BE

V v

S C

e I i

/

pnp

VEC

VEB

Ie

Ic Ib

E C

i i

B C

i i

) 1 /( +

T EB

V v

S C

e I i

/

V V

CE

2 . 0 >

V V

EC

2 . 0 >

JBE ON

JBE ON

Zona de Saturao

A juno Base-Coletor comea a conduzir para Vbc=0.5V de onde resulta

que na entrada na zona de saturao podemos considerar Vce=0.2

0.5V

0.7V

0.2V

C

B

E

Modelo para o transstor na zona de saturao

Modelo simplificado

0.7V

0.2V

C

B

E

C

B

E

Zona de Saturao

Utilizando o modelo de Ebers Moll

podemos chegar a seguinte frmula para a

regio de saturao.

F forced

R forced

T CESat

V V

/ 1

/ ) 1 ( 1

ln

+ +

forced

50 48 45 40 30 20 10 1 0

V

cesat

(mV)

235 211 191 166 147 123 76 60

B

C

forced

I

I

10 20 30 40

50

100

150

200

250

V

c

e

S

a

t

(

m

V

)

forced

F forced

<

Exemplo: =50

Curvas Caractersticas dos

Transstores

Zona Ativa

V2

V 22

Q2

N 22222

I2

uA 22

Ib=60uA

Ib=20uA

Vce (V)

I

c

(

A

)

I

c

I

e

Zona Ativa Inversa

Zona Ativa Inversa

O transstor um dispositivo aproximadamente simtrico, de tal forma

que se trocarmos o emissor com o coletor obtemos um novo dispositivo,

que continua a funcionar como um transstor.

No entanto o coletor em geral menos dopado que o emissor, donde

resulta que o novo (

R

) bastante mais pequeno.

Trocar o emissor com o colector corresponde utilizar um valor de V

CE

negativo.

T BC

V v

S E

e I i

/

V V

EC

2 . 0 >

JBC ON

I

b

V

CE

V

BE

C R E

i i

B R E

i i

Curvas Caractersticas

<<

R

Zona ativa

inversa

Zona ativa

Zona saturao

Variao de beta com a corrente

0

50

100

150

200

0,0000001 0,00001 0,001 0,1 10 1000

Ic (A)

b

e

t

a

grandes variaes de corrente provocam variaes do beta

O Efeito da Temperatura

Vbe varia cerca de

2mV/C para valores

semelhantes de Ic

Beta do transstor

tipicamente aumenta com a

temperatura

V2

12V

Q1

2N3903

V1

1V

Sensibilidade Temperatura

0

0,2

0,4

0,6

0,8

1

1,2

0 0,2 0,4 0,6 0,8 1

Vbe (V)

I

c

(

A

)

0C

27C

60C

Efeito de Early

Mesmo na zona ativa existe uma pequena

dependncia de Ic com Vce. Tal deve-se a

uma diminuio da largura efectiva da

regio de base, devido ao alargamento da

regio de depleo da juno CE. Efeito de

Early.

V2

12V

Q1

2N3903

I1

50uA

VA

Tenso de

Early

,

_

+

A

ce

v v

S c

V

v

e I i

T BE

1

/

Modelo de pequenos sinais

r

Modelo

Modelo T

B

C

E

+

-

v

B C

i i .

B

C

E

BE C

v gm i .

e

r

T

C

V

I

gm

gm I

V

r

B

T

T

C

V

I

gm

E

T

e

I

V r

r

+

E C

i i

v gm i

C

.

Nota:

BE

v v

Incorporando o efeito de Early

r

Modelo aumentado

B

C

E

+

-

v

C

A

O

I

V

r

O

r

ro modela o efeito de Early.

Pode ser considerado

como a resistncia de

sada da fonte de corrente.

Configuraes de Amplificao de um

nico Andar

Q1

I1

Rs

V1

Rc

Vcc

Vee

Vo

Q1

I1

Rs

V1

Vcc

Vee

Ce

Vo

Rl

Q1

I1

Rs

V1

Rc

Vcc

Vee

Vo

Montagem emissor

comum

Montagem coletor

comum ou seguidor de

emissor

Montagem base

comum

Montagem Emissor Comum

Q1

I1

Rs

V1

Rc

Vcc

Vee

Vo

r R

I

( )

C O O

S

i

R r v gm v e

r R

r

v v // .

O C O

r R R //

( )

C O

S

V

R r

r R

r

gm A //

,

_

C V

R gm A

+

C O

O

I

R r

r

A

Modelo de pequenos sinais

Usa-se para ter

Ganho de tenso

Rs

Vi

Rpi ro Rc

gm vpi

-

vpi

+

io

ib

Ri

Ro

Emissor Comum Degenerado

Q1

I1

Rs

V1

Rc

Vcc

Vee

Vo

Re

Modelo de pequenos sinais

( )

E I

R r R 1 + +

C O

R R

( ) ( )

E

C

E e S

C

V

R

R

R r R

R

A

+ + +

1

I

A

Rs

Vs

Rc

Vo

re

Re

Ri

Ro

.ie

+

-

v

Ii

Io

Q1

I1

Rs

V1

Vcc

Vee

Ce

Vo

Rl

Montagem Coletor Comum

ou Seguidor de Emissor

Rs

V1

Vo

Rl

re

ro

Modelo de pequenos sinais

( ) ( )

L o e I

R r r R // 1 + +

e

S

e O O

r

R

r r R

,

_

+

+

1

//

1

1 1

//

//

+

+

+

+ +

+

S

L

L

S

L o e

L o e

V

R

R

R

R

R r r

R r r

A

( )

L O

O

I

R r

r

A

+

+ 1

Ri

Ro

Io

Nota:

calcularam-se os ganho

de corrente e tenso

com carga

Usa-se para ter Ganho de corrente

Montagem Base Comum

Q1

I1

Rs

V1

Rc

Vcc

Vee

Vo

Rs

Vi

re

Vo

Rc

Ri

Ro

i

E

e I

r R

C O

R R

e S

C

V

r R

R

A

+

I

A

O Inversor TJB

Q1

Rs

Vi

Rc

Vcc

Vo

No utilizada em parte

devido s dificuldades

em retirar o transistor da

saturao

Exemplo:

Rb=10k , Rc=1k e =50 e Vcc=5V

V

IL

V

IH

V

OH

V

OL

Zona

Corte

Zona

Activa

Zona

Saturao

0.7V

0.2V

V

R

R V I R V V

C

S B S IH

66 . 1

2 . 0 5

7 . 0 7 . 0

+ +

IH OH H

V V NM

OL IL L

V V NM

Margens de Rudo:

Modelo de Transporte

Base

Coletor

Emissor

Ib

Ie

Ic

( )

( ) 1

1

/

/

T BC

T BE

V v

S

V v

S C

e I

e I I

( )

( ) 1

1

/

/

+

T BC

T BE

V v

R

S

V v

F

S

B

e

I

e

I

I

Uma forma alternativa do

modelo de Ebers-Moll

Beta para pequenos sinais

depende de Ic

AC b c

B

C

ef

i i

i

i

h

/

ef ef

h h mas ,

( )

) ( ). ( '

). (

B B B

B

B B

B

C

ef

i i i

i

i i

i

i

h

Valor redusido

Beta corresponde a

secante curva, e h

ef

tangente curva!

Efeitos capacitivos no TJB

Capacidade de

difuso ou de carga

na base

(zona ativa)

Capacitncia da

juno base emissor

Capacitncia da

juno base coletor

C F C

n

n

i i

D

W

Q

2

2

T

C

F de

V

I

C

m

OE

BE

je

je

V

V

C

C

,

_

1

0

0

2

je je

C C

m

OC

BC

V

V

C

C

,

_

1

0

0

2

C C

Juno ao corte

Juno em conduo

de fe

C C C +

Modelo de Alta frequncia

( )

+ +

r C C s

h

fe

1

0

rx

r

C

C

ro

C

E

B

0

f f

t

h

fe

Q1

Vcc

Circuito para

determinao do beta

Variao de h

fe

com a frequncia

( )

C C

gm

f

T

+

2

Este modelo s

vlido at cerca de

0.2 f

t

T

fe

f

f

h

0

0

1

Modelo do SPICE

RC Resistncia ohmica do colector

RE Resistncia ohmica do emissor

TR Tempo de transito inverso ideal

TF Tempo de transito directo ideal

VAR Tenso de Early inversa

NR Coeficiente de emisso inverso

BR Ganho de corrente inverso mximo

VAF Tenso de Early directa

NF Coeficiente de emisso directo

BF Ganho de Corrente directo mximo

IS Corrente de Saturao

S

I

F

n

A

V

R

F

R

e

r

c

r

VJS Tenso intrinseca da juno CS

MJS Coeficiente de gradiente da juno CS

CJS Capacidade da juno CS (Pol nula)

VJC Tenso intrinseca da juno BC

MJC Coeficiente de gradiente da juno BE

CJC Capacidade da juno BC (Pol nula)

VJE Tenso intrinseca da juno BE

MJE Coeficiente de gradiente da juno BE

CJE Capacidade da juno BE (Pol nula)

RB Resistencia ohmica da base (Pol nula)

x

r

0 je

C

0 be

m

Oe

V

0

C

0 bc

m

Oc

V

0 cs

C

rx

r

C

C

ro

C

E

B

C

CS

S

i

C

Exemplo 4.1

O transistor na figura tem = 100 e exibe uma tenso v

BE

de 0,7V

com i

C

= 1 mA. Projete um circuito de modo que uma corrente de 2

mA flua atravs do coletor e que uma tenso de + 5V aparea no

coletor.

Exemplo 4.1 - soluo

V

C

= +5 V V

R

C

= 15 5 = 10 V

I

C

= 2 mA V

R

C

= 10 V / 2 mA = 5 k

v

BE

= 0,7 V com i

C

= 1 mA

v

BE

com i

C

= 2 mA dado por:

V 717 , 0

1

2

ln 7 , 0

,

_

+

T BE

V V

V

B

= 0 V

E

= 0,717 V

= 100 = 100/101

I

E

= I

C

/ = 2 / 0,99 = 2,02 mA

R

E

= (VE ( 15)) / I

E

= 7,07 k

Representao grfica das

caractersticas do transistor

Figura 4.12 A caracterstica i

C

v

BE

de um transistor npn

(igual curva i-v do diodo, exceto pelo valor da constante

n).

As caractersticas i

E

-v

BE

e i

B

-v

BE

so tambm

exponenciais, mas com diferentes correntes de escala:

I

S

/ para i

E

e I

S

/ para i

B

.

Para anlises dc rpidas de primeira ordem,

normalmente assume-se que V

BE

0,7V.

Para um transistor pnp, a caracterstica i

C

v

EB

ser

idntica da figura.

A tenso na juno emissor-base decresce de,

aproximadamente, 2 mV para cada acrscimo de 1

o

C na

temperatura (para uma corrente de juno constante).

Figure 4.13 Efeito da temperatura na caracterstica i

C

v

BE

. Para uma corrente de emissor constante (linha

tracejada), v

BE

varia na taxa de 2 mV/C.

T BE

V v

S C

e I i

/

Transistor npn: i

C

v

CB

(por i

E

)

Modo ativo de operao (v

CB

0).

Figura 4.14 A caracterstica i

C

v

CB

de um transistor npn.

E C

i i

Dependncia de i

C

com a tenso de

coletor o efeito Early

Modo ativo de

operao TJBs

mostram uma certa

dependncia com

da corrente de

coletor com a

tenso de coletor.

Suas caractersticas

i

C

v

CB

no so

linhas retas

horizontais.

Figura 4.15 (a) Circuito conceitual para a medio da caracterstica i

C

v

CE

do TJB.

(b) A caracterstica i

C

v

CE

de um TJB usual.

Dependncia de i

C

com a tenso de

coletor o efeito Early (2)

v

BE

> 0.

v

CE

pequeno (v

C

< v

B

) J

CB

:

polarizao direta regio de

saturao.

v

CE

v

CB

< 0 J

CB

: pol. reversa

espessura da regio de

depleo na J

CB

W

EFETIVA DA BASE

I

S

i

C

: efeito Early.

Relao linear de i

C

com v

CE

: assumindo que I

S

permanece constante:

,

_

+

A

CE

V v

S C

V

v

e I i

T BE

1

/

Inclinao no-nula das linhas

retas i

C

v

CE

: a impedncia de

sada do coletor no infinita

Dependncia de i

C

com a tenso de

coletor o efeito Early (3)

Inclinao no-nula das linhas retas i

C

v

CE

a impedncia de

sada do coletor finita e definida por:

Da equao anterior: r

o

V

A

/ I

C

I

C

: o nvel da corrente correspondendo ao valor constante de v

BE

prximo fronteira da regio ativa.

Esta dependncia de i

C

com v

CE

no projeto e anlise do circuito de

polarizao normalmente no considerada; no entanto, a

resistncia de sada finita r

o

pode ter um efeito significativo no

ganho de amplificadores a transistores.

1

constante

1

1

]

1

BE

v

CE

C

o

v

i

r

Anlise dc de circuitos com transistores

Modelo da tenso constante V

BE

assuma que V

BE

= 0,7V

independentemente do valor exato da corrente i

C

.

Exemplo 4.2: Considere o circuito da figura. Deseja-se analisar

este circuito de modo a determinar as tenses em todos os ns e as

correntes em todos os ramos. Assuma = 100.

Exemplo 4.2 anlise

O transistor est na regio ativa?

V

B

(em relao ao terra) = 4V ; V

E

= V

R

E

< 4V (assumindo o modo

ativo de operao, h uma queda V

BE

de 0,7 na J

BE

) A juno BE

est diretamente polarizada.

V

E

= 4 V

BE

4 0,7 = 3,3 V

V

R

E

= V

E

= 3,3 V I

E

= V

E

/ R

E

= 1 mA .

V

C

= 10 V I

C

R

C

; V

B

= 4V

Vamos assumir que V

BC

< 0: regio ativa de

operao (juntamente com a condio V

BE

> 0).

Assim: I

C

= I

E

= / (+1) = 100/101 0,99

I

C

= 0,99 1 = 0,99 mA.

V

C

= 10 I

C

R

C

= 10 0,99 4,7 +5,3 V: V

BC

= 1,3V ()

Exemplo 4.2 anlise (2)

V

BE

> 0 , V

BC

< 0: O transistor est na regio ativa?

I

B

= I

E

/ ( + 1) = 1 / 101 0,01 mA.

Condies consistentes O transistor est na regio ativa!

Exemplo 4.3

Analise o circuito da figura e determine as tenses em todos

os ns e as correntes em todos os ramos. Assuma = 100.

O transistor est na regio ativa? Assuma, inicialmente, operao

na regio ativa.

O transistor est

no modo de saturao

(visto mais adiante).

Exemplo 4.4

Analise o circuito da figura e determine as tenses em todos

os ns e as correntes em todos os ramos. Assuma = 100.

O transistor est na regio ativa? V

B

= 0V J

BE

no conduz

(V

BE

< 0) i

E

= 0 ; V

C

= 10 I

C

4,7k > V

B

= 0 J

BC

no conduz

(V

BC

= 0 V

C

< 0) i

C

= 0 i

B

= i

C

i

E

= 0

O transistor est no modo cortado de operao.

Exemplo 4.5

Analise o circuito da figura e determine as tenses em todos

os ns e as correntes em todos os ramos. Assuma = 100.

Observe que o transistor agora pnp!

Exemplo 4.6

Analise o circuito da figura e determine as tenses em todos

os ns e as correntes em todos os ramos. Assuma = 100.

O transistor est no modo ativo?

Exemplo 4.7

Analise o circuito da figura e determine as tenses em todos

os ns e as correntes em todos os ramos. Assuma = 100.

O transistor est no modo ativo?

Exemplo 5.9 5

a

edio do Sedra&Smith

Analise o circuito da figura e determine as tenses em todos

os ns e as correntes em todos os ramos. Assuma = 100.

Exemplo 4.8

Analise o circuito da figura e determine as tenses em todos

os ns e as correntes em todos os ramos. Assuma = 100.

Sobre construo de

dispositivos

semicondutores e

circuitos integrados

5.1 TIPOS DE DIODOS 5.1 TIPOS DE DIODOS

5.1.1 Diodo de Juno

1

0

T A

V V

e I I

5.1.2 Diodo Schottky

( )

1

0

T

S

R I

A

V

V

e I I

5.1.3 Diodo PIN

1

2

T A

V V

S

e I I

5.1.4 Diodo IMPATT

5.1.5 Diodo Tnel

5.2.2 Modelo Linear do Diodo (pequenos sinais)

T

Q

T

S Q

V

A

D

d

d

nV

I

nV

I I

dV

dI

R

G

Q

+

1

5.3 TRANSISTOR BIPOLAR DE JUNO 5.3 TRANSISTOR BIPOLAR DE JUNO

Construo interdigital

Diminuir a resistncia

base-emissor

Reduz o rudo trmico

Alta potncia

TRANSISTOR BIPOLAR DE HETEROJUNO

Alto ganho de corrente

sem necessidade de

dopar excessivamente o

emissor

Aumento da injeo de

portadores devido s

camadas adicionais de

semicondutor

Altas freqncias de

operao (100 GHz)

Exemplo de Projeto

Substrato

Os transstores nos circuitos integrados modernos so

em geral construdos atravs da adio de impurezas a

uma bolacha de semicondutor.

Bolacha de

Silcio

Transstor

Corte

vertical

Transstor planar

Transstor vertical

E

B C E

B C

Substrato de Silcio

p

n

n n

n p

Contatos

metlicos

5.5 TRANSISTORES DE EFEITO DE CAMPO 5.5 TRANSISTORES DE EFEITO DE CAMPO

5.5.1 Tipos de FETs

MOSFET

Transistor MOSFET

MOSFET (Metal - Oxide - Semiconductor Field Effect

Transistor)

Sao circuitos integrados com alta escala de integracao;

baixo consumo, dimensoes reduzidas,etc

Existem duas variedades de transistores MOSFETs,

conforme o tipo dos portadores existentes no canal: n ou p.

Transistores de canal n baseiam a sua conducao eletrica

em portadores negativos, eletrons, tal como ocorre na

conducao eletrica dos metais

Transistores de canal p, a conducao eletrica acontece

pelo deslocamento de lacunas, com carga positiva.

Transistor MOSFET

Estrutura

fonte

substrato

dreno

porta

Canal n

fonte

substrato

dreno

porta

Canal p

CMOS eh uma associacao em serie destes

dois tipos de transistores, construidos sob

um mesmo substrato

JFET

MESFET

HEMT

5.6 MODELAGEM DO MESFET 5.6 MODELAGEM DO MESFET

Funcionamento

5.6.1 Modelo de Grandes Sinais

Modelo Dinmico

5.6.2 Modelo de Pequenos Sinais

Modelo de alta freqncia

Logic value 1

Undefined

Logic value 0

Voltage

V

DD

V

1,min

V

0,max

V

SS

(Gnd)

Tenso relativas aos nveis lgicos

Nveis Lgicos

0 low baixo Lgica

1 high alto Positiva

0 high alto Lgica

1 low baixo Negativa

Valores Tpicos:

V

DD

= 5 V ou 3.3 V e V

SS

= 0 V

V1,min = 40% V

DD

V0,max = 60% V

DD

Tenso de Threshold (tenso de

limiar) Qualquer tenso acima da

Tenso de Threshold define um

valor lgico, qualquer tenso abaixo

da Tenso de Threshold define um

valor lgico.

Transistor NMOS como uma chave

(a) Uma chave controlada por uma entrada x

x = "low" x = "high"

Gate

Drain Source

(b) Transistor NMOS

Substrate (Body)

MOS Metal Oxide Silicon

NMOS MOS tipo N (canal

N Substrato P)

Gate - Porta

Source Fonte

Drain - Dreno

Susbstrate (body)

substrato

Se V

G

baixo, no h

formao de canal entre

fonte e dreno transistor

no conduz transistor

aberto (turned off)

Se V

G

alto, h formao

de canal entre fonte e dreno

transistor conduz

transistor fechado (turned

on)

V

D

V

S

(c) Smbolo simplificado de um transistor NMOS

V

G

x = "high" x = "low"

(a) Uma chave com comportamento oposto ao do slide anterior

Gate

(b) Transistor PMOS

V

DD

Drain Source

Substrate (Body)

Transistor PMOS como uma chave

PMOS MOS tipo P (canal

P Substrato N)

Gate - Porta

Source Fonte

Drain - Dreno

Susbstrate (body)

substrato

Se V

G

baixo, h formao

de canal entre fonte e dreno

transistor no conduz

transistor fechado (turned

on)

Se V

G

alto, no h

formao de canal entre

fonte e dreno transistor

no conduz transistor

aberto (turned off)

V

G

V

D

V

S

(c) Smbolo simplificado de um transistor PMOS

Transistores NMOS e PMOS em circuitos lgicos

V = V V V

S DD

V

D

V

G

Chave Aberta

quando

V

G

=V

DD

V

D

DD

Chave fechada

quando

V

G

= 0 V

V

D

=V

DD

DD

(b) Transistor PMOS

(a) Transistor NMOS

V

G

V

D

V

S

= 0 V

Chave fechada

quando V

G

=V

DD

V

D

= 0 V

Chave aberta

quando V

G

= 0 V

V

D

x f

(c) Smbolos Grficos

x f

Uma Porta Inversora NOT - construda com tecnologia

NMOS

(b) Diagrama simplificado

V

x

V

f

V

DD

R

V

x

V

f

R

+

-

(a) Diagrama do Circuito

5 V

Vf = 0,2 V quando Vx = 5 V

O resistor um limitador de

corrente (na prtica, outro

transistor)

Porta NAND com tecnologia NMOS

V

f

V

DD

(a) Circuito

(b) Tabela Verdade

x x

0

0

1

1

0

1

0

1

1

1

1

0

1 2

f

V

x

2

V

x

1

(c) Smbolo Grfico

f f

x

1

x

2

x

1

x

2

V

x

1

V

x

2

V

f

V

DD

(a) Circuit

(c) Graphical symbols

(b) Truth table

f

0

0

1

1

0

1

0

1

1

0

0

0

x

1

x

2

f

f

x

1

x

2

x

1

x

2

Porta NOR com tecnologia NMOS

(c) Smbolos Grficos

(a) Circuito

f f

(b) Tabela Verdade

0

0

1

1

0

1

0

1

0

0

0

1

x

1

x

2

f

V

f

V

DD

A

V

x

1

V

x

2

x

1

x

2

x

1

x

2

V

DD

Porta AND com tecnologia NMOS

(a) Circuit

(c) Graphical symbols

(b) Truth table

f

0

0

1

1

0

1

0

1

0

1

1

1

x

1

x

2

f

f

V

f

V

DD

V

x

2

V

x

1

x

1

x

2

x

1

x

2

V

DD

Porta OR com tecnologia NMOS

Estrutura de uma Porta NMOS

V

f

V

DD

Pull-down network

V

x

1

V

x

n

(PDN)

V

f

V

DD

Pull-down network

Pull-up network

V

x

1

V

x

n

(PUN)

(PDN)

Estrutura de uma Porta CMOS

CMOS Complementary MOS

resistor referente porta NOMS

substitudo por uma rede Pull-up

(PUN)

PDN e PUN so duais, se o PDN tiver

transistores NMOS em srie, PUN

ter transistores PMOS em paralelo, e

vice-versa.

(a) Circuito

V

f

V

DD

V

x

(b) Tabela verdade e estados dos transistores

on

off

off

on

1

0

0

1

f x

T

1

T

2

T

1

T

2

Estrutura de uma Porta NOT CMOS

(a) Circuit

V

f

V

DD

(b) Truth table and transistor states

on

on

on

off

0

1

0

0

1

1

0

1

off

off

on

off

off

on

f

off

on

1

1

1

0

off

off

on

on

V

x

1

V

x

2

T

1

T

2

T

3

T

4

x

1

x

2

T

1

T

2

T

3

T

4

Estrutura de uma Porta NAND CMOS

Para f = 1 f = x1x2 = x1 + x2 PUN = 2 transistores PMOS em paralelo

Para f = 0 f = x1x2 PDN = 2 transistores NMOS em paralelo

(a) Circuit

V

f

V

DD

(b) Truth table and transistor states

on

on

on

off

0

1

0

0

1

1

0

1

off

off

on

off

off

on

f

off

on

1

0

0

0

off

off

on

on

V

x

1

V

x

2

T

1

T

2

T

3

T

4

x

1

x

2

T

1

T

2

T

3

T

4

Estrutura de uma Porta NOR

CMOS

Para f = 1 f = x1 + x2 = x1 . x2 PUN = 2 transistores PMOS em srie

Para f = 0 f = x1 + x2 PDN = 2 transistores NMOS em paralelo

V

f

V

DD

V

x

1

V

x

2

V

DD

Estrutura de uma Porta AND CMOS

NAND + NOT

Estrutura de uma Porta CMOS

Exerccio 1

Considere a funo: f = x1 + x2 x3

Ache o circuito CMOS equivalente

Exerccio 2

Considere a funo: f = x1 + (x2 + x3) x4

Ache o circuito CMOS equivalente

V

f

V

DD

V

x

1

V

x

2

V

x

3

Estrutura de uma Porta CMOS Exerccio 1

f = x1 + x2 x3 = x1 (x2 + x3)

V

f

V

DD

V

x

1

V

x

2

V

x

3

V

x

4

Estrutura de uma Porta CMOS Exerccio 2

f = x1 ( x2 x3 + x4)

(a) Circuit

V

f

V

DD

(b) Voltage levels

L

H

L

L

H

H

L

H

H

H

H

L

V

x

1

V

x

2

V

x

1

V

x

2

V

f

Nveis de Tenso em uma Porta Lgica

Interpretao dos Nveis de Tenso Lgica Positiva e Negativa

(b) Tabela Verdade Lgica Positiva e Smbolo

f

0

0

1

1

0

1

0

1

1

1

1

0

x

1

x

2

f

x

1

x

2

V V V

(a) Nveis de Tenso

L

H

L

L

H

H

L

H

H

H

H

L

x

1

x

2

f

1

1

0

0

1

0

1

0

0

0

0

1

x

1

x

2

f

f

x

1

x

2

(c) Tabela Verdade Lgica Negativa e Smbolo

(a) Nveis de Tenso

L

H

L

L

H

H

L

H

L

L

L

H

V

x

1

V

x

2

V

f

(c) Lgica Negativa

1

1

0

0

1

0

1

0

1

1

1

0

x

1

x

2

f

f

x

1

x

2

(b) Lgica Positiva

f

0

0

1

1

0

1

0

1

0

0

0

1

x

1

x

2

f

x

1

x

2

Interpretao dos Nveis de Tenso Lgica Positiva e

Negativa

Circuito Integrado Padro Srie 7400

(b) Estrutura de um Circuito Integrado 7404

(a) Encapsulamento Dual-Line DIP (Dual-Line Package)

V

DD

Gnd

Implementao de f = x

1

x

2

+ x

2

x

3

V

DD

x

1

x

2

x

3

f

7404

7408 7432

Circuito Integrado 74244 - 8 Buffers tri-states

P

i

n

2

P

i

n

4

P

i

n

6

P

i

n

8

P

i

n

1

P

i

n

1

2

P

i

n

1

4

P

i

n

1

6

P

i

n

1

8

P

i

n

1

1

P

i

n

1

3

P

i

n

1

5

P

i

n

1

7

P

i

n

1

9

P

i

n

3

P

i

n

5

P

i

n

7

P

i

n

9

Dispositivos Lgicos Programveis como uma

Caixa Preta

Porta Lgicas

e

chaves

programveis

Entradas

(variveis lgicas)

Sadas

(funes lgicas)

Estrutura geral de uma PLA Programmable Logic Array

f

1

AND plane

OR plane

Input buffers

inverters

and

P

1

P

k

f

m

x

1

x

2

x

n

x

1

x

1

x

n

x

n

Baseado na idia que as funes lgicas

podem ser representadas como uma

soma de produtos plano de ANDs e

plano de ORs

Diagrama, em nvel de portas lgicas, de uma PLA

f

1

P

1

P

2

f

2

x

1

x

2

x

3

Plano OR

Conexes

Plano AND

programveis

P

3

P

4

Exerccio Dizer quais so as respectivas funes f1 e f2.

Desenho esquemtico de uma PLA

x x x

f

1

P

1

P

2

f

2

1 2 3

Plano OR

Plano AND

P

3

P

4

Exemplo de uma PAL Programmable Array Logic

f

1

P

1

P

2

f

2

x

1

x

2

x

3

Plano AND

P

3

P

4

PAL O plano AND

programvel e o Plano OR fixo

Circuito extra de sada de uma PAL

f

1

Para o plano AND

D Q

Clock

Select

Enable

Flip-flop

Unidade de Programao de um PLD

UM PLCC Plastic-Leaded Chip Carrier com soquete

P

r

i

n

t

e

d

c

i

r

c

u

i

t

b

o

a

r

d

Estrutura de CPLD Complex Programmable Logic Device

PAL-like

block

I

/

O

b

l

o

c

k

PAL-like

block

I

/

O

b

l

o

c

k

PAL-like

block

I

/

O

b

l

o

c

k

PAL-like

block

I

/

O

b

l

o

c

k

Interconnection wires

Detalhe de um CPLD

D Q

D Q

D Q

PAL-like block (details not shown)

PAL-like block

Encapsulamento de um CPLD e sua programao

(a) CPLD in a Quad Flat Pack (QFP) package

Printed

circuit board

To computer

(b) JTAG programming

Estrutura de uma FPGA Field Programmable Gate Array

Logic block Interconnection switches

I/O block

I/O block

I

/

O

b

l

o

c

k

I

/

O

b

l

o

c

k

FPGA - lookup table (LUT) de duas entradas

(a) Circuit for a two-input LUT

x

1

x

2

f

0/1

0/1

0/1

0/1

0

0

1

1

0

1

0

1

1

0

0

1

x

1

x

2

(b) f

1

x

1

x

2

x

1

x

2

+ =

(c) Storage cell contents in the LUT

x

1

x

2

1

0

0

1

f

1

f

1

LUT contm clulas que

armazenam, So usadas para

implementar uma funo

lgica

FPGA - lookup table (LUT) de trs entradas

f

0/1

0/1

0/1

0/1

0/1

0/1

0/1

0/1

x

2

x

3

x

1

FPGA - lookup table (LUT) + Flip Flop

Out

D Q

Clock

Select

Flip-flop

In

1

In

2

In

3

LUT

FPGA Programada

0

1

0

0

0

1

1

1

0

0

0

1

x

1

x

2

x

2

x

3

f

1

f

2

f

1

f

2

f

x

1

x

2

x

3

f

Exerccio: D as

funes f, f1 e f2

Duas linhas de um circuito com tecnologia standard-cell

chip

f

1

f

2

x

1

x

3

x

2

Um gate array - sea-of-gates

Exemplo de uma funo lgica em um gate array

f

1

x

1

x

3

x

2

Processos de deposicao

Borrifamento

Este processo ocorre em uma camara com gas

inerte sob baixa pressao. O material a ser

depositado eh instalado e eletricamente

conectado a uma placa metalica e a lamina eh

instalada em outra placa metalica proxima

A diferenca em relacao ao processo de

evaporacao eh que o borrifamento permite

deposicao de qualquer material, condutor ou

isolante, independente do ponto de fusao.

Etapas de construo de CIs

Material semicondutor

Litografia

Dopagem

Oxidacao

Corrosao

Deposicao

Tecnologia de CI

O circuito integrado consiste de uma rede de

componentes eletronicos interligados, fabricado

sobre uma unica peca de material semicondutor.

A fabricacao de transistores, diodos, resistores,

capacitores e condutores de interconexao, usando

apenas elementos simples como (silicio, oxigenio,

aluminio e tracos de outros metais, mostra a

engenhosidade e a complexidade deste campo de

atuacao.

Tecnologia de CI

A superficie de silicio e submetida a varias etapas de

processamento

Elementos simples (silicio, oxigenio, aluminio, outros) sao

depositados e seletivamente removidos em regioes

precisamente delimitadas por mascaras.

Cada camada possui caracteristicas eletricas especificas e

esta alinhada precisamente com as demais acima e abaixo.

As camadas superpostas formam ondulacoes

tridimensionais e as superposicoes comportam-se como os

componentes eletronicos basicos mencionados acima.

Tecnologia de CI

A performance aumenta com a reducao das

dimensoes das estruturas integradas.

Transistores menores e mais proximos entre

si, possibilitam:

conexoes mais curtas,

reducao nas capacitancias parasitas e

aumento na velocidade de chaveamento

Tecnologia de CI

Nao eh possivel descrever em detalhes cada tarefa

devido a sua complexidade;

Os detalhes sao conhecidos apenas pelos

fabricantes e os processos de fabricacao evoluem

continuamente

A fabricacao de CIs exige instalacoes,

equipamentos e insumos extremamente

especializados e de alto custo, alem de uma equipe

de especialistas em constante atualizacao

Material Semicondutor

A base para fabricao de CIs:

lamina de silicio cristalino dopado e com uma das faces

polidas

a lamina eh normalmente adquirida de um dos poucos

fabricantes dedicados a produzir este insumo em escala

mundial

O ponto de partida para fabricacao desta lamina eh:

o cristal de quartzo, SiO

2

, com pelo menos 99,5% de

grau de pureza

Etapa

1

Litografia

Etapa que trata das:

dimensoes das sucessivas camadas,

posicionamento das sucessivas camadas,

alinhamento preciso das sucessivas camadas

Fotolitografia por mascaras

particularidade da litografia, trata-se do processo tradicional para

impressao do layout do CI sobre a lamina de silicio. Basea-se em

mascaras para cada etapa da fabricacao

Fotolitografia por escrita direta

neste caso dispensa o conjunto de mascaras, transferindo o lay-out

de cada etapa diretamente do computador para a superficie da

lamina.

Etapa

2

Fotolitografia por mascaras

O layout contendo a representacao dos transistores,

interconexoes e demais elementos eh decomposto em uma

dezena ou mais de desenhos, as mascaras correspondentes a

cada uma etapa de fabricacao.

Este processo possibilita imprimir centenas de copias do

mesmo ou de diferentes circuitos em cada lamina, claro com

o auxilio de maquinas.

O custo de producao do conjunto de mascaras eh elevado,

sendo amortecido pela producao em massa daquele CI.

Fotolitografia por escrita direta

Neste caso dispensa o conjunto de mascaras,

transferindo o lay-out de cada etapa diretamente do

computador para a superficie da lamina.

O processo eh mais demorado

Adequado para a producao em pequena escala e

para prototipacao rapida.

Dopagem

Nesta etapa permite criar regioes condutoras atraves da

adicao de portadores p ou n a um volume de silicio.

Para haver conducao eletrica, estas impurezas devem

substituir atomos de silicio dentro da rede cristalina

A profundidade maxima do dopante raramente ultrapassa

1m

Metodos de dopagem

Dopagem por difusao (forno 1000 graus C)

Dopagem por implantacao ionica (camara de vacuo)

Etapa

3

Oxidacao

Usa-se o dioxido de silicio

composto isolante

exelentes propriedades dieletricas

resistentes a temperatura de 1200 C

usado bastante como :

isolante entre camadas

dieletrico do eletrodo de porta dos transistores

dieletrico em capacitores integrados

mascara para operacoes que dependem de temperatura

elevada.

O processo ocorre em um forno de quartzo com

temperatura entre 1000 C a 1200 C

Etapa

4

Corrosao

Trata-se de retirar seletivamente algum tipo

de material em regioes delimitadas por uma

mascara

Processos mais comuns:

Corrosao liquida (emprega liquidos reativos e

perigosos como acido fluoridrico)

Corrosao por plasma (gas inerte CF

4

sob baixa

pressao)

Etapa

5

Deposicao

Filmes finos com espessura muito pequena, formado pelos

mais diversos materiais organicos e inorganicos podem ser

depositados com precisao.

Acontece em uma camara com gas ou vapor sob pressao

reduzida com o objetivo de aumentar o percurso medio das

particulas

Processos de deposicao:

Deposicao por epitaxia

Deposicao quimica de vapor (CVD)

Evaporacao

Borrifamento

Etapa

6

Processos de deposicao

Deposicao por epitaxia

processo de acrescentar material a uma estrutura cristalina de

modo ordenado, sem solucao de continuidade. O material

depositado deve ter caracteristicas moloculares semelhantes para

poder acompanhar o plano de cristalizacao da base.

Epitaxia em fase vapor: o material faz parte de um composto

gasoso que se decompoe na superficie da lamina por estar a

uma temperatura superior a 1000 C

Epitaxia por feixe de moleculas: A operacao ocorre no alto

vacuo (menor que 10

-9

atm). Obtem-se um filme cristalino

com alta qualidade e pureza.

Epitaxia em fase liquida: processo usado para crescer o

imenso cristal de silicio dopado.

Processo ocorre a uma taxa de 0,1m/min

Processos de deposicao

Deposicao quimica de vapor

Neste processo, as moleculas vaporizadas do composto se decompoem ou

reagem na superficie da lamina, depositando o material desejado

Processo ocorre a uma taxa de 30 a 300 m/min apenas

Evaporacao

Neste processo a deposicao de metais eh feito rapidamente num baixo ponto

de fusao. Ex: aluminio

Por exemplo o aluminio, em uma camara de vacuo eh vaporizado e se

deposita livremente sobre a superficie da lamina colocada acima e

submetida a um rapido movimento orbital para uniformizar a deposicao:

Ex: metalizacao dos discos CD, CDROM, ...

processo ocorre a uma taxa de varios m/min

Crystal Growth and Wafer

Preparation

Material Preparation

Material preparation is the beginning of the

process in making an IC chip .

The goal for this part of the process is to

grow the ingot that will be sliced up into

wafers.

The wafer is a round solid silicon disc that

will have all of the processing performed on

it.

Step 1: Obtaining the Sand

The sand used to grow the wafers has to be

a very clean and good form of silicon.

For this reason not just any sand scraped off

the beach will do.

Most of the sand used for these processes is

shipped from the beaches of Australia.

Step 2: Preparing the Molten

Silicon Bath

The sand is taken and put into a pot where it

is heated to about 1600 degrees C where it

melts.

The molten sand will become the source

that will ultimately produce the raw poly-

crystalline silicon.

Raw Polysilicon

Raw polycrystalline silicon

produced by mixing refined

trichlorosilane with hydrogen

gas in a reaction furnace.

The poly-crystalline silicon is

allowed to grow on the surface

of electrically heated tantalum

hollow metal wicks

Polysilicon Ingots

The polycrystalline silicon tubes

refined by dissolving in

hydrofluoric acid producing

polysilicon ingots.

Polycrystalline silicon has

randomly oriented crystallites,

electrical characteristics not

ready for device fabrication.

Must be transformed into

single crystal silicon using

crystal pulling

Step 3: Making the Ingot

A pure silicon seed

crystal is now placed

into the molten sand

bath.

This crystal will be

pulled out slowly as it

is rotated.

The result is a pure

silicon tube that is

called an ingot

Creating the Single Crystalline Ingot

Crushed high-purity polycrystalline silicon

is doped with elements like arsenic, boron,

phosphorous or antimony and melted at

1400 in a quartz crucible surrounded by an

inert gas atmosphere of high-purity argon.

The melt is cooled to a precise temperature,

then a "seed" of single crystal silicon is

placed into the melt and slowly rotated as it

is "pulled" out.

Creating the Single Crystalline Ingot

(cont.)

The surface tension between the seed and

the molten silicon causes a small amount of

the liquid to rise with the seed and cool into

a single crystalline ingot with the same

orientation as the seed.

The ingot diameter is determined by a

combination of temperature and extraction

speed

Examples of completed ingots

Ingot Sizes

Most ingots produced

today are 150mm (6")

and 200mm (8")

diameter,

For the most current

technology 300mm

(12") and 400mm (16")

diameter ingots are

being developed.

Ingot Characterization

Single Crystal Silicon ingots are

characterized by the orientation of their

silicon crystals. Before the ingot is cut into

wafers, one or two "flats" are ground into

the diameter of the ingot to mark this

orientation.

Different flats for orientation

Each of the wafers is

given either a notch or

a flat edge

This will be used in

orienting the wafer into

the exact position for

later procedures.

<100> Lattice Orientation

This lattice

orientation is used

for MOS

(metaloxide

semiconductor),

Bi-CMOS, &

GaAs types of

chips.

Lattice Orientation

The lattice orientation refers to the organized

pattern of the silicon crystals in the wafer and

their orientation to the surface.

The orientation is obtained based on the

orientation of the crystal that is placed into the

molten silicon bath.

The different orientations have different

benefits and are used in different types of chips.

<111> Lattice Orientation

This

orientation

is used for

Bipolar

types of

chips

Step 4: Preparing the Wafers

The ingot is ground

into the correct

diameter for the

wafers.

Then it is sliced into

very thin wafers.

This is usually done

with a diamond saw.

Some wafers in storage trays

Wafer Lapping

The sliced wafers are

mechanically lapped using

a counter-rotating lapping

machine and aluminum

oxide slurry. This flattens

the wafer surfaces, makes

them parallel and reduces

mechanical defects like

saw markings

Wafer Lapping Machine

Wafer Etching

After lapping, wafers are etched in a

solution of nitric acid/ acetic acid or

sodium hydroxide to remove microscopic

cracks or surface damage created by the

lapping process.

The acid or caustic solution is removed by a

series of high-purity RO/DI water baths

Wafer polishing

Next, the wafers are polished

in a series of combination

chemical and mechanical

polish processes called CMP

The wafers are held in a hard

ceramic chuck using either

wax bond or vacuum and

buffed with a slurry of silica

powder, RO/DI water and

sodium hydroxide

Wafer Cleaning

Most wafer manufacturers use a 3-step process

which starts with an SC1 solution (ammonia,

hydrogen peroxide and RO/DI water) to remove

organic impurities and particles from the wafer

surface.

Next, natural oxides and metal impurities are

removed with hydrofluoric acid.

Finally, the SC2 solution, (hydrochloric acid and

hydrogen peroxide), causes super clean new

natural oxides to grow on the surface.

Growth of Epitaxial Silicon

The purpose of EPI growth is to create a layer with

different, usually lower, concentration of

electrically active dopant on the substrate. For

example, an n-type layer on a p-type wafer.

This layer is of a much better quality then the

slightly damaged or unclean layer of silicon in the

wafer

It is called the Epitaxial layer - where the actual

processing will be done.

An Epitaxial reactor.

Epitaxial Reactors

Overview of Wafer

Fabrication

Overview of Wafer Fabrication

Four stages of Semiconductor Manufacturing

material prep

crystal growth and wafer prep

wafer fabrication

packaging

Wafer Fabrication

the series of processes used to create the semiconductor

devices in/on the surface of the wafer

Wafer Terminology

Chip, die, microcircuit, die,bar

the identical circuits covering the wafer

Scribe lines, saw lines, streets, avenues

small areas between the chips used to separate them

Engineering die, test die

special devices or circuits containing special chemicals

to be tested during processing

Edge die

partial die patterns that will not function

Wafer Terminology (cont.)

Wafer crystal plane

the crystal structure toward which the chip edges

are oriented

Wafer Flats

the flatted edge which indicates the crystal

structure and material type

Basic Wafer Fab Operations

Layering

Patterning

Doping

Heat Treatments

Layering

Adding thin layers to the wafer surface

either insulators, conductors or semiconductors

deposited by two major techniques - growing or

deposition

Oxidation - growing a silicon dioxide layer on the

wafer surface

Deposition - common techniques are CVD

(chemical vapor deposition) Evaporation and

Sputtering.

Patterning

Series of steps resulting in removal of certain portions of

the added surface layers

After removal a pattern of the layer is left on the wafer

surface.

Material removed may be in the form of a whole or just

an island of material.

Patterning process known by names Litho, Masking,

Photolithography, Photomasking, Microlithography

Patterning is the most critical basic operation.

Patterning (cont)

Goal is to:

create circuit parts in the exact dimensions (feature size)

required by the circuit design

locate them in their precise location on the wafer

surface.

Errors in process or placement can change the

electrical functions of the device.

Contamination can introduce serious defects that

result in loss of good die.

Doping

Places specific amounts of dopant in the wafer surface

through openings in the surface layer.

Two techniques used are Ion Implantation and Thermal

Diffusion.

Thermal diffusion - chemical process that takes place

when wafer is heated to about 1000 C and exposed to

vapors of the proper dopant.

Ion Implantation - physical process in which dopant

atoms are ionized, accelerated to high speed and shot

into the wafer surface

Doping (cont)

Purpose:

create either N type or P type pockets in the

wafer surface

these pockets form the PN junctions required for

operation of the transistors, capacitors, diodes

and resistors in the circuit

Heat Treatment

Heat treatment to achieve specific results.

Annealing -

heat treatment (about 1000 C) occurring after

ion implantation to repair disruptions in the

wafer crystal structure.

Alloying -

occurs after metal conductor strips placed on

wafer. Metal alloyed (about 450 C) to wafer

surface to ensure good electrical conduction.

Semiconductor Manufacturing

Process Steps

Hundreds of steps are often required in the

wafer processing of an I.C.

The four basic operations are used

repeatedly to build the parts of the device in

and on the wafer.

Building an MOS Transistor

Circuit Design

Block diagram of the circuit

Schematic

Circuit layout - using CAD of the composite (composite

- the entire circuit including every layer)

The drawings are separated into layers and digitized

(translating to a digital database)

Final drawing completed on a computerized X-Y plotter

table

Reticles and Mask

Reticle -a hard copy of the individual drawing

recreated in a thin layer of chrome deposited on a glass

or quartz plate.

May be used directly in the photo process or used to

make a photo-mask or mask.

Masks are used to pattern a whole surface in one

pattern transfer. Masks and reticles are similar in

makeup.

Reticles and Masks are produced in a separate

department or purchased from an out side vendor.

A Mask setis supplied for each type of circuit.

Introduction to

Photolithography

n-well

p-channel transistor

p-well

n-channel transistor

p+ substrate

Introduction to Photolithography

Julian Serda

edited by Roy Stamps

Transistor Layers

Objectives

Given a multiple choice test, be able to select the

correct answer related to the following terms,

concepts and processes covered in this lesson:

wafer conditions that affect the photo process.

characteristics of wafers after completion of the

photolithography process.

differences between negative and positive

photolithography processes.

ten basic steps of the photomasking process.

basic features of each of the ten steps of the

photomasking process.

Terms and Concepts to be

Covered in this Lesson

photolithography

microlithography

dehydration bake

hydrophobic

hexamethyldisilazine

HMDS

photoresist

exposure

linewidth resolution

overlay accuracy

positive lithography

negative lithography

windows & islands

adhesion

film thickness

light absorbance

uniformity

develop

etch & strip

Photolithography -- Definitions

Photolithography is used to produce 3-D

images using light sensitive photoresist and

controlled exposure to light.

Microlithography is the technique

used to print ultra-miniature

patterns -- used primarily in the

semiconductor industry.

Photolithography is at the Center of

the Wafer Fabrication Process

* 4

Thin Films

Implant

Diffusion

Etch

Test/Sort

Polish

Photo

Patterned

wafer

What else is Photolithography?

3-dimensional circuit patterning

Most critical step in IC process

Determines feature resolution

Determines overlay accuracy

Bottleneck in the fab process

The leading technology

Other Terms used to Describe

Photolithography

masking

photomasking

photo

lithography

litho

yellow room

dark room

Wafer Conditions Prior to Patterning

Surface conditions include:

film composition, e.g.: silicon, nitride, polysilicon,

metal, etc.

bare surface vs. patterned surface

surface reflectivity

Surface conditions may affect

photoresist-to-wafer adhesion

alignment accuracy

linewidth resolution

exposure settings

bake time

Wafer Conditions after

Photolithography

resist coated wafer

patterned resist layer

withstands etching process

withstands ion implanting

quality measures

linewidth resolution

overlay accuracy

particles & defects

Importance of Resolution and

Overlay Registration

Top view of Transistor

V

DD V

SS

V

out

V

in

g

g

s d

s d

contact

Cross-section of Transistor

n-channel

transistor

p-channel

transistor

p-well

n+ p+ n+

p+

n-substrate

source

drain source

drain

field oxide

gate oxide

metal