Академический Документы

Профессиональный Документы

Культура Документы

78 LM 12

Загружено:

sergey0 оценок0% нашли этот документ полезным (0 голосов)

124 просмотров2 страницы78lm12

Оригинальное название

78lm12

Авторское право

© © All Rights Reserved

Доступные форматы

PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документ78lm12

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

124 просмотров2 страницы78 LM 12

Загружено:

sergey78lm12

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 2

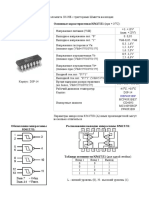

Микросхема

К561ЛН2, К564ЛН2, К176ЛН2, К561ЛН2.

Микросхема К561ЛН2 содержит 6 буферных (усиленных) инверторов стандартной КМОП логики.

Основные характеристики К561ЛН2 (при +25oC):

Напряжение питания Uпит +3..+18V

Параметры при Uпит +5V +10V +15V

Ток потребления (статический) < 2µA

Мощность потребления 0,4 мкВт/вентиль

Выходное напряжение лог. "0", не более 0,95V 2,9V

Выходное напряжение лог. "1", не менее 3,6V 7,2V

Входное напряжение лог. "0", не более 1,5V 3V 4V

Входное напряжение лог. "1", не менее 3,5V 7V 11V

Время задержки 50нс (типовое)

Входной ток лог. «0»/«1» < 0,1uA

Выходной ток лог. «0»/«1» 1,25mA 1,25mA

Время нарастания 0/1 <120nS <90nS

Время спада 1/0 <110nS <50nS

Рабочий диапазон температур -40oC..+85oC

Корпус DIP-14

Аналог по характеристикам "CD4049"

Аналог по выводам "CD4069"

Расположение выводов микросхемы К561ЛН2:

Внутренняя схема одного инвертора

Микросхема К561ЛН2 по входным и выходным уровням сигналов совместима с другими

ИС стандартной КМОП логики серии 40xx/К561,

а при напряжении питания 5 вольт также с ИС ТТЛ логики.

Выходы микросхемы К561ЛН2 допускают нагрузку на два ТТЛ входа серии 74/К155.

Корпус: DIP-14

№ выв. Назначение № выв. Назначение

1 Вход 8 Выход

2 Выход 9 Вход

3 Вход 10 Выход

4 Выход 11 Вход

5 Вход 12 Выход

6 Выход 13 Вход

7 Общий 14 Ucc

Тип микросхемы К561ЛН2

Т.С. -10..+70

Vdd min...Vdd max,В -0.5...+18

Pd,MBT 300

Напр.сиг. A-Q

ViI(Vnl),B при Vdd=5B 1

Vih(Vnh),B при Vdd=5B 4

Icc,mkA при Vdd=5B <0.25

TpHL tip. нс при Vdd=5B 45

TpLH tip,нс при Vdd=5B 45

TpHL тах,нс при Vdd=5B 32

TpLH max,HC при Vdd=5B 32

Vil(Vnl),B при Vdd=10B 2

Vih(Vnh),B при Vdd=10B 8

Icc,мкA при Vdd=10B <0.5

TpHLtip,нс при Vdd=10B 23

TpLH tip,нс при Vdd=10B 23

TpHL max,нс при Vdd=10B 16

TpLH max,нс при Vdd=10B 16

Vil(Vnl),B при Vdd=15B 2.5

Vih(Vnh),B при Vdd=15B 12.5

Icc,mkA при Vdd=15B <1

TpHL tip, нс при Vdd=15B 18

TpLH tip, нс при Vdd=15B 18

TpHL max.нс при Vdd=15B 13

TpLH max, нс при Vdd=15B 13

Вам также может понравиться

- K561TL1Документ2 страницыK561TL1essen999Оценок пока нет

- 939Документ2 страницы939qwer tootОценок пока нет

- КР1534ПП3 4Документ6 страницКР1534ПП3 4Sergos88Оценок пока нет

- DS3231Документ3 страницыDS3231Jhonatan Lima BuzzОценок пока нет

- K 1055 HP 2Документ6 страницK 1055 HP 2Thanh Pham TuanОценок пока нет

- KР590KН2Документ1 страницаKР590KН2Ramazan ÖzenОценок пока нет

- 1230 DPXXДокумент11 страниц1230 DPXXYoandy PerezОценок пока нет

- K561TM2 EtcДокумент1 страницаK561TM2 EtcMike BrdnОценок пока нет

- RS 3 2010 60-62Документ2 страницыRS 3 2010 60-62chefchelios50822Оценок пока нет

- ANSI code 18 Tип EPN-110DN: uni-lineДокумент2 страницыANSI code 18 Tип EPN-110DN: uni-linetechniciandpaОценок пока нет

- ЖК телевизоры (168 224)Документ57 страницЖК телевизоры (168 224)александрОценок пока нет

- Map 3222Документ4 страницыMap 3222Ioan TivgaОценок пока нет

- 1210 элементыДокумент5 страниц1210 элементы1vasilisk12Оценок пока нет

- Назначние Выводов Микросхемы КР1534ПП1Документ5 страницНазначние Выводов Микросхемы КР1534ПП1Evgeniy Andreevich FrolovОценок пока нет

- SR3B261BD DocumentДокумент8 страницSR3B261BD DocumentИван КолодинОценок пока нет

- 210 Manual 326 BДокумент28 страниц210 Manual 326 BАлексей ХоролецОценок пока нет

- s2000 sp4 220 Et v.1.12 Jul 18Документ8 страницs2000 sp4 220 Et v.1.12 Jul 18azat OrazowОценок пока нет

- 564кт3Документ2 страницы564кт3영민Оценок пока нет

- EG8030 Datasheet RusДокумент20 страницEG8030 Datasheet RusRoby Jack100% (1)

- 134 TV 14Документ4 страницы134 TV 14truongpx1993Оценок пока нет

- 564 La 9Документ2 страницы564 La 9Влад ГорОценок пока нет

- 597 Ca 3Документ7 страниц597 Ca 3영민Оценок пока нет

- EG8030 Datasheet RusДокумент20 страницEG8030 Datasheet RusАлександр ПоповОценок пока нет

- Prezentatsia Po Podstantsiam KUB 25 Ot GK EnergiaДокумент17 страницPrezentatsia Po Podstantsiam KUB 25 Ot GK EnergiaАлексей СемёновОценок пока нет

- Instruktsia IDS Drive ZДокумент23 страницыInstruktsia IDS Drive ZSam VinchesterОценок пока нет

- Operating Instructions Electronic Pressure Sensor: PNI02xДокумент25 страницOperating Instructions Electronic Pressure Sensor: PNI02xErick Portela cruzОценок пока нет

- IL4558RДокумент6 страницIL4558RAleksandr LiubchenkoОценок пока нет

- K 1055 HP 2 RДокумент13 страницK 1055 HP 2 RRebecca RiversОценок пока нет

- Косой настройкаДокумент17 страницКосой настройкаRedОценок пока нет

- K140ud8 PDFДокумент2 страницыK140ud8 PDFdenitoОценок пока нет

- K140ud8 PDFДокумент2 страницыK140ud8 PDFDennys EstradaОценок пока нет

- K140ud8 PDFДокумент2 страницыK140ud8 PDFDennys EstradaОценок пока нет

- K140ud8 PDFДокумент2 страницыK140ud8 PDFDennys EstradaОценок пока нет

- Zelio Logic - SR2E201BDДокумент3 страницыZelio Logic - SR2E201BDВладимир УсковОценок пока нет

- КР1114ЕУ4 (TL494, IR3M02, μA494, КА7500, МВ3759)Документ3 страницыКР1114ЕУ4 (TL494, IR3M02, μA494, КА7500, МВ3759)drusja85Оценок пока нет

- PT2322 DatasheetДокумент10 страницPT2322 Datasheetswap2gzОценок пока нет

- PCAT200Документ3 страницыPCAT200steven.seagalОценок пока нет

- Info 21Документ18 страницInfo 21Is LifeОценок пока нет

- Тема 2.1. Управление светодиодамиДокумент38 страницТема 2.1. Управление светодиодамиMaffinОценок пока нет

- 6EP19612BA21 Datasheet RuДокумент2 страницы6EP19612BA21 Datasheet RuНиколай НиколенкоОценок пока нет

- DS1307Документ2 страницыDS1307Jhonatan Lima BuzzОценок пока нет

- KR140 UD70843 RДокумент1 страницаKR140 UD70843 RKr4iZenОценок пока нет

- ЧастотомерДокумент33 страницыЧастотомерGordiiejikОценок пока нет

- IDS-Drive ZДокумент23 страницыIDS-Drive ZАлександрОценок пока нет

- QD0056C DatasheetДокумент2 страницыQD0056C DatasheetMassimo PerseoОценок пока нет

- ООО компания "Электроника и Связь" +7 (473) 277-14-34, 277-35-34Документ2 страницыООО компания "Электроника и Связь" +7 (473) 277-14-34, 277-35-34yamaxiОценок пока нет

- 12 p59-60Документ2 страницы12 p59-60Emilian Angelov AngelovОценок пока нет

- ООО компания "Электроника и Связь" +7 (473) 277-14-34, 277-35-34Документ3 страницыООО компания "Электроника и Связь" +7 (473) 277-14-34, 277-35-34Abdurashid tillaevОценок пока нет

- ETP48100-B1-50A описание на русскомДокумент1 страницаETP48100-B1-50A описание на русскомAlexander PischulinОценок пока нет

- ILE4267r 0Документ8 страницILE4267r 0Олег ПетровскийОценок пока нет

- Изучите технологию ремонта цветного телевизора с нуля (267-289)Документ23 страницыИзучите технологию ремонта цветного телевизора с нуля (267-289)александрОценок пока нет

- 174УН4АДокумент3 страницы174УН4ААлександрОценок пока нет

- Svetotexnika 2016 PDFДокумент37 страницSvetotexnika 2016 PDFBouazza AllitiОценок пока нет

- LPG899Документ6 страницLPG899Prof. Arturo GilsonОценок пока нет

- Источник бесперебойного питания KR1000LCD (L) KR2000LCD (L) KR3000LCD (L)Документ14 страницИсточник бесперебойного питания KR1000LCD (L) KR2000LCD (L) KR3000LCD (L)Sandy Gitu LohОценок пока нет

- KR 537 Ru 10Документ3 страницыKR 537 Ru 10Василь ЛопушанськийОценок пока нет

- ReleДокумент24 страницыRelevilemmarkovОценок пока нет

- URC101Документ17 страницURC101sergeyОценок пока нет

- Unic Urv340 PDFДокумент120 страницUnic Urv340 PDFsergeyОценок пока нет

- 1 - Прайс 22.06.2020Документ336 страниц1 - Прайс 22.06.2020sergey50% (2)

- Rele 75Документ4 страницыRele 75sergeyОценок пока нет

- Wiring DiagramsДокумент104 страницыWiring Diagramssergey100% (2)

- техинформДокумент160 страництехинформsergeyОценок пока нет

- BC 327Документ110 страницBC 327sergeyОценок пока нет

- Chrysler 300c Dodge Magnum 2004 ArusДокумент374 страницыChrysler 300c Dodge Magnum 2004 Arussergey100% (1)

- 78 LM 12Документ2 страницы78 LM 12sergeyОценок пока нет

- Instrukzia Po AbsДокумент53 страницыInstrukzia Po AbssergeyОценок пока нет

- O Cat325sДокумент248 страницO Cat325ssergeyОценок пока нет

- Фалалеев С.В. Конструкция PDFДокумент246 страницФалалеев С.В. Конструкция PDFXavier AverosОценок пока нет

- 5 - 1 - Операционная Система-РУС 2021 - 1 КисмДокумент23 страницы5 - 1 - Операционная Система-РУС 2021 - 1 КисмUlugbek HamroevОценок пока нет

- Разработка интерактивных систем на OpenFrameworksДокумент43 страницыРазработка интерактивных систем на OpenFrameworksДенис ПереваловОценок пока нет

- ПРЕЗЕНТАЦИЯДокумент11 страницПРЕЗЕНТАЦИЯIlya PolidovetsОценок пока нет

- Илон Маск. В погоне за мечтойДокумент178 страницИлон Маск. В погоне за мечтойHolly.BezhОценок пока нет

- Инструкция Как Выставить Фактуру и Добавить ОплатуДокумент8 страницИнструкция Как Выставить Фактуру и Добавить ОплатуiskorostenskynikolayОценок пока нет